50%——在品控界是個很可怕的數字,有一對兄弟難題占到了產線不良率的一半江山。

在電子器件組裝過程中,EOS(Electrical Over Stress)與 ESD(Electrical Static Discharge)造成的集成電路失效約占現場失效器件總數的50%,且通常伴隨較高不良率以及潛在可靠性問題,是產線一大殺手。

當問題發生時,應該如何查找真因、尋找解決方案,一直以來都是困擾現場工程師、品控工程師的難題。廣電計量集成電路失效分析實驗室,通過多年的行業積累,總結出一套相對完整的針對EOS/ESD的分析方法,通過失效分析、模擬驗證等手段,可以更好地協助現場工程師與設計工程師提升產線良率及IC的可靠性。

常見問題1:產線失效到底是由EOS還是ESD引起?

我們在做失效分析時,最常聽到客戶的要求是希望知道rootcause是EOS還是ESD,確認失效機理及真因,是改善良率的第一步,也是非常關鍵的一步。通常,我們區分EOS還是ESD會首先通過失效分析手法挖掘IC的物理失效現象,然后從現象上去區分。

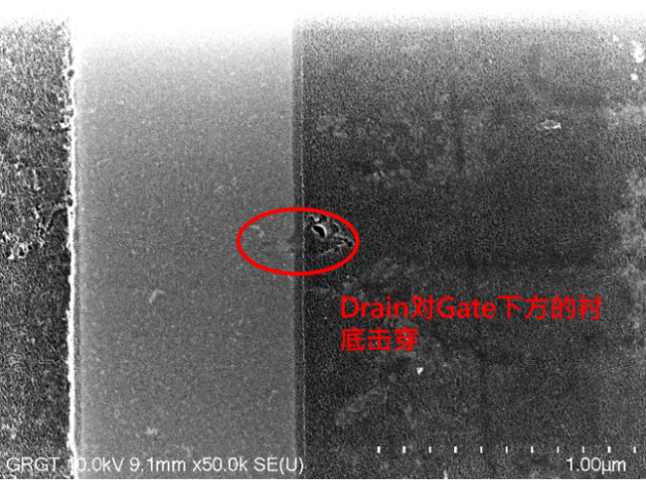

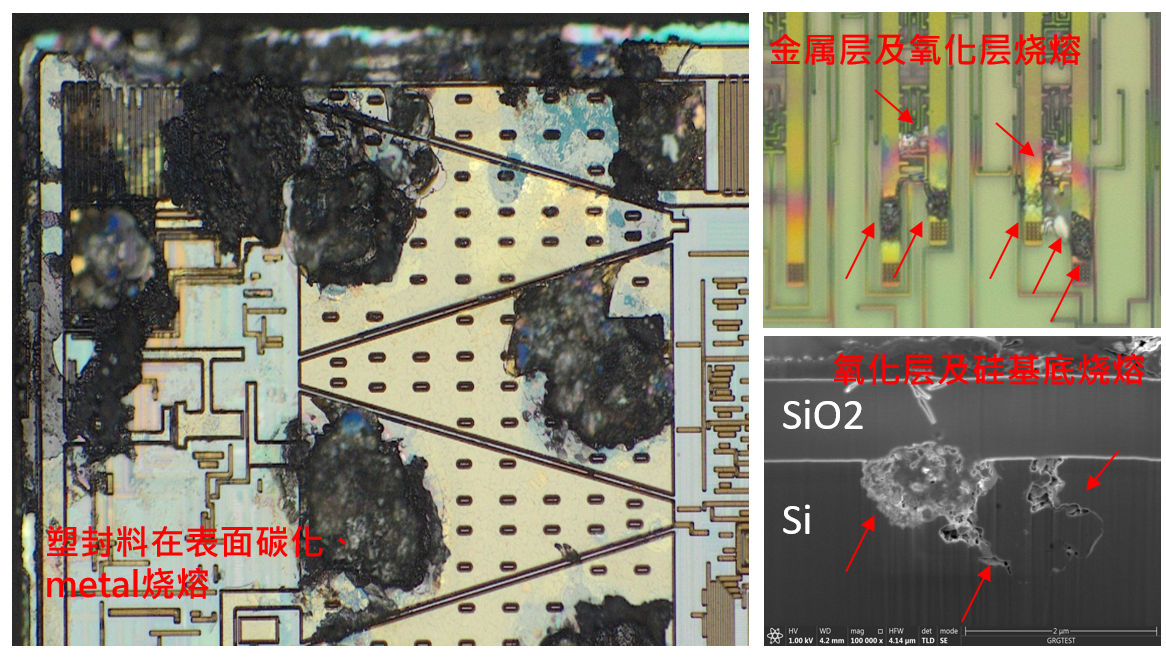

常見ESD物理失效表現:襯底擊穿、多晶硅熔融、GOXpin hole、contactmelted、metal melted等(見圖1),常見EOS物理失效表現:氧化層、金屬層大面積熔融以及封裝體碳化等現象(見圖2)。

圖1:常見ESD物理失效現象

圖2:常見EOS物理失效現象

常見問題2:為什么EOS和ESD會造成不同的失效現象?

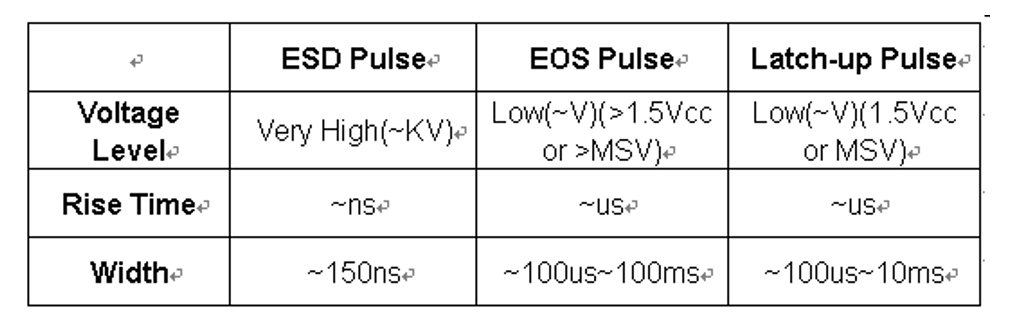

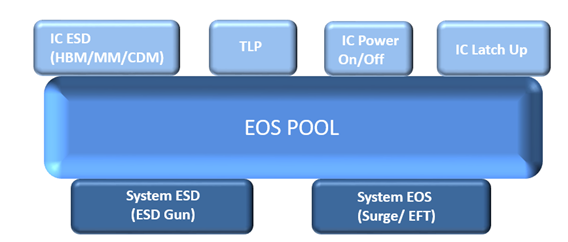

ESD從廣義上屬于EOS的一種,但是現場應用中我們通常把ESD單獨歸類,除此之外的過電應力統歸于EOS。EOS 是指長時間(幾微秒到幾秒)持續的過壓或大電流造成的局部過熱導致的失效,其電壓、電流相對ESD較低,但是持續時間長能量更高,經常有同一功能區塊多處大面積的burnout現象。ESD 單指在靜電放電過程中瞬間高電壓(通常在幾千或上萬伏特)大電流(1~10A)狀態下引發的失效現象,主要特征為放電時間極短(1~100ns),因此一般呈現為輕微的點狀失效。

表1:EOS/ESD信號特征

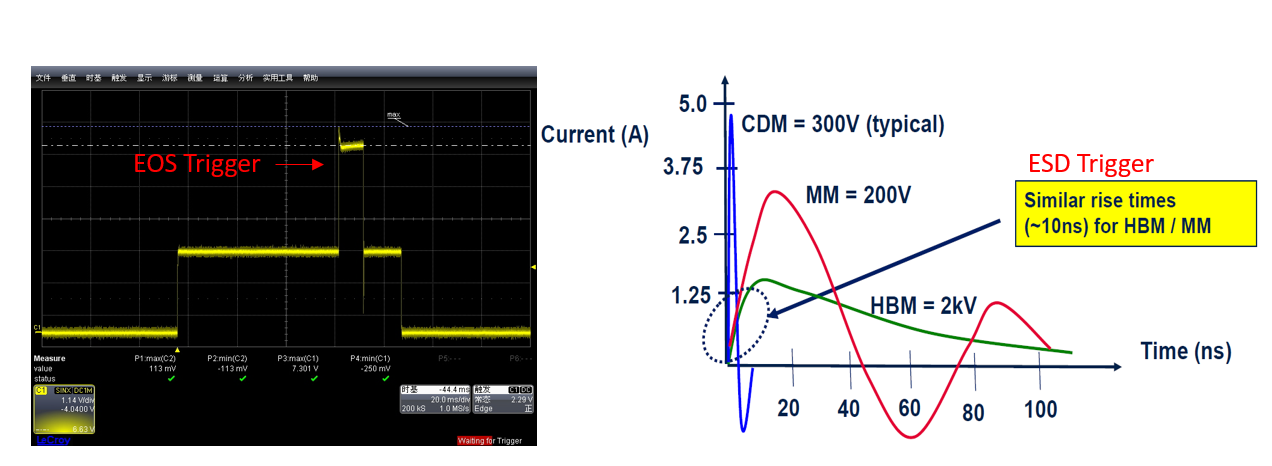

圖3:EOS/ESD脈沖波形

綜合以上,由于EOS信號相對ESD信號持續時間長,能量更強,所以通常會造成芯片大面積的burnout現象,這是EOS不同于ESD現象的主要特征。

常見問題3:什么情況下無法區分EOS/ESD?

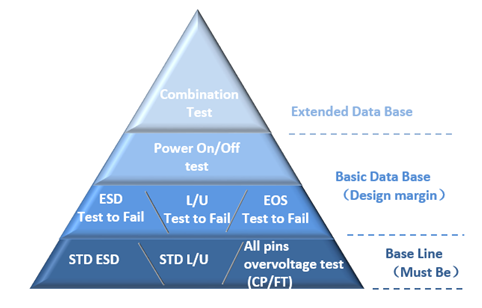

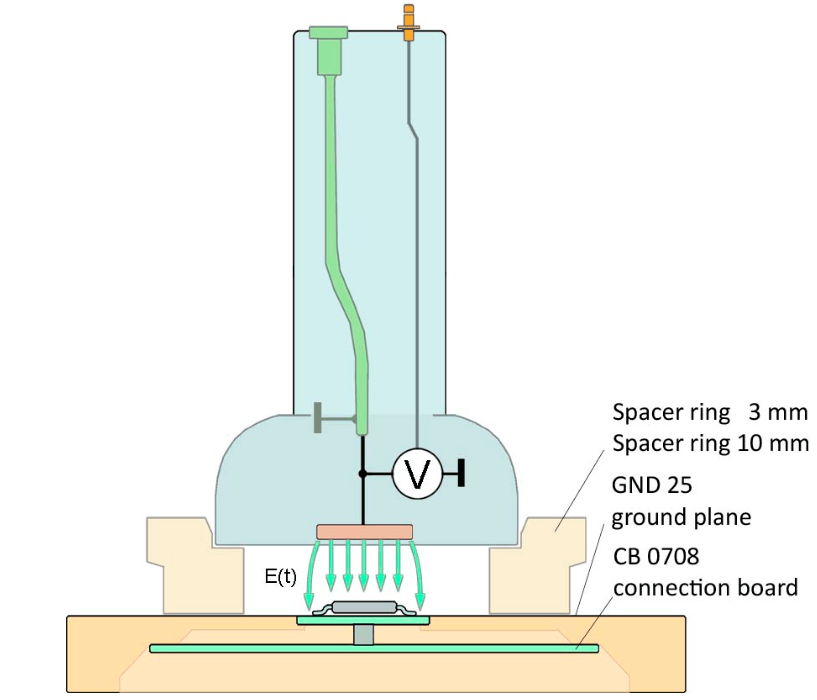

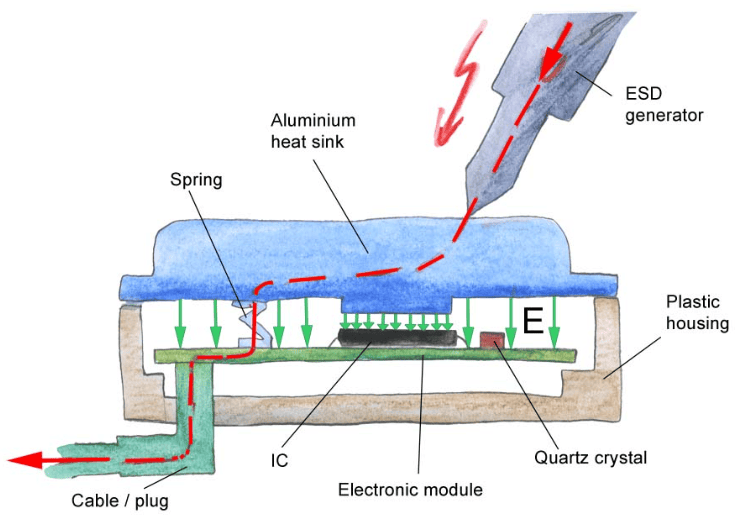

一種情況是短脈沖EOS(持續時間幾個微秒)與ESD的物理損傷十分相似,比如只造成很小面積的金屬熔融,這種情況就很難區分是EOS還是ESD的能量造成。另一種情況是IC先經過了ESD損傷,在后續功能驗證時大漏電流誘發了burnout現象,使得IC表面同時存在EOS和ESD的物理失效特征,尤其常見于PAD旁邊的IO buffer線路上,這種情況下單從物理失效現象是無法判斷初始失效是否由ESD導致。當遇到EOS/ESD無法區分的情況,需要通過模擬實驗進一步驗證,對IC或系統使用不同模型進行EOS/ESD模擬測試(見圖4)testto fail,并針對失效IC進行分析。通過對比驗證批芯片與實際失效芯片的物理失效現象(失效線路位置及失效發生的物理深度),不僅可以用來歸納真因,還可以了解IC或系統在不同條件下的耐受等級,從而進一步指導優化產線防護或IC的可靠性設計。針對新投產芯片也可以考慮從多維度進行EOS/ESD的驗證與分析(見圖5),不斷提升IC的可靠性品質。

圖4:IC常見EOS模擬驗證方式

圖5:IC常見EOS/ESD測試項目

綜上所述,當產線發生EOS/ESD失效時,應該從哪些方面進行分析及改良?我們通常建議客戶參考以下流程進行:

1. 針對失效IC進行電性及物理失效分析,確認其物理失效現象(失效點對應的電路位置及失效的物理深度),配合現場失效信息收集,初步推斷EOS/ESD失效模型;

2.針對EOS/ESD無法判斷的情況,對相關IC或系統進行EOS/ESD模擬試驗,驗證其電壓、電流耐受等級,并針對失效芯片執行失效分析,對比實際失效狀況,歸納真因及梳理改善方向;

3.探測現場容易發生EOS/ESD的位置(例如使用ESD Event Detector或高頻示波器),針對產線應用進行改良。

表2:IC常見EOS/ESD失效來源

生產人員/設備/環境的ESD防護不佳 | 使用易感應靜電的材料 |

模塊測試開關引起的瞬態/毛刺/短時脈沖波形干擾 | 熱插拔引發的瞬間電壓、電流脈沖 |

電源供應器缺少過電保護裝置及噪聲濾波裝置 | 提供超過組件可操作的工作電源 |

接地點反跳(接地點不足導致電流快速轉換引起高電壓) | 過多過強的ESD事件引發EOS |

其他設備的脈沖信號干擾 | 不正確的上電順序 |

廣電計量集成電路失效分析實驗室,配備完善的EOS/ESD/RA等測試設備及完整的失效分析手法,擁有經驗豐富的材料及電性能可靠性專家,可以針對IC進行全方位的失效分析及可靠性驗證方案的設計與執行。

-

ESD

+關注

關注

50文章

2291瀏覽量

175739 -

DRAM

+關注

關注

40文章

2348瀏覽量

185606 -

EOS

+關注

關注

0文章

131瀏覽量

21616

發布評論請先 登錄

【干貨】ESD如何選型

中國集成電路大全 接口集成電路

ESD與EOS資料整理

集成電路為什么要封膠?

集成電路電磁兼容性及應對措施相關分析(三)集成電路ESD 測試與分析

集成電路電磁兼容性及應對措施相關分析(三)—集成電路ESD 測試與分析

集成電路電磁兼容性及應對措施相關分析(一) 電子系統性能要求與ESD問題

集成電路電磁兼容性及應對措施相關分析(一) — 電子系統性能要求與ESD問題

干貨|集成電路EOS/ESD,如何把控?

干貨|集成電路EOS/ESD,如何把控?

評論