概述

AD9551接受一個或兩個參考輸入信號,然后由這些信號產生一個或兩個輸出信號。這兩個輸出信號的頻率為諧波相關的,可編程因子為1至63。AD9551能將參考頻率轉換成需要的輸出頻率。輸入接收器和輸出驅動器同時具備單端和差分工作模式。

數據表:*附件:AD9551多業務時鐘發生器技術手冊.pdf

參考調節和轉換電路在內部使兩個參考同步,以便一個參考失效時,輸出端實際上不出現相位擾動現象。

AD9551采用一個26 MHz外部晶體(標稱值)和內部DCXO來提供保持模式工作。如果兩個參考都失效了,該器件會維持一個穩定的輸出信號。

小數N分頻PLL可實現超精細的輸出頻率調諧精度。所有目前定義的網絡標準(包括前向糾錯率)都可能實現(假設采用一個26 MHz的晶體)。

AD9551具備引腳可選的預置分頻器值,從而提供頻比分類。由于具備對大多數所需頻比進行編程的能力,因此SPI接口擁有更多靈活性。

應用

特性

- 任意兩個標準網絡速率之間轉換

- 雙路參考輸入和雙路時鐘輸出

- 引腳可編程(標準網絡速率轉換)

- SPI可編程(任意合理速率轉換)

- 輸出頻率范圍:10 MHz至777.6 MHz

- 輸入頻率范圍:19.44 MHz至806 MHz

- 片上VCO

- 欲了解更多特性,請參考數據手冊

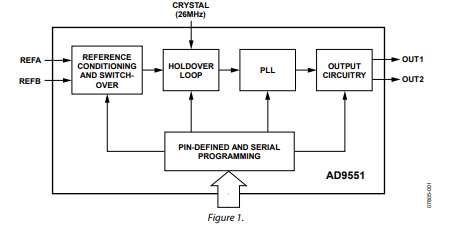

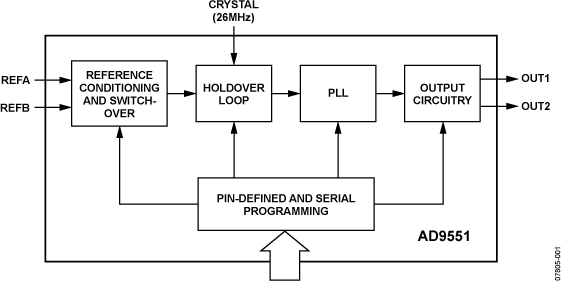

框圖

AD9551可通過外部控制引腳(A[3:0]、B[3:0]和Y[3:0])輕松配置。這些引腳的邏輯狀態設置預定義的分頻器值,以建立特定的輸入 - 輸出頻率比。對于需要不同頻率比的應用,用戶可通過串行端口覆蓋任何預配置的設置,從而啟用各種廣泛的應用。

AD9551架構由兩個級聯的PLL級組成。第一級由分數分頻(通過Σ - Δ調制)組成,隨后是一個基于晶體諧振器的DCXO數字PLL。DCXO使用外部晶體,頻率范圍為19.44 MHz至52 MHz。DCXO構成第一個PLL,在較窄的頻率范圍(±50 ppm)內圍繞晶體諧振器頻率工作。這個PLL的環路帶寬約為180 Hz,提供初始的抖動凈化輸入參考信號。第二級是一個頻率乘法PLL,將19.44 MHz至52 MHz的輸入頻率(在104 MHz的范圍內)轉換為約3.7 GHz。這個PLL采用基于Σ - Δ調制的分數反饋分頻器,實現分數頻率乘法。第二個PLL輸出端的可編程整數分頻器將最終輸出頻率設置為高達900 MHz。

理解AD9551的一個重要方面是,其產生的輸出頻率很可能與輸入參考頻率不一致。原因是輸入和晶體頻率通常不是諧波相關的,因此輸出和晶體頻率之間沒有固定關系。因此,輸入和輸出信號之間的相位關系一般是不斷變化的。

AD9551包含參考信號處理模塊,可在兩個參考輸入之間實現平滑的切換過渡。該電路會自動檢測參考輸入信號的存在。如果只有一個輸入存在,器件將其用作有效參考。如果兩個輸入都存在,一個將成為有效參考,另一個將成為備用參考。該電路與備用參考的有效參考邊緣對齊。如果有效參考失效,電路會自動切換到備用參考(如果可用),使其成為新的有效參考。同時,失效的參考一旦再次可用,將成為新的備用參考,并與新的有效參考邊緣對齊(防止故障再次發生的預防措施)。

如果無法使用備用參考,AD9551支持保持模式。請注意,外部晶體對于切換器和保持功能至關重要。它也是參考同步和監測功能的時鐘源。

AD9551使用單個外部電容作為輸出PLL環路濾波器。憑借適當的端接,輸出可兼容LVPECL、LVDS或CMOS邏輯電平,盡管AD9551是嚴格在CMOS工藝中實現的。

AD9551可在 -40°C至 +85°C的擴展工業溫度范圍內運行。

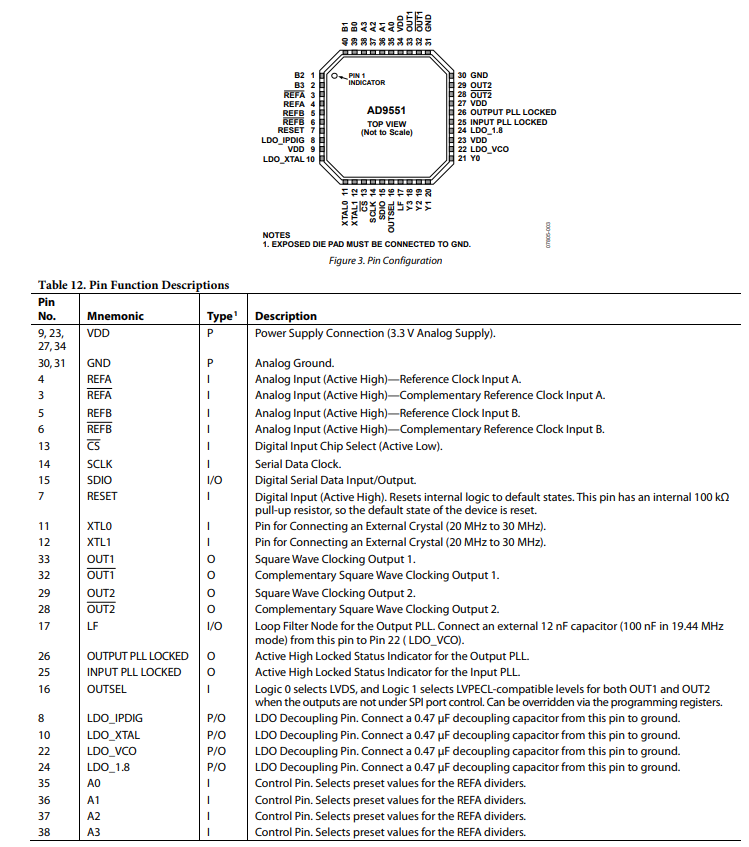

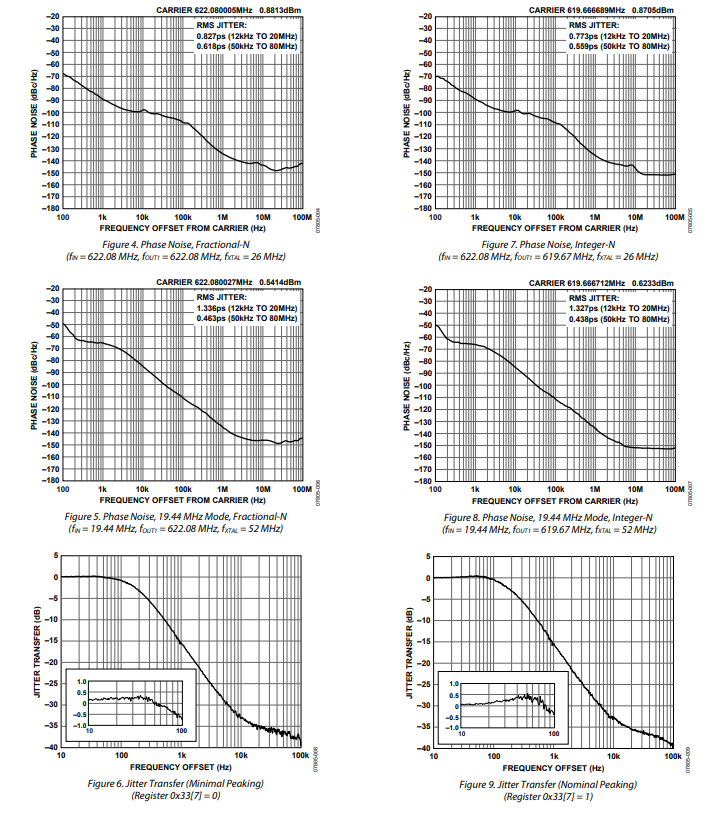

引腳配置描述

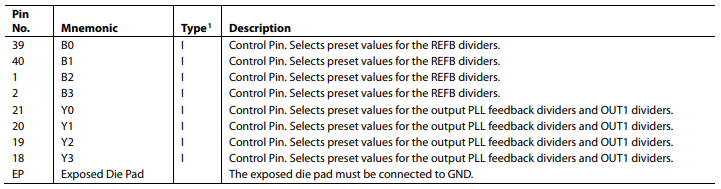

典型性能特征

-

接收器

+關注

關注

15文章

2563瀏覽量

73411 -

pll

+關注

關注

6文章

884瀏覽量

136055 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68889

發布評論請先 登錄

AD9551,pdf datasheet (Multiser

AD9551 多業務時鐘發生器

AD9551多業務時鐘發生器技術手冊

AD9551多業務時鐘發生器技術手冊

評論