點(diǎn)擊藍(lán)字關(guān)注我們

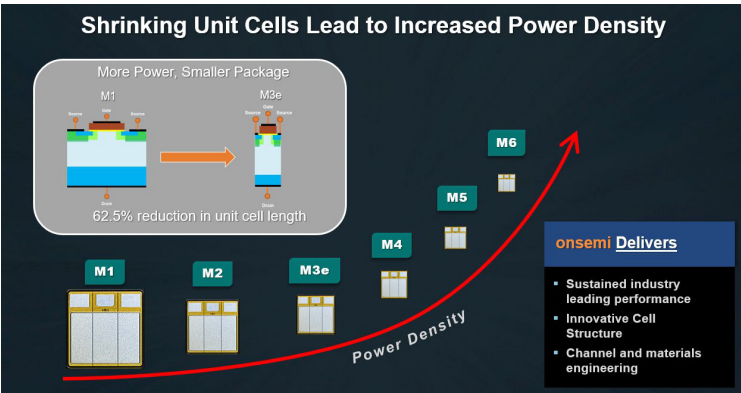

SiC MOSFET 在功率半導(dǎo)體市場中正迅速普及,因?yàn)樗畛醯囊恍┛煽啃詥栴}已得到解決,并且價位已達(dá)到非常有吸引力的水平。隨著市場上的器件越來越多,必須了解 SiC MOSFET 與 IGBT 之間的共性和差異,以便用戶充分利用每種器件。本系列文章將概述安森美 M 1 1200 V SiC MOSFET 的關(guān)鍵特性及驅(qū)動條件對它的影響,作為安森美提供的全方位寬禁帶生態(tài)系統(tǒng)的一部分,還將提供NCP51705(用于 SiC MOSFET 的隔離柵極驅(qū)動器)的使用指南。本文為第二部分,將重點(diǎn)介紹安森美M 1 1200 V SiC MOSFET的動態(tài)特性。

原版文檔獲取點(diǎn)擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領(lǐng)取原版文檔哦~

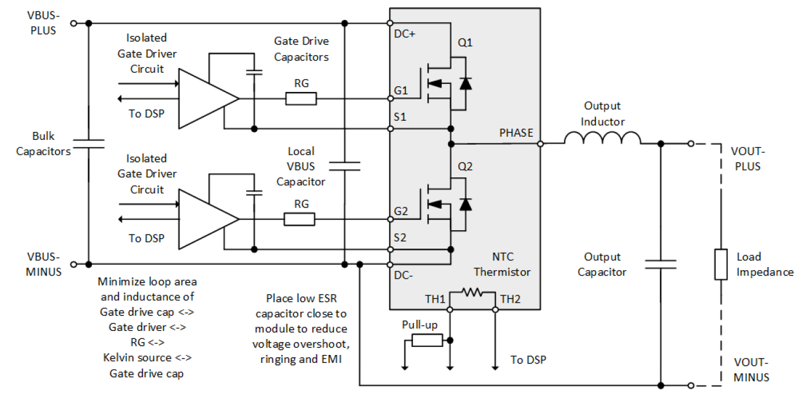

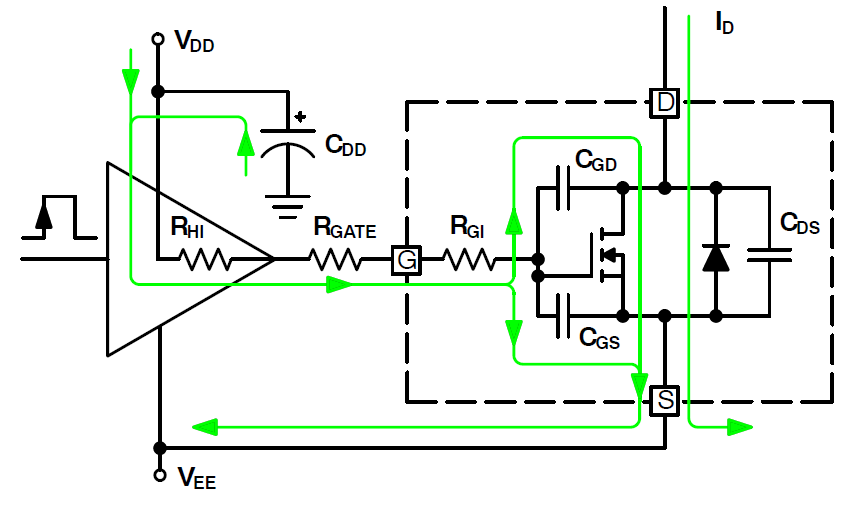

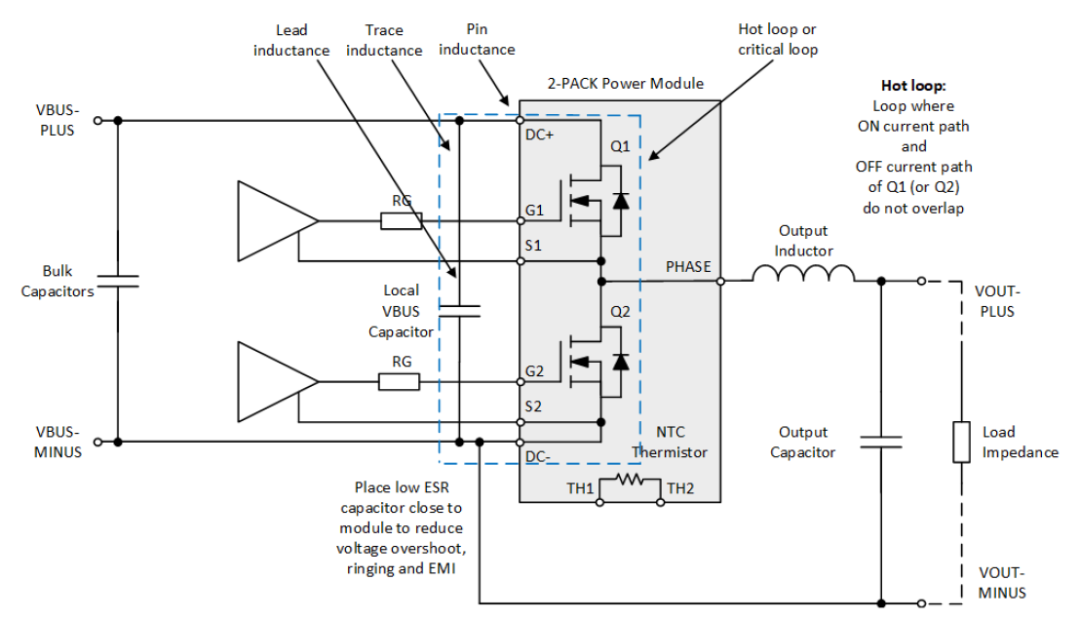

為了表征安森美 M 1 SiC MOSFET 的動態(tài)特性,使用了一個 20 m 的半橋模塊,其中兩個 40 m 器件并聯(lián)。圖 10 說明了測試設(shè)置。

圖 10:動態(tài)特性測試設(shè)置框圖

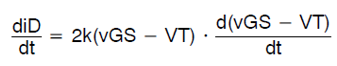

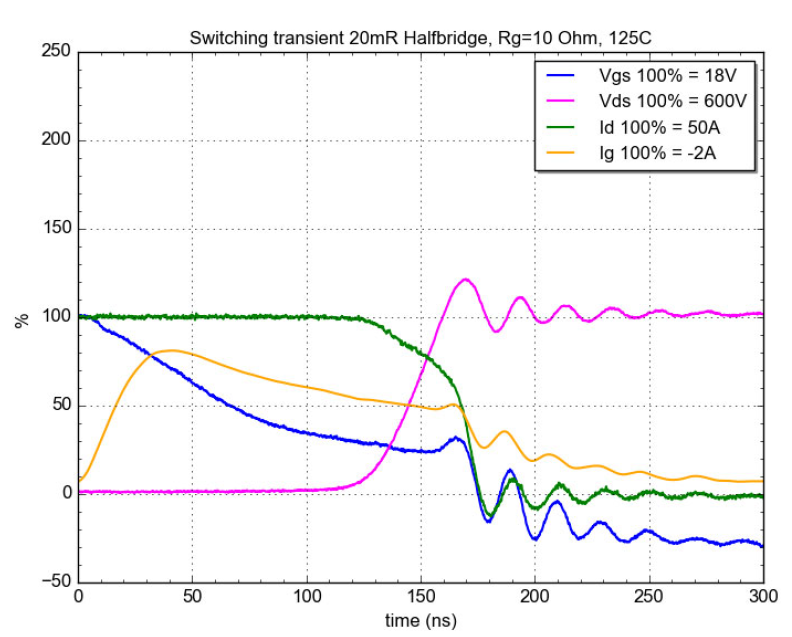

圖 11 顯示了上述測試設(shè)備的導(dǎo)通波形。品紅色曲線是低壓側(cè) MOSFET 的漏電壓。綠色曲線是通過低壓側(cè) MOSFET 的電流。

如果柵極驅(qū)動器在時間 t = 0 時被切換到 18 V,則切換序列開始。在初始緩升之后,柵極驅(qū)動電流起步很高,并隨著柵極電壓的增加而減小。柵極電壓升高,直至達(dá)到閾值電壓。電流增加,直至達(dá)到流過二極管的電流:負(fù)載電流+反向恢復(fù)電流+電容電流。

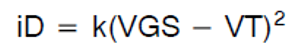

SiC MOSFET 的臺階電壓高度依賴于負(fù)載電流。在圖 11 中,臺階電壓約為 10 V。給定 ID 的 VGS 由以下公式得出。

因此,坡度將隨時間變化如下:

當(dāng)柵極電壓隨時間呈近似線性變化時,di/dt 隨時間呈線性變化。由di/dt 隨時間呈線性下降引起的 Vds 壓降從電流達(dá)到閾值電壓時開始,到達(dá)到電流峰值時結(jié)束。

柵極電流和電壓達(dá)到臺階電壓。柵極電流為 QGD 充電,并且漏電壓降低到幾乎為零。

漏極電流向負(fù)載電流下降,并伴有一些振鈴。

最后,柵極電壓升高至 18 V。漏電壓降低至負(fù)載電流乘以 18 V 時的 RDS(ON)。

圖 11:20 mohm、1200 V 半橋模塊的導(dǎo)通波形

圖 12:SiC MOSFET 源極電流

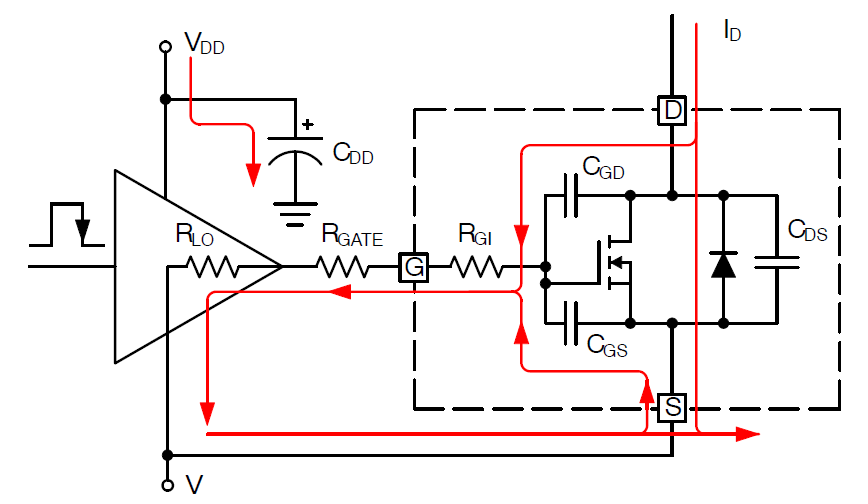

圖 13 顯示了使用兩個 40 mohm 器件的 20 mohm、1200 V 半橋模塊的關(guān)斷波形。

如果柵極驅(qū)動器在時間 t = 0 時被切換到 -5 V,則開關(guān)序列開始。在初始緩升之后,柵極驅(qū)動漏極電流起步很高,并隨著柵極電壓的增加而減小。柵極電壓下降,直至達(dá)到臺階電壓。由于沒有反向恢復(fù)電流,臺階電壓低于導(dǎo)通期間的電壓。QGD 放電時,電壓升高。一些漏極電流用于給非線性 COSS 電容放電,其在漏極電流中表現(xiàn)為負(fù)斜率。

柵極電壓過沖由電路中的回路電感引起:離直流總線最近的電容–模塊的直流+觸點(diǎn)–模塊的直流?觸點(diǎn)–回到直流總線電容。模塊和電容之間的連接應(yīng)盡可能低電感,以最大限度地降低振鈴電壓。

當(dāng)達(dá)到峰值電壓時,柵極驅(qū)動器將柵極從臺階電壓放電至閾值電壓,使電流降至零。柵極驅(qū)動器繼續(xù)給柵極放電,直至達(dá)到 ?5 V。

圖 13:20 mohm、1200 V 半橋模塊的關(guān)斷波形

圖 14:SiC MOSFET 漏極電流

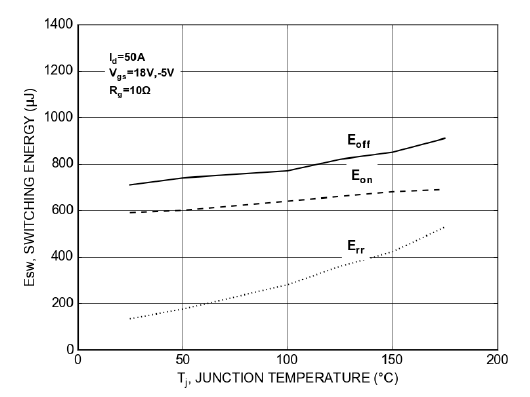

開關(guān)損耗隨溫度增加

開關(guān)損耗隨溫度增加與靜態(tài)特性一樣,SiC MOSFET 的工作溫度將對開關(guān)性能產(chǎn)生影響。不過,如圖 15 所示,EON 和 EOFF 的溫度系數(shù)幾乎相同,150℃ 時的開關(guān)性能將非常接近 25℃ 時的特性。反向恢復(fù)損耗 (Err) 卻非如此,其在 25℃ 時可忽略不計,但隨著溫度升高,它們可能會達(dá)到損耗計算應(yīng)考慮的程度。因此,如前一章所述,考慮實(shí)際工作溫度下的參數(shù)至關(guān)重要,而不僅僅是 25℃。

在 Err 的情況下,值得注意的是,這些損耗的很大一部分是電容損耗,而不是 pn 結(jié)損耗。這些電容損耗看起來像示波器上的損耗,但不會導(dǎo)致體二極管發(fā)熱。這些損耗的影響和幅度取決于電壓和電流,但可能高達(dá)典型數(shù)據(jù)表中所示 Err損耗的 40%。因此,直接從數(shù)據(jù)表中獲取 Err 損耗是一種保守的方法。然后,在實(shí)際應(yīng)用中,只能通過比較系統(tǒng)輸入功率和系統(tǒng)輸出功率來測量總損耗。

圖 15:20 mΩ、1200 V SiC MOSFET 模塊中的開關(guān)損耗與 Tj

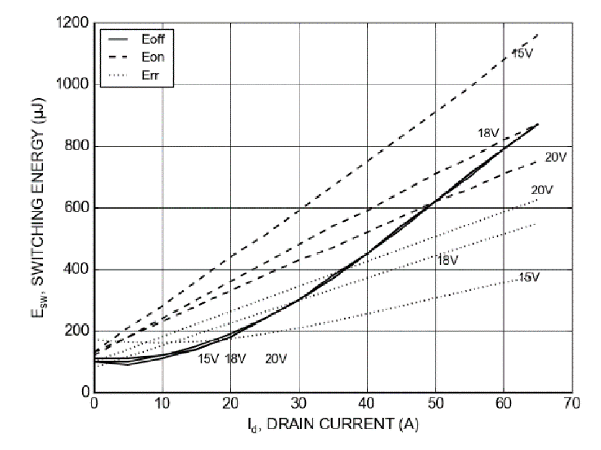

開關(guān)損耗隨漏極電流 (ID) 而增加

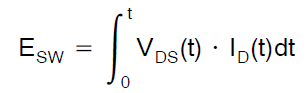

開關(guān)損耗隨漏極電流 (ID) 而增加根據(jù)定義,MOSFET 的開關(guān)損耗是指任何開關(guān)事件期間電壓時間積分與電流的乘積。

因此,預(yù)計損耗會隨著電流的增加而增加。但在將 M 1 1200 V SiC MOSFET 的行為與 IGBT 相比時,存在一些差異。如圖 16 所示,對于半橋配置的 20 mΩ、1200 V SiC 模塊,EON 與 ID 的關(guān)系是線性的,這些損耗將取決于換向回路中相應(yīng)二極管的恢復(fù)。體二極管的恢復(fù)損耗也表現(xiàn)為線性模式。另一方面,EOFF 損耗從二次增長開始,直到它們也變成線性的某一點(diǎn)。

圖 16:20 mΩ、1200 V SiC MOSFET 模塊中的開關(guān)損耗與 ID 特性

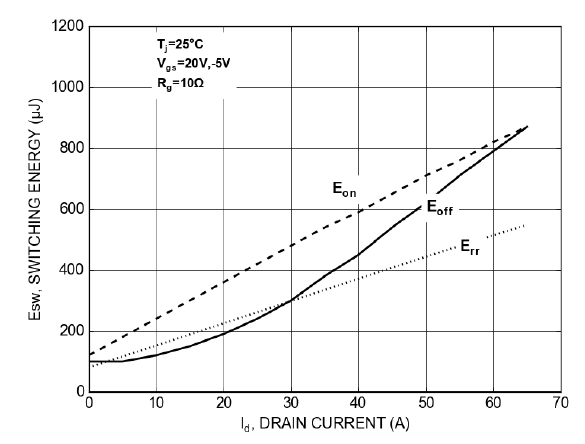

開關(guān)損耗與漏源電壓 (VDS)

開關(guān)損耗與漏源電壓 (VDS)

如前一點(diǎn)所述,開關(guān)損耗的另一個直接因素是 VDS,在這種情況下,如圖 17 所示,EON、EOFF 和 Err 以線性方式表現(xiàn),但斜率不同。

圖 17:20 mΩ、1200 V SiC MOSFET 模塊中的開關(guān)損耗與 VD

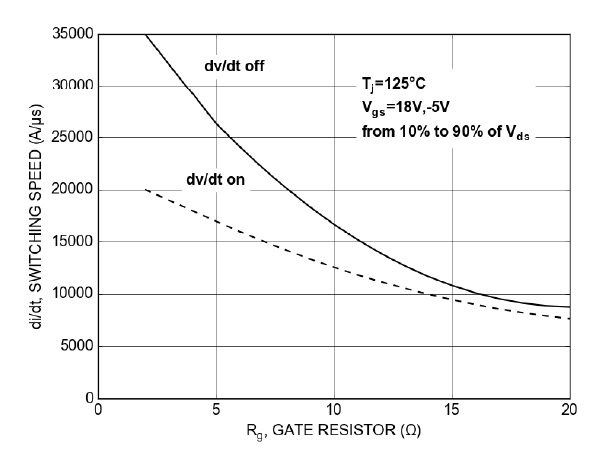

柵極電阻 (RG) 對開關(guān)性能的影響

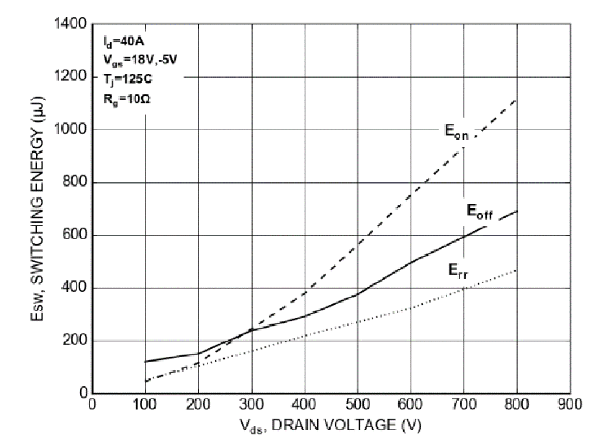

柵極電阻 (RG) 對開關(guān)性能的影響開關(guān)器件通過外部手段實(shí)現(xiàn)的可控性是電路設(shè)計中的關(guān)鍵因素。在 MOSFET 或 IGBT 的情況下,盡管是電壓控制器件,但影響其開關(guān)行為的最常見方式之一是修改外部柵極電阻 RG,其中包括調(diào)節(jié)開關(guān)事件中涉及的不同電容的充電或放電速度。因此,會直接影響開關(guān)時間以及 di/dt 或 dv/dt。

在第一階段,選擇適當(dāng)?shù)闹禃r,需要考慮 RG 對損耗的影響。RG 較高將使器件速度變慢,從而導(dǎo)致 EON 和 EOFF 損耗增加。圖 18 顯示了 20 mΩ、1200 V SiC MOSFET M 1 模塊中開關(guān)損耗與 RG 的關(guān)系。RG 較高的積極影響是 Err 損耗減少,這是因?yàn)?MOSFET 體二極管在較慢的開關(guān)速度下表現(xiàn)更平滑。

但是,這不能補(bǔ)償導(dǎo)通和關(guān)斷損耗的增加。

圖 18:20 mΩ、1200 V SiC MOSFET 模塊中的開關(guān)損耗與 RG

結(jié)論顯而易見,應(yīng)盡可能降低 RG。另一方面,任何電路的寄生電感和電容都可能導(dǎo)致臨界電壓過沖或振蕩,如果器件太快打開,會產(chǎn)生潛在的電磁干擾 (EMI),這不僅涉及主電流換向路徑,還涉及柵極電路。此外,在某些應(yīng)用中,出于安全原因,dV/dt 可能受到限制。因此,器件的速度必須能夠通過 RG 或最終的柵極電容 (CG) 輕松調(diào)節(jié),但不建議使用后者,因?yàn)樗赡軙跂艠O中造成嚴(yán)重的振蕩。圖 19 顯示了在使用安森美 M 1 SiC MOSFET 的 1200 V、20 mΩ 半橋模塊中 RG 對 dV/dt 的影響。此圖顯示,RG 的修改使用戶能夠?qū)?dV/dt 產(chǎn)生強(qiáng)大的影響,從而使開關(guān)行為適應(yīng)電路和應(yīng)用的要求。通過這種方式,每個用戶都能輕松為自己的應(yīng)用找到開關(guān)損耗和開關(guān)速度之間的最佳平衡。

圖 19. 20 mΩ、1200 V SiC MOSFET 模塊中 RG 的 dV/dt 可控性

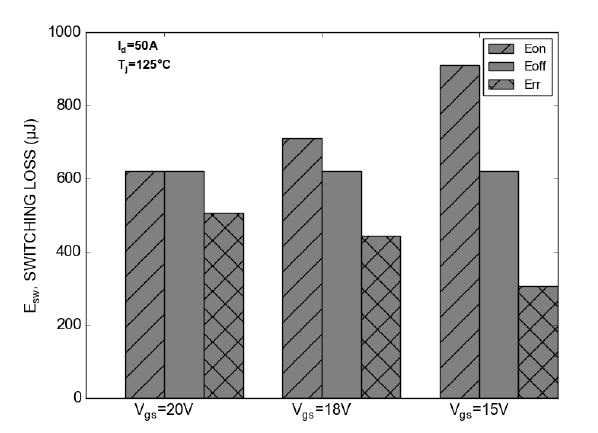

VGS 對開關(guān)損耗的影響

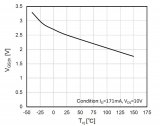

VGS 對開關(guān)損耗的影響在本應(yīng)用筆記的第一章中,討論了 VGS 對安森美 M 1 1200 V SiC MOSFET 靜態(tài)特性的影響。結(jié)論是,至少在 + 18 V 的電壓下使用該器件,高達(dá) + 20 V 的電壓更佳。如果現(xiàn)在正在考慮開關(guān)性能,則結(jié)論將是相同的。圖 20 顯示了開關(guān)損耗與 VGS 的相關(guān)性。EOFF 與正 VGS 無關(guān):在圖中,三條 EOFF 曲線重疊。另一方面,VGS 將對 EON 和 Err 行為產(chǎn)生重大影響。如果 VGS 增加并且使用相同的 RG,則電流給 CGD 和 CGS充電。結(jié)果導(dǎo)致器件開關(guān)變快,從而減少 EON 損耗,這對 Err 的影響正好相反,因?yàn)樗俣燃涌鞂⒃谙喾?MOSFET 的體二極管中引起更高的恢復(fù)損耗。

圖 20:20 mΩ、1200 V SiC MOSFET 模塊中正 VGS 對開關(guān)損耗的影響

如果考慮總損耗,如圖 21 所示,在 VGS 較高時,EON 損耗的減少會過度補(bǔ)償 Err 的增加,能夠更有效地在較高 VGS 下開關(guān)器件。當(dāng)然,還應(yīng)考慮其他因素,如 EMI 或 dV/dt。

圖 21:20 mΩ、1200 V SiC MOSFET 模塊中不同正 VGS 的總損耗

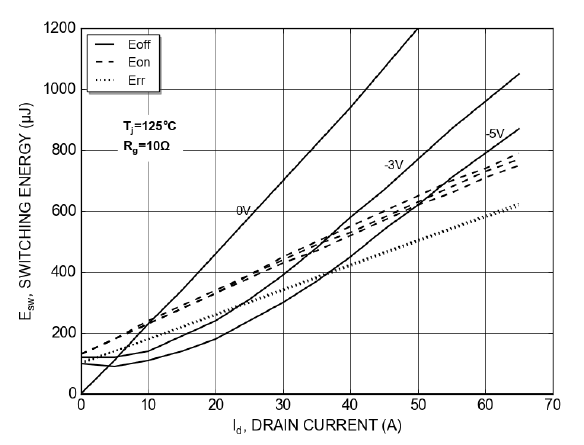

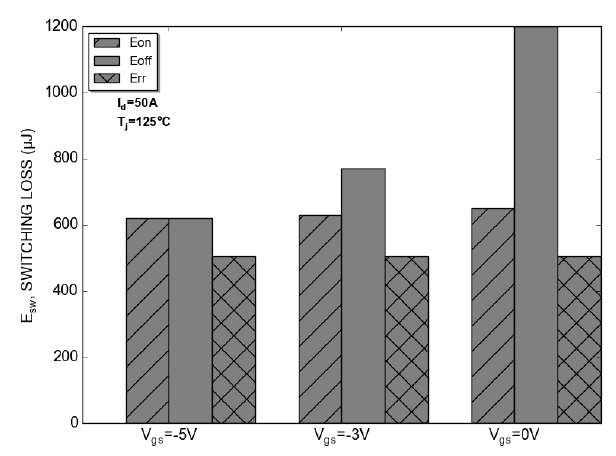

考慮到負(fù)柵極偏壓,之前強(qiáng)調(diào)了在體二極管應(yīng)導(dǎo)通期間使用負(fù)電壓完全關(guān)閉溝道的重要性。這也會對開關(guān)損耗產(chǎn)生影響。如圖 22 所示,雖然負(fù)柵極電壓對 EON 或 Err 損耗幾乎沒有影響,但 EOFF 損耗可能會受到嚴(yán)重影響。盡管 – 5 V 和 ?3 V 之間的差異約為 25%,但如果使用 0 V 負(fù)柵極偏壓,則 EOFF 損耗可能會翻倍。

圖 22:20 mΩ、1200 V SiC MOSFET 模塊中負(fù) VGS 對開關(guān)損耗的影響

在圖 23 中也可以觀察到這種影響,其中顯示了總損耗。

圖 23:20 mΩ、1200 V SiC MOSFET 模塊中不同 VGS 的總損耗

圖 23:20 mΩ、1200 V SiC MOSFET 模塊中不同 VGS 的總損耗

短路耐受時間 (SCWT)

短路耐受時間 (SCWT)在一些應(yīng)用中,SCWT 是挑選器件時需要考慮的一個重要要求。不過,此特性也會帶來一些影響。SCWT 較長會對靜態(tài)和動態(tài)性能產(chǎn)生影響。因此,在許多器件中,為了獲得更好的性能,會忽略此特性。

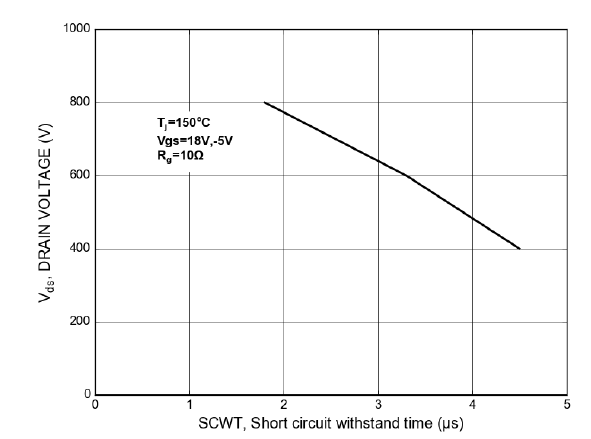

安森美 1200 V M 1 SiC MOSFET 留有一定的設(shè)計裕度,以提供短路耐受能力。器件能夠在短路中存活的時間取決于許多因素,最重要的因素是 VDS 和設(shè)備可能遭受短路事件的參考溫度。與本應(yīng)用筆記中討論的許多其他參數(shù)一樣,必須在合適的溫度下看待這些特性,雖然 125℃ 和 150℃ 之間的差異不大,但 SiC MOSFET 的 SCWT 在 25℃ 時可能會明顯更好。為了提供常見工作溫度的相關(guān)數(shù)據(jù),本文選擇了 150℃ 的起始溫度。圖 24 顯示了不同 VDS 的典型 SCWT。

重要提示:這些是典型的參考值,無法保證一定會實(shí)現(xiàn),請參考數(shù)據(jù)表中的值或聯(lián)系您當(dāng)?shù)氐募夹g(shù)支持人員。

圖 24:20 mΩ、1200 V 半橋 SiC MOSFET 模塊中的短路耐受時間

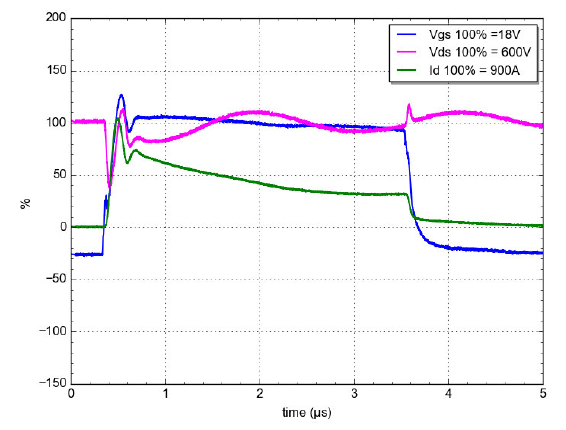

圖 25 顯示了 20 mΩ、1200 V SiC MOSFET 模塊在 150℃ 時的實(shí)際測量短路行為。

圖 25:20 mΩ、1200 V 半橋 SiC MOSFET 模塊中的短路行為

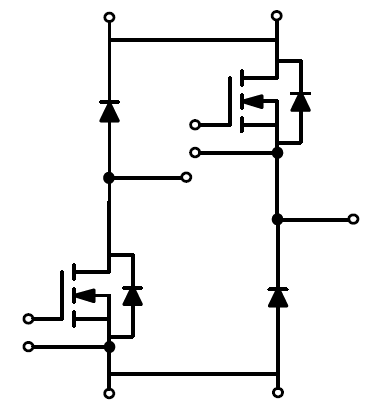

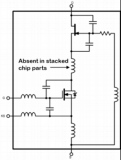

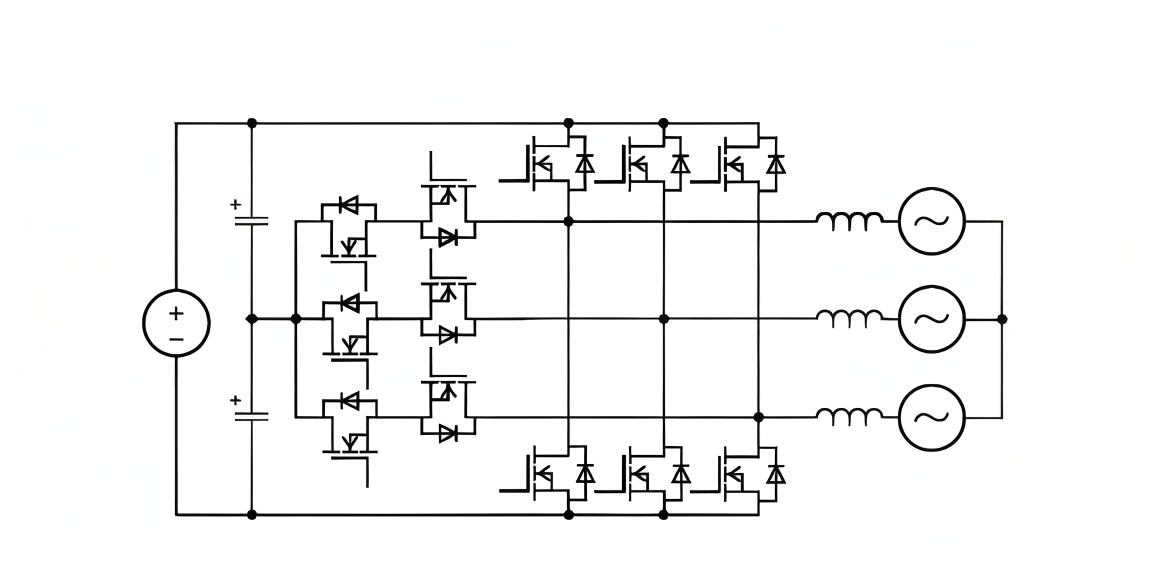

體二極管的動態(tài)特性如前幾章所述,即使不建議使用傳導(dǎo)損耗較高的 SiC MOSFET 體二極管,這也不能總是避免。改善總損耗的一種可能性是激活 MOSFET 的溝道以改善靜態(tài)行為,但這對動態(tài)性能的影響微乎其微。另一種方法是采用與 SiC MOSFET 并聯(lián)的外部 SiC 二極管。不過,為了完全禁用體二極管,應(yīng)將其與半橋的主換向路徑去耦,如圖 26 所示。

體二極管的動態(tài)特性如前幾章所述,即使不建議使用傳導(dǎo)損耗較高的 SiC MOSFET 體二極管,這也不能總是避免。改善總損耗的一種可能性是激活 MOSFET 的溝道以改善靜態(tài)行為,但這對動態(tài)性能的影響微乎其微。另一種方法是采用與 SiC MOSFET 并聯(lián)的外部 SiC 二極管。不過,為了完全禁用體二極管,應(yīng)將其與半橋的主換向路徑去耦,如圖 26 所示。

圖 26:具有拆分輸出的半橋

這種拆分不僅引入了額外的 SiC 二極管,而且增加了布局的復(fù)雜性。比較外部 SiC 二極管與體二極管的動態(tài)行為,如圖 27 所示,可以看出外部 SiC 二極管確實(shí)改善了反向恢復(fù)行為。但這種改善可能微不足道;特別是考慮到部分體二極管損耗無耗散。因此,用戶需要考慮在成本和復(fù)雜性都相應(yīng)增加的情況下添加此附加組件是否值得。

圖 27:外部 SiC 二極管(虛線)與 SiC MOSFET 體二極管(實(shí)線)的恢復(fù)行為

在電源模塊內(nèi)添加緩沖電容的影響

在電源模塊內(nèi)添加緩沖電容的影響任何設(shè)計中的雜散電感都將在器件的開關(guān)性能中發(fā)揮關(guān)鍵作用,不僅在效率方面,而且還會導(dǎo)致不必要的行為,例如振鈴或高壓過沖。考慮到 SiC 器件主要用于快速開關(guān)應(yīng)用,雜散電感產(chǎn)生不必要影響的風(fēng)險變得更高。因此,在任何設(shè)計中,都要首先保持寄生電感盡可能低。盡管如此,即使是最有經(jīng)驗(yàn)的設(shè)計人員也無法避免封裝固有的某些寄生和所需的最少 PCB 布線。

圖 28 顯示了標(biāo)準(zhǔn)半橋配置關(guān)鍵開關(guān)回路中主要組件的示意圖。為了縮短臨界回路的長度,應(yīng)盡可能靠近模塊放置低 ESR 電容。但是,這不會阻止回路中包含引腳電感、PCB 跡線和電容引線。

圖 28:具有外部電容的半橋模塊示意圖

圖 28:具有外部電容的半橋模塊示意圖

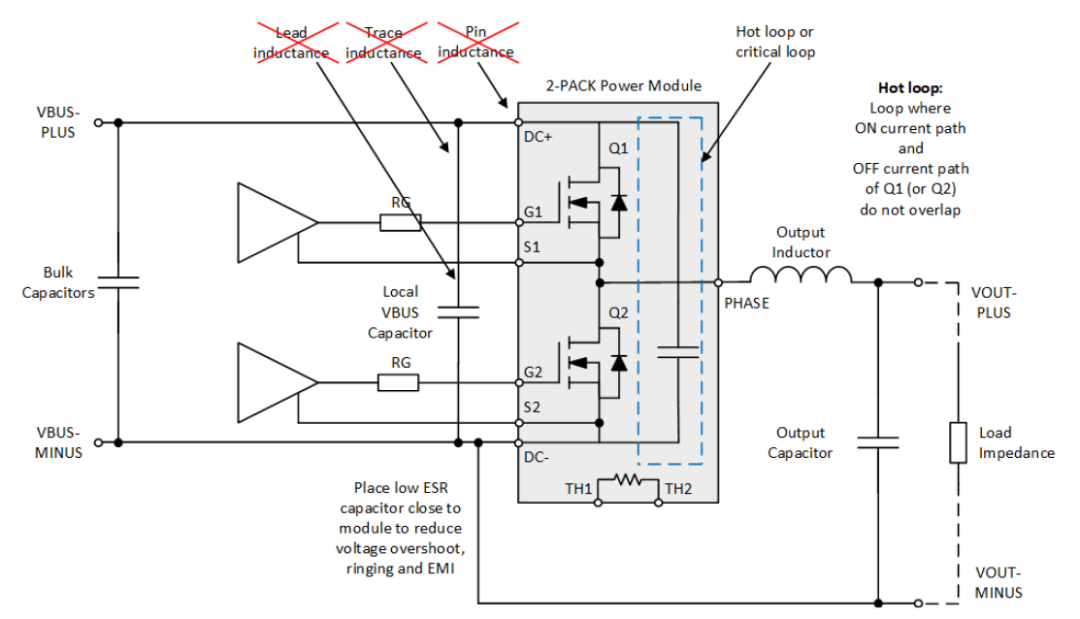

為了進(jìn)一步縮短臨界回路的長度,可以在模塊內(nèi)部集成一個額外的電容。如圖 29 所示。這樣,通過在一定程度上消除引腳、跡線和引線電感的影響,我們可以進(jìn)一步減小寄生電感。集成電容的尺寸受到模塊內(nèi)部可用空間的限制,例如,本研究使用了 100 nF 電容。

圖 29:具有集成電容的半橋模塊示意圖

圖 29:具有集成電容的半橋模塊示意圖

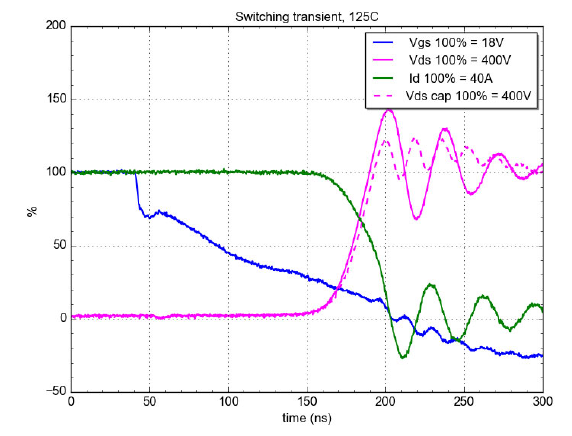

減小臨界回路電感將能改善開關(guān)行為。首先,如圖 30 所示,關(guān)斷時的電壓過沖可從近 150% 降至 120%。

圖 30:具有集成電容與外部電容的半橋關(guān)斷行為

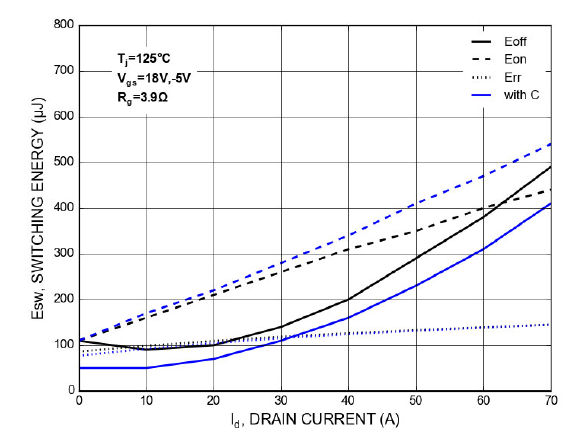

圖 30:具有集成電容與外部電容的半橋關(guān)斷行為如圖 31 所示,電壓過沖減少的直接后果是 Eoff 損耗減少。另一方面,隨著電流的增加,Eon 損耗可能會增加。在任何情況下,從總損耗來看,器件的公共電流能力都有所提高。

圖 31:具有和沒有集成電容的開關(guān)損耗

原版文檔獲取點(diǎn)擊文末的“贊”和“在看”,并發(fā)送截圖和您的郵箱地址到后臺,即可領(lǐng)取原版文檔哦~

點(diǎn)擊可查看1700 V EliteSiC MOSFET系列新品

原文標(biāo)題:安森美 M 1 1200 V SiC MOSFET 動態(tài)特性分析

文章出處:【微信公眾號:安森美】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

安森美

+關(guān)注

關(guān)注

32文章

1770瀏覽量

92813

發(fā)布評論請先 登錄

麥科信光隔離探頭在碳化硅(SiC)MOSFET動態(tài)測試中的應(yīng)用

Nexperia推出采用X.PAK封裝的1200V SiC MOSFET

?安森美推出基于碳化硅的智能功率模塊

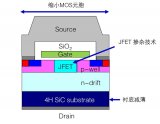

安森美SiC cascode JFET并聯(lián)設(shè)計的挑戰(zhàn)

安森美SiC Cascode JFET的背景知識和并聯(lián)設(shè)計

安森美新型SiC模塊評估板概述

國產(chǎn)SiC MOSFET在T型三電平拓?fù)渲械膽?yīng)用分析

安森美M3S與M2 SiC MOSFET的性能比較

SiC MOSFET的參數(shù)特性

又一大廠確定下一代SiC MOSFET采用溝槽設(shè)計

三菱電機(jī)1200V級SiC MOSFET技術(shù)解析

揭秘安森美在SiC市場的未來布局

瞻芯電子第三代1200V 13.5mΩ SiC MOSFET通過車規(guī)級可靠性測試認(rèn)證

安森美 M 1 1200 V SiC MOSFET 動態(tài)特性分析

安森美 M 1 1200 V SiC MOSFET 動態(tài)特性分析

評論