一. 前言

前面的文章https://mp.weixin.qq.com/s/wC79XEXMAK-3SGX8JkrFKw,完整的介紹了PSRAM的相關內容,比如接口時序等,但是該文章內容較多,需要花費一些時間慢慢閱讀。對于一些開發人員可能只是想大概了解一下PSRAM的關鍵信息點,或者說遇到問題了不知如何查起,想直接看看有沒有一些常見的坑,來對照排查自己的問題,本文就是針對此而寫。本文重點介紹PSRAM時序中幾個關鍵的點,也是沒有調試過PSRAM的開發人員可能會理解錯誤的點,以及時序的training算法等。每一個知識點都是從工程實踐出發,都是真金白銀的干貨,基本上這一些信息就包括了可能遇到的大部分問題了,先看這篇文章,基本就能避免各種坑了。

注意以下以APS256XXN為例,其他芯片不排除略有差異,但是關鍵時序不會有差異都是一樣的。

二.PSRAM關鍵知識點

2.1 總線寬度

默認是x8模式,可以通過寄存器修改為x16模式。

但是命令字和地址的發送始終是8位模式的,不過抓包可以看到此時高8位內容會和低8位的內容完全一樣。

2.2 地址空間

對于x16模式,因為其單位是x16bits即2B,所以頁內偏移地址即列地址,只需要CA[9:0]10位就足夠,可以表示2048字節,而x8模式需要CA[10:0]11位表示2048字節,行地址則不管是x8還是x16都是RA[13:0]。

又由于是DDR模式,即雙邊沿都傳輸數據,所以數據的最小傳輸單位是一個CLK,一個CLK就對應兩個總線寬度,對于x8模式是2B,對于x16模式就是4B,所以x8和x16模式最小的數據傳輸大小就是2B和4B,即列地址的bit0 CA[0]必須始終是0。

寄存器操作沒有以上限制可以從任意寄存器開始,但是也要注意由于是DDR所以一個CLK,PSRAM會發出連續兩個寄存器的值,CLK不停則連續的兩個寄存器重復發出。

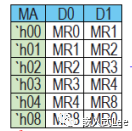

即對應下表

比如讀MA0則依次返回MR0和MR1,CLK不停則MR0和MR1重復返回.

2.3 命令地址的鎖存

在CE#變為LOW之后,指令字節在CE#拉低后**第一****個** **CLK上升沿被鎖存** **,** 注意這里是第一個上升邊沿,如果CE#拉低后首先出現的是CLK的下降沿則這個下降沿會略過,也是沒問題的。

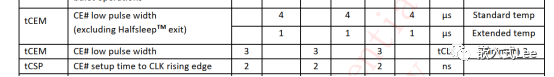

按照時序要求,指令字節需要一直保持到第一個CLK上升沿之后的下降沿,然后保持一個保持時間tHD,但是實際測試可能只需要保持到第一個CLK上升沿并且保持保持時間tHD就就夠了。實際應用還是建議完全按照手冊要求來,一直保持到下降沿之后的保持時間,這樣確保安全。這里還要注意CE#拉低到CLK拉高有一個最小的tCSP時間(2nS)要求,還有CLK上升沿之前數據的最小建立時間tSP。

如下所示

地址在第三、第四、第五和第六CLK邊沿(第二CLK上升沿、第二CLK下降沿、第三CLK上升邊沿、第三CL下降沿)被鎖存,以上邊沿計數是從CE#拉低之后的CLK上升沿開始作為第一個CLK邊沿計數。

如下是一個實際的應用中抓取到的波形,CE#拉低之后首先出現的是CLK的下降沿,這也是沒問題的

2.4 寫數據-DM

注意DM和DQS是復用的,都是發送方驅動,但是DQS和DM的含義完全是不一樣的。

DQS是讀數據時PSRAM驅動,用于表示數據就緒,控制器這邊根據DQS的邊沿延遲一定時間進行數據采樣。

而控制器發送數據,PSRAM并不是通過DM來采樣的,DM表示的是數據是否MASK掉,PSRAM是通過CLK的邊沿來采樣的,CLK的邊沿采樣再來結合此時DM電平表示對應的字節是否要寫入,如果DM為高則MASK掉指定字節不寫入。

所以結合DM可以實現單字節的寫入。

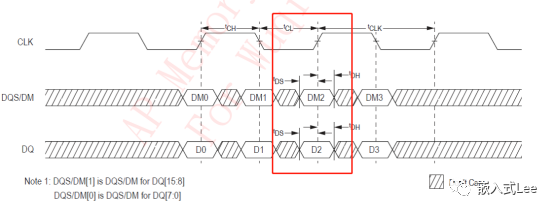

由于寫數據時是CLK邊沿采樣,且DM和數據是同時變化的,要相對CLK的邊沿有數據建立時間和保持時間分別是tDS,tDH。

如圖所示

2.5 讀數據-DQS

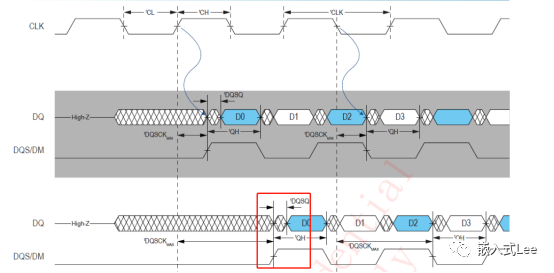

注意讀數據不一樣不再通過CLK的邊沿鎖存數據,而是通過DQS來鎖存數據了。

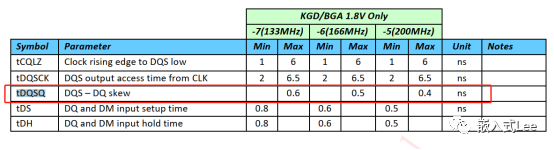

讀數據時PSRAM同時更新DQS和總線信號,但是兩者信號類型不一樣,一個是時鐘信號一個是總線數據信號,所以其物理上經過的路徑就是不一樣的,到達引腳時存在時間差,這個時間差就是tDQSQ,比如對于166MHz這個值就是最大不超過0.5nS,所以接收方需要在DQS的邊沿延時該時間之后再采樣才能保證采樣到正確的數據。大部分讀不到數據基本都是接收方這個時間設置不對,正常來說接收方會有一個PHY可以通過寄存器配置該時間,接收training也就是不斷調整該時間然后確定一個合適的中間的值。

2.6 x8和x16的存儲映射

不管是x8還是x16模式頁的大小都是2K,但是x8模式和x16模式數據在頁內的放置是不一樣的。

X8模式按照字節序列寫入頁內的0~2047字節

X16模式則1字節寫入頁內的01022處,另外字節寫入頁內的10232047處。

所以要注意如果動態切換模式,則讀出的數據內容就不一樣了。

2.7 讀寫數據的長度

普通模式讀寫數據最長由Burst Type決定,不能超過一個PAGE的大小;

寫最小長度是一個CLK對應的長度,x8模式就是一個CLK兩個邊沿2字節,X16模式就是一個CLK兩個邊沿2x2=4字節;讀沒有最小長度限制。寫數據可以結合DM來MASK寫入單字節,而讀數據沒有MASK。讀寫數據的開始地址和長度要是2(x8)或者4(x16)字節對齊。

讀寫數據如果是使能了RXB且使用Linear Burst 讀寫模式則理論上讀寫最長字節數沒有限制,但是要受限于tCEM即CE拉低的時間限制

對于標準溫度最長CE可以拉低4uS,如果算200MHz時鐘,4uS有 800個CLK,不考慮命令地址,延遲等時間,800個CLK最多可以傳輸800x2x2個字節。

如果是擴展溫度1uS,算200MHz時鐘,4uS有200個CLK,不考慮命令地址,延遲等時間,200個CLK最多可以傳輸200x2x2個字節。

所以也不多,一般都是一次傳輸讀寫256個字節。

2.8 training

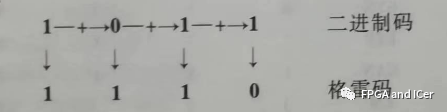

所謂的training就是針對讀和寫兩個關鍵的時序參數來進行

讀即DQS延遲tDQSQ時間之后再進行采樣

寫即數據在CLK邊沿tDS之前建立,都是數據建立時間的概念。

根本原因是因為時鐘信號和數據總線信號走的路徑不一樣,所以出現在引腳上的時刻也不一樣(內部邏輯電路是時序邏輯電路都是在時鐘的邊沿進行數據更新的,理論上數據源是同步的)。

對于發送時,控制器的邏輯電路修改數據是在CLK邊沿進行的,但是傳播到引腳上時數據較CLK延后了,哪怕不延后數據也最多只能和時鐘保持同步,不能滿足數據建立時間要求,所以就要人為的在CLK的輸出路徑上加上延遲,以滿足建立時間的要求。

對于接收,同樣的道理,數據在出現在引腳上時已經滯后DQS了,這個時間就是tDQSQ,所以不能DQS邊沿采樣了,需要延遲一段時間采樣,所以需要在DQS的輸入路徑上人為的添加延遲。

這兩個延遲是由PHY去控制的,會提供寄存器接口給軟件控制,軟件就是控制這兩個延遲時間來進行training。

所謂的training就是,不斷嘗試讀寫,通過判斷讀是否正確,來判斷參數是否合適,得到一個范圍的參數,取中間值。修改這兩個時序如果能正確讀寫就認為這個參數可行,然后在所有可行的參數中取中間值,以獲得較高的冗余度。讀寫是否正確一般通過讀某個有固定值的寄存器來確定。

具體算法如下:

由于有兩個參數,一個決定發送,一個決定接收,由于一次傳輸比如讀寄存器,需要先發送命令地址,然后讀,涉及到兩個過程,任意一個過程錯誤都不能讀到正確的數據。

所以兩個參數都需要遍歷嘗試,實際就是兩層嵌套遍歷。

一般可以讀內容是固定的寄存器,比如廠商ID對應的寄存器,假設CLK延遲參數可以配置為099,DQS延遲參數可配置為099

那么組合就有100*100次嘗試,也可以增加遞增間隔以減少嘗試次數。

先固定CLK延遲,遍歷DQS延遲,記錄能讀到正確數據的DQS延遲范圍

再遞增CLK延遲,遍歷DQS延遲,記錄能讀到正確數據的DQS延遲范圍

在所有能讀到正確數據的DQS延遲范圍中選擇范圍最寬的,取其范圍的中間的DQS延遲值作為最終的DQS延遲值。

在所有能讀到正確數據的CLK延遲中取中間的CLK延遲值作為最終的CLK延遲值。

三. 實測波形

如下地址有使用邏輯分析抓包的實際PSRAM讀寫寄存器和數據的波形記錄,可以參考。

注意這些記錄波形是實際測試過程中抓取的,不是最終的最好狀態,不能作為標準波形參考,標準波形需要參考手冊。

鏈接:https://pan.baidu.com/s/1HHGEvwz_NHT_tra4ONe-RQ?pwd=45b9

提取碼:45b9

四. 總結

以上分享了PSRAM接口一些關鍵的知識點,大部分是容易理解錯誤,且導致問題的點,基本上理解這些點就能解決大部分問題了,作為入門參考也可以先看這篇,先有個大概了解。作為遇到問題不知如何解決時也可以參考這篇文章,基本上能解決大部分問題。

審核編輯:湯梓紅

-

嵌入式

+關注

關注

5141文章

19542瀏覽量

315178 -

接口

+關注

關注

33文章

8952瀏覽量

153224 -

PSRAM

+關注

關注

1文章

38瀏覽量

13708 -

時序

+關注

關注

5文章

397瀏覽量

37793

發布評論請先 登錄

【視頻課程】MATLAB知識點講解1

數控電源的知識點講解

EMC 設計避坑指南:四不口訣

PSRAM避坑指南-關鍵知識點講解

PSRAM避坑指南-關鍵知識點講解

評論