前言

本文以一個實例,講解RISC-V未對齊訪問導致的問題.

未對齊導致的問題很常見,本文以實例分享調試分析過程。

過程

現象是程序進入了異常中斷函數exception()

先分部打端點,結合step單步運行,確認執行哪個函數的哪一句執行后異常。

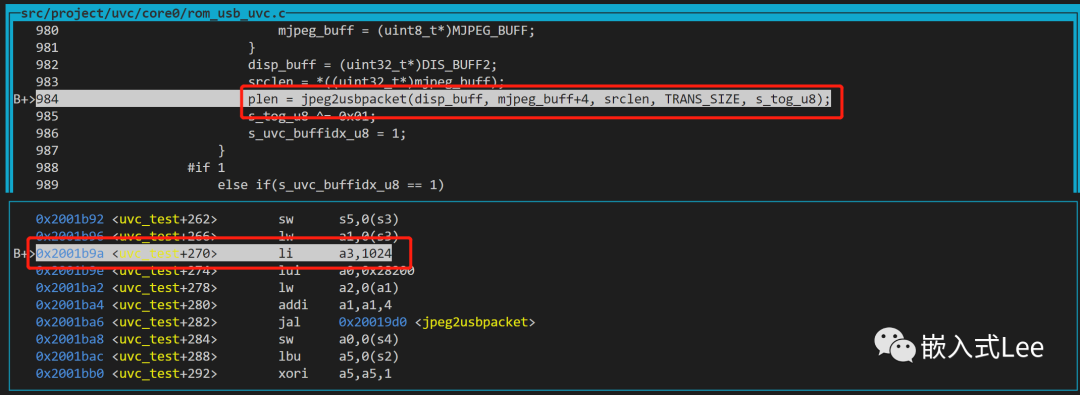

這里已經確認是rom_usb_uvc.c的984行執行后異常。

在執行異常的語句前打斷點

b rom_usb_uvc.c:984

再重新運行到該處

顯示匯編界面layout split

stepi按照匯編單步執行

最終確認執行匯編指令

lw a2,0(a1)后異常

查看此時寄存器a1的值。

(gdb) info reg a1

a1 0x28429ddd 675454429

stepi執行完`lw a2,0(a1)``后進入異常處理函數

查看此時mcause寄存器

(gdb) info reg mcause

mcause 0x4 4

見 對應 即 所以修改緩沖區按照WORD對齊。<的<>.Load address misaligned。正是lw指令寄存器a1間接尋址非WORD對齊地址0x28429ddd導致。

jpeg2usbpacket函數傳入的指向緩沖區的指針參數非WORD對齊導致。

審核編輯:湯梓紅

-

嵌入式

+關注

關注

5152文章

19675瀏覽量

317547 -

調試

+關注

關注

7文章

612瀏覽量

34722 -

程序

+關注

關注

117文章

3826瀏覽量

82979 -

函數

+關注

關注

3文章

4381瀏覽量

64868 -

RISC-V

+關注

關注

46文章

2570瀏覽量

48824

發布評論請先 登錄

rIsc-v的缺的是什么?

為什么選擇RISC-V?

RISC-V 發展

RISC-V未對齊訪問導致問題案例

RISC-V規范的演進 RISC-V何時爆發?

第一屆RISC-V中國峰會看點 risc-v開發要怎么優化risc-v指令集架構代碼密度

RISC-V的挑戰分析

RISC-V學習筆記【1】RISC-V概述

openEuler加入RISC-V Landscape

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V未對齊導致問題案例

RISC-V未對齊導致問題案例

評論