曾經(jīng)有一段時(shí)間,實(shí)際上是幾十年,制造更好的計(jì)算機(jī)芯片所需要的只是更小的晶體管和更窄的互連。DNA那個(gè)時(shí)代已經(jīng)一去不復(fù)返了,雖然晶體管會繼續(xù)變得更小,但簡單地制造它們已不再是重點(diǎn)。

上周在比利時(shí)安特衛(wèi)普舉行的ITF 2023 世界大會上,研究人員認(rèn)為,現(xiàn)在保持計(jì)算速度呈指數(shù)級增長的唯一方法是一種稱為系統(tǒng)技術(shù)協(xié)同優(yōu)化 (STCO) 的方案。它能夠?qū)⑿酒纸獬伤鼈兊墓δ芙M件,為每個(gè)功能使用最佳的晶體管和互連技術(shù),并將它們重新拼接在一起以創(chuàng)建一個(gè)功耗更低、功能更好的整體。

Imec研發(fā)經(jīng)理Marie Garcia Bardon說:“這將我們引向 CMOS 的新范式。” 正如總部位于比利時(shí)的納米技術(shù)研究組織所稱,CMOS 2.0 是一個(gè)復(fù)雜的愿景。但它可能是最實(shí)用的前進(jìn)方式,其中的一部分已經(jīng)在當(dāng)今最先進(jìn)的芯片中得到體現(xiàn)。

我們是怎么到這里的

Imec 研發(fā)副總裁Julien Ryckaert說,從某種意義上說,半導(dǎo)體行業(yè)在 2005 年之前的幾十年里被寵壞了。在那段時(shí)間里,化學(xué)家和設(shè)備物理學(xué)家能夠定期生產(chǎn)更小、功耗更低、速度更快的晶體管,可用于芯片上的每項(xiàng)功能,這將導(dǎo)致計(jì)算能力的穩(wěn)步提高。

但此后不久,輪子開始脫離該計(jì)劃。設(shè)備專家可以想出出色的新晶體管,但這些晶體管并不能制造出更好、更小的電路,例如構(gòu)成 CPU 主體的 SRAM 存儲器和標(biāo)準(zhǔn)邏輯單元。作為回應(yīng),芯片制造商開始打破標(biāo)準(zhǔn)單元設(shè)計(jì)和晶體管開發(fā)之間的障礙。稱為設(shè)計(jì)技術(shù)協(xié)同優(yōu)化或 DTCO 的新方案導(dǎo)致專門設(shè)計(jì)用于制造更好的標(biāo)準(zhǔn)單元和存儲器的設(shè)備。

但 DTCO 不足以讓計(jì)算繼續(xù)進(jìn)行。物理和經(jīng)濟(jì)現(xiàn)實(shí)的局限性共同為通用型晶體管的發(fā)展設(shè)置了障礙。如Imec 的首席工程師Anabela Veloso解釋說,物理限制阻止了 CMOS 工作電壓降低到大約 0.7 伏以下,從而減緩了功耗的進(jìn)展。轉(zhuǎn)向多核處理器幫助改善了這個(gè)問題一段時(shí)間。同時(shí),輸入輸出限制意味著越來越需要將多個(gè)芯片的功能集成到處理器上。

因此,除了具有多個(gè)處理器內(nèi)核實(shí)例的片上系統(tǒng) (SoC) 之外,它們還集成了網(wǎng)絡(luò)、內(nèi)存和通常專用的信號處理內(nèi)核。這些內(nèi)核和功能不僅具有不同的功率和其他需求,而且它們也無法以相同的速度變得更小。即使是 CPU 的高速緩存 SRAM,也不會像處理器的邏輯那樣快速縮小。

系統(tǒng)技術(shù)協(xié)同優(yōu)化

讓事情擺脫困境與技術(shù)集合一樣是一種哲學(xué)轉(zhuǎn)變。根據(jù) Ryckaert 的說法,STCO 意味著將片上系統(tǒng)視為功能的集合,例如電源、I/O 和緩存存儲器。“當(dāng)你開始對功能進(jìn)行推理時(shí),你會意識到 SoC 不是這種同質(zhì)系統(tǒng),只是晶體管和互連,”他說。“它是功能,針對不同的目的進(jìn)行了優(yōu)化。”

理想情況下,您可以使用最適合它的工藝技術(shù)來構(gòu)建每個(gè)功能。實(shí)際上,這主要意味著在自己的硅片或小芯片上構(gòu)建每個(gè)。然后,您可以使用高級 3D 堆疊等技術(shù)將它們綁定在一起,這樣所有功能就好像它們在同一塊硅片上一樣。

這種想法的例子已經(jīng)出現(xiàn)在高級處理器和人工智能加速器中。英特爾的高性能計(jì)算加速器 Ponte Vecchio(現(xiàn)在稱為英特爾數(shù)據(jù)中心 GPU Max)由 47 個(gè)小芯片組成,這些小芯片使用兩種不同的工藝構(gòu)建,分別來自英特爾和臺積電。AMD 已經(jīng)在I /O 小芯片上使用了不同的技術(shù)并在其 CPU 中計(jì)算小芯片,它最近開始為計(jì)算小芯片的高級高速緩存分離出SRAM 。

Imec 的 CMOS 2.0 路線圖走得更遠(yuǎn)。該計(jì)劃需要繼續(xù)縮小晶體管,將電源和可能的時(shí)鐘信號移動到 CPU 的硅片下方,以及更加緊密的 3D 芯片集成。Ryckaert 說:“我們可以使用這些技術(shù)來識別不同的功能,分解 SoC,然后重新集成它,從而非常高效。”

晶體管將在未來十年內(nèi)改變形式,但連接它們的金屬也會改變。最終,晶體管可能是由二維半導(dǎo)體而不是硅制成的堆疊設(shè)備。電力傳輸和其他基礎(chǔ)設(shè)施可以分層放置在晶體管下方。

持續(xù)的晶體管縮放

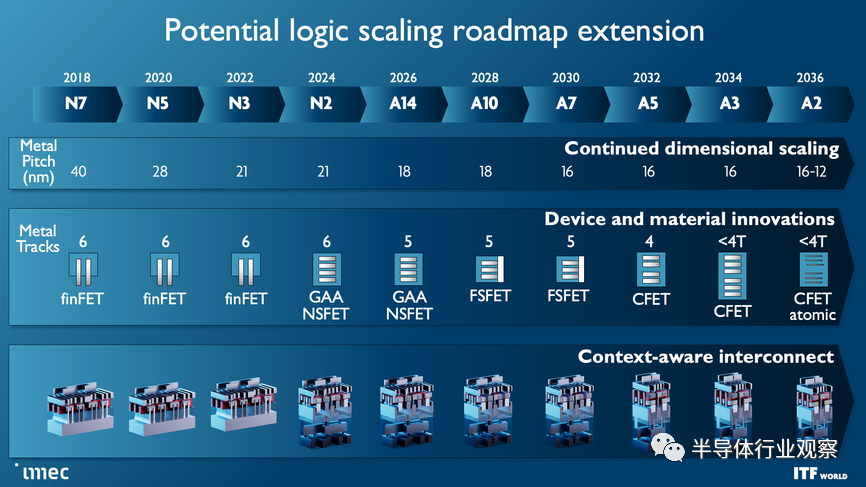

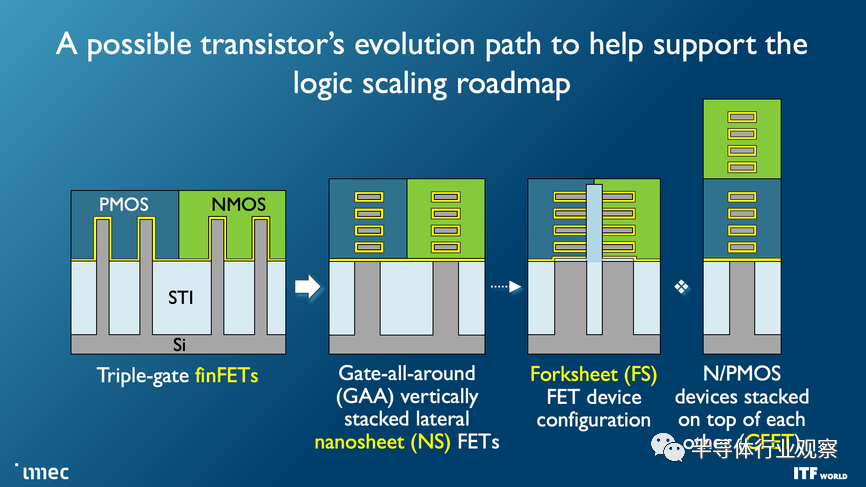

主要芯片制造商已經(jīng)從為過去十年的計(jì)算機(jī)和智能手機(jī)提供動力的 FinFET 晶體管過渡到一種新的架構(gòu),納米片晶體管。最終,兩個(gè)納米片晶體管將在彼此之上構(gòu)建,形成互補(bǔ)的 FET 或 CFET,Velloso 稱其“代表了 CMOS 縮放的終極”。

隨著這些設(shè)備按比例縮小和改變形狀,主要目標(biāo)之一是縮小標(biāo)準(zhǔn)邏輯單元的尺寸。這通常以“軌道高度”來衡量——基本上,可以安裝在單元內(nèi)的金屬互連線的數(shù)量。先進(jìn)的FinFET和早期的納米片器件是六軌cell。移動到五個(gè)軌道可能需要一種稱為 forksheet 的間隙設(shè)計(jì),它可以將設(shè)備更緊密地?cái)D壓在一起,而不必使它們更小。然后 CFET 會將單元減少到四個(gè)軌道或可能更少。

根據(jù) Imec 的說法,芯片制造商將能夠使用ASML 的下一代極紫外光刻技術(shù)生產(chǎn)出這一進(jìn)展所需的更精細(xì)的特征。這項(xiàng)稱為高數(shù)值孔徑 EUV 的技術(shù)目前正在 ASML 建設(shè)中,而 Imec 是下一個(gè)交付的。增加數(shù)值孔徑,一個(gè)與系統(tǒng)可以收集光線的角度范圍相關(guān)的光學(xué)術(shù)語,可以產(chǎn)生更精確的圖像。

背面供電網(wǎng)絡(luò)

背面供電網(wǎng)絡(luò)的基本思想是從硅表面上方移除所有發(fā)送電力(而不是數(shù)據(jù)信號)的互連,并將它們放置在硅表面下方。這應(yīng)該允許更少的功率損耗,因?yàn)楣β蕚鬏敾ミB可以更大且電阻更小。它還為信號傳輸互連釋放了晶體管層上方的空間,可能導(dǎo)致更緊湊的設(shè)計(jì)。

將來,更多的可能會被轉(zhuǎn)移到硅片的背面。例如,所謂的全局互連——那些跨越(相對)遠(yuǎn)距離以傳輸時(shí)鐘和其他信號的互連——可以位于硅片下方。或者,工程師可以添加有源功率傳輸設(shè)備,例如靜電放電安全二極管。

3D整合

進(jìn)行 3D 集成的方法有多種,但當(dāng)今最先進(jìn)的是晶圓到晶圓和芯片到晶圓的混合鍵合。這兩個(gè)提供了兩個(gè)硅芯片之間最高密度的互連。但這種方法要求兩個(gè)芯片設(shè)計(jì)在一起,因此它們的功能和互連點(diǎn)對齊,使它們可以作為一個(gè)芯片,技術(shù)人員的主要成員 Anne Jourdain 說。Imec R&D 有望在不久的將來每平方毫米產(chǎn)生數(shù)百萬個(gè) 3D 連接。

進(jìn)入 CMOS 2.0

CMOS 2.0 將分解和異構(gòu)集成發(fā)揮到極致。根據(jù)哪些技術(shù)對特定應(yīng)用有意義,它可能會產(chǎn)生一個(gè)包含嵌入式內(nèi)存、I/O 和電源基礎(chǔ)設(shè)施、高密度邏輯、高驅(qū)動電流邏輯和大量緩存存儲器層的 3D 系統(tǒng)。

要達(dá)到這一點(diǎn),不僅需要技術(shù)開發(fā),還需要工具和培訓(xùn)來辨別哪些技術(shù)可以真正改進(jìn)系統(tǒng)。正如 Bardon 指出的那樣,智能手機(jī)、服務(wù)器、機(jī)器學(xué)習(xí)加速器以及增強(qiáng)現(xiàn)實(shí)和虛擬現(xiàn)實(shí)系統(tǒng)都有非常不同的要求和限制。對一個(gè)人有意義的事情對另一個(gè)人來說可能是死胡同。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

459文章

52184瀏覽量

436209 -

CMOS

+關(guān)注

關(guān)注

58文章

5992瀏覽量

238076 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8492瀏覽量

134091

原文標(biāo)題:芯片微縮最新路線圖,2036年實(shí)現(xiàn)0.2nm

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

三星在4nm邏輯芯片上實(shí)現(xiàn)40%以上的測試良率

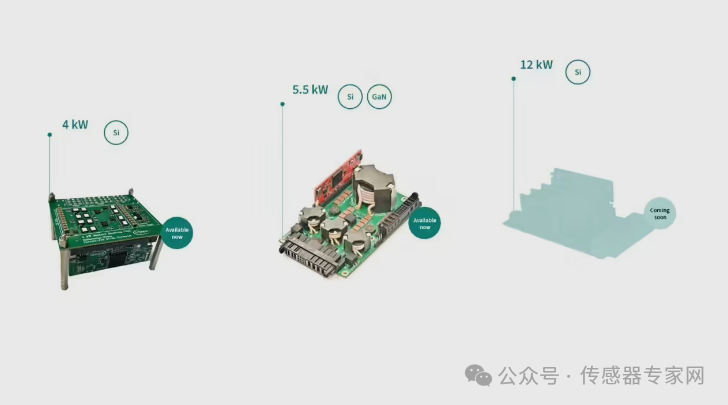

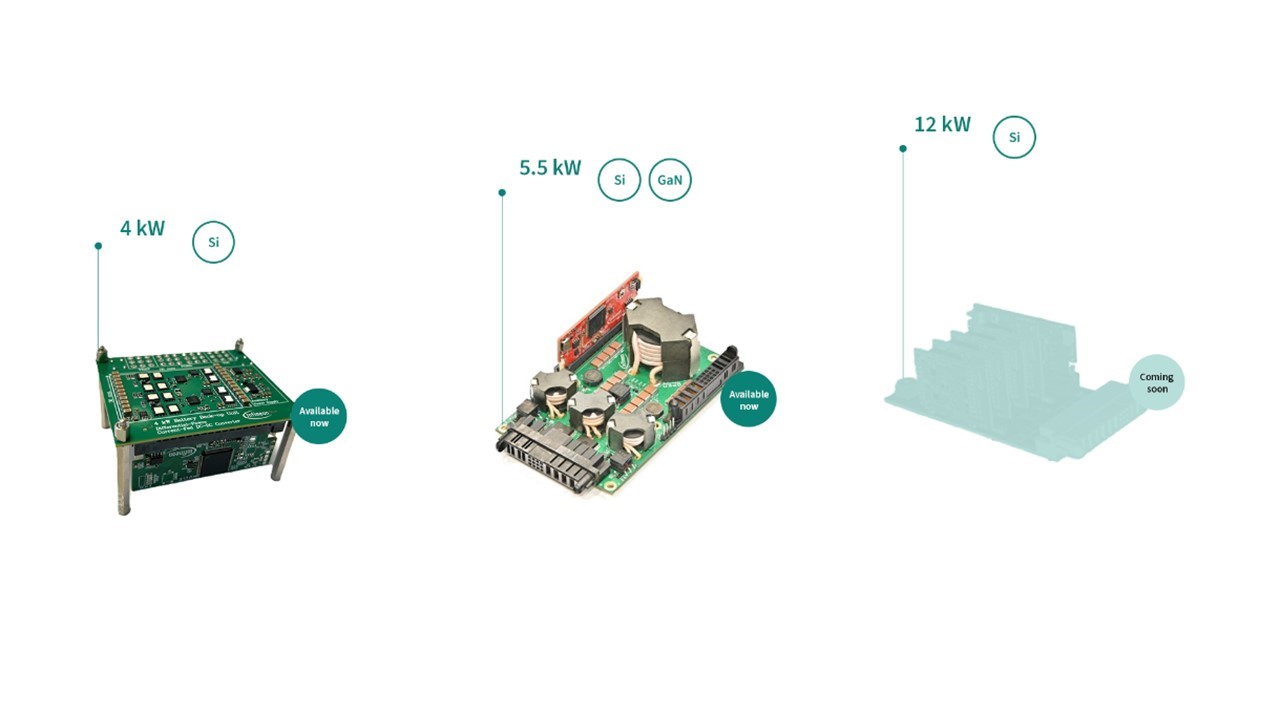

英飛凌公布AI數(shù)據(jù)中心電池備份單元BBU路線圖,全球首款12kW系統(tǒng)在列

英飛凌針對AI數(shù)據(jù)中心推出先進(jìn)的電池備份單元技術(shù), 進(jìn)一步完善Powering AI路線圖

OpenAI簡化大模型選擇:薩姆·奧特曼制定路線圖

2022年CT MICRO光耦合器新產(chǎn)品和路線圖

關(guān)于RISC-V學(xué)習(xí)路線圖推薦

未來10年智能傳感器怎么發(fā)展?美國發(fā)布最新MEMS路線圖

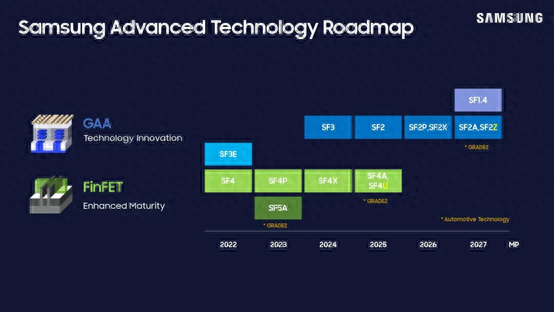

三星加速2nm及1.4nm制程投資

越南定半導(dǎo)體路線圖:2030年建1芯片廠10封測廠

三星電子計(jì)劃在2026年推出最后一代10nm級工藝1d nm

2024學(xué)習(xí)生成式AI的最佳路線圖

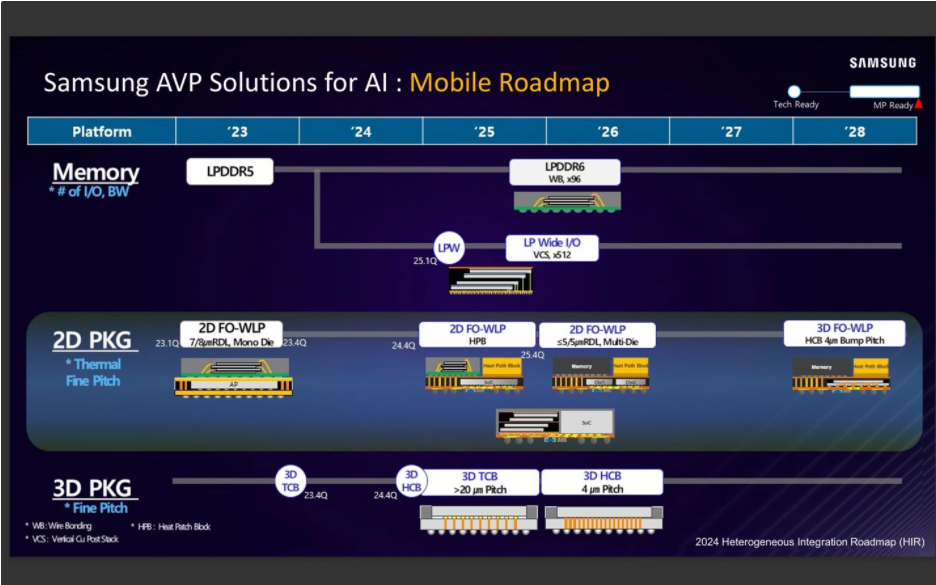

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動內(nèi)存即將面世

三星展望2027年:1.4nm工藝與先進(jìn)供電技術(shù)登場

三星公布最新工藝路線圖

芯片微縮最新路線圖,2036年實(shí)現(xiàn)0.2nm

芯片微縮最新路線圖,2036年實(shí)現(xiàn)0.2nm

評論