behavior model,即建立行為級模型。主要采用matlab、veriloga等工具,對設計進行行為級建模。

通過建模,確定設計核心參數(shù)、非理想因素對于電路的影響、對電路的功能進行快速驗證。

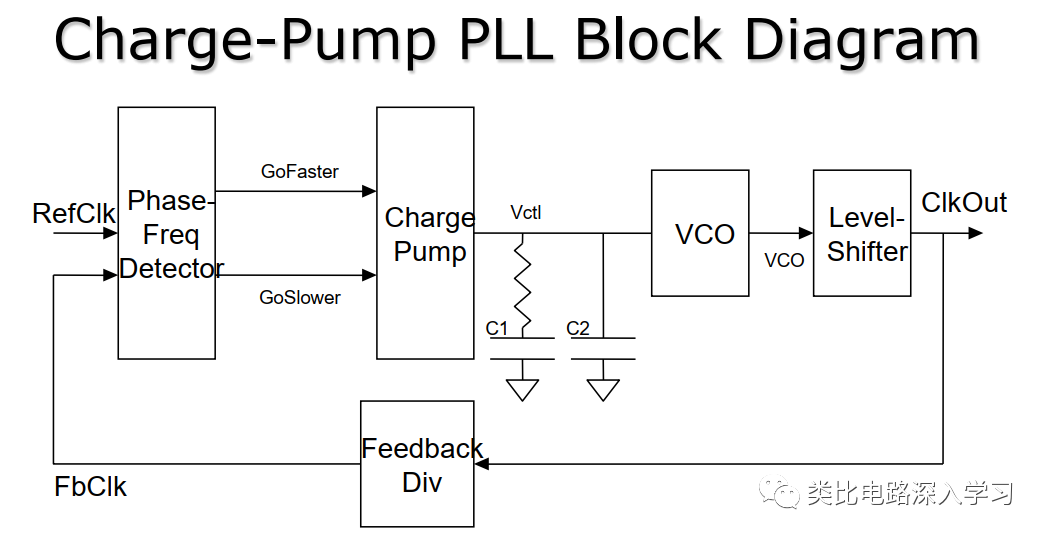

本文以SoC中的整數(shù)PLL為例,行為級建模工具選擇matlab。

對PLL的環(huán)路參數(shù)進行設計,并通過行為級模型進行仿真。

PLL,是一個小型的控制系統(tǒng)。規(guī)格如下:

| 參數(shù) | 示例 |

|---|---|

| 參考時鐘頻率 | 13MHz~76.8MHz |

| 輸出時鐘頻率 | 100MHz~2GHz |

| 鎖定時間 | <100uS |

| Period Jitter RMS | <2ps |

| 輸出時鐘duty cycle | 40%~60% |

| 功耗 | <5mA |

| 輸出時鐘頻率精度 | <±300ppm |

其環(huán)路參數(shù)的分析、假定和計算如下:

1)環(huán)路分頻比N

根據(jù)輸入頻率范圍26M76.8MHz,輸出頻率范圍104M2.002GHz。可以計算得到環(huán)路分頻比N范圍為4~77

這里先假定為2uA

3)壓控振蕩器的增益Kvco

由于本文采用CP PLL(single-path loop filter),即最傳統(tǒng)也是最可靠的結(jié)構(gòu)進行設計。因此控制電壓在0~vdd范圍內(nèi)變化,頻率需要在PVT下覆蓋輸出頻率范圍,因此Kvco這里假定為4GHz/V

- 環(huán)路帶寬和相位裕度

這里先假定為500kHz和50°

環(huán)路參數(shù)匯總?cè)缦?/p>

| 參數(shù) | 選定值 |

|---|---|

| 參考時鐘頻率FIN | 26MHz |

| 輸出時鐘頻率FOUT | 104MHz~2.002GHz |

| 環(huán)路分頻比N | 4~77 |

| 電荷泵電流Icp | 2uA |

| 壓控振蕩器的增益Kvco | 4GHz/V |

| 環(huán)路濾波器階數(shù) | 二階 |

| 環(huán)路帶寬BW | 500KHz |

| 環(huán)路相位裕度PM | 50° |

根據(jù)上述參數(shù)進行環(huán)路濾波器設計,

1)hands on

R1=BWN/(IcpKvco2PI)=6.87kΩ

C1=tan(PM)/(BWR12PI)=55pF

C2=0.1*C1=5.5pF

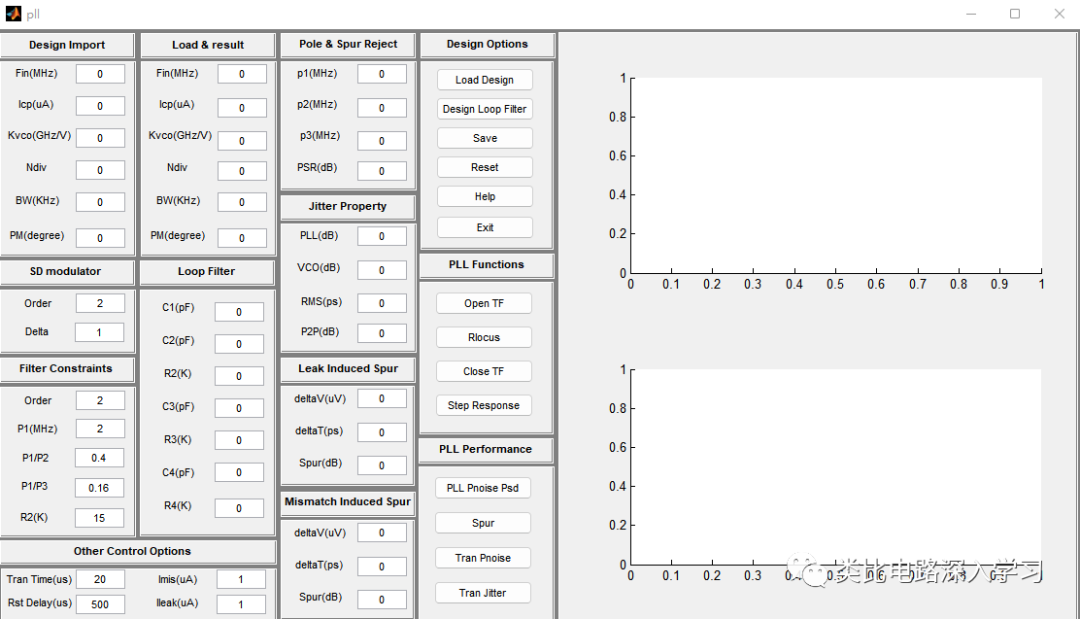

2)ToolBox Get

ToolBox CPPSIM by Perrott (http://www.cppsim.com)

ToolBox pll_tool by EETOP Senior(https://bbs.eetop.cn/thread-448188-1-1.html)

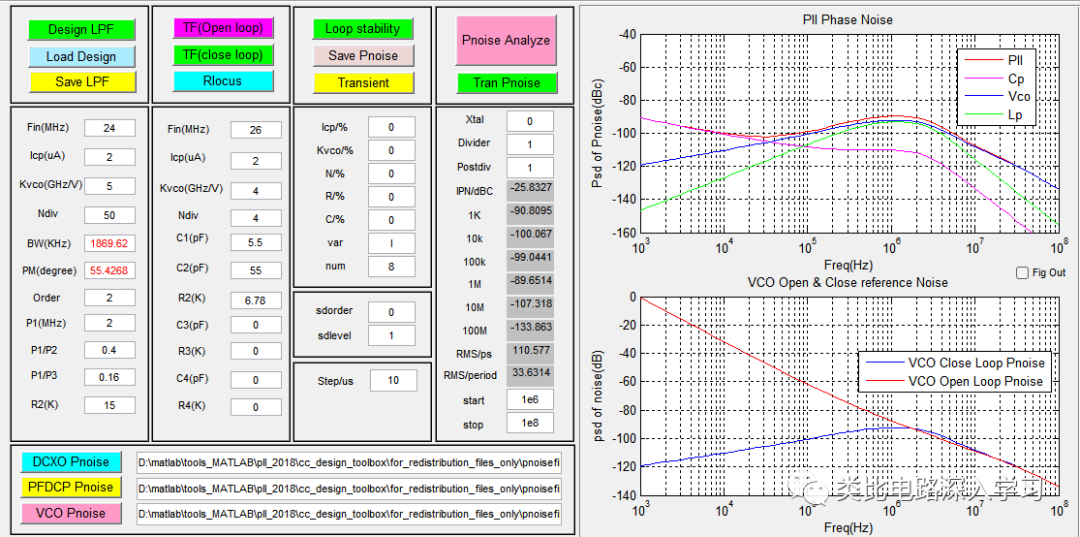

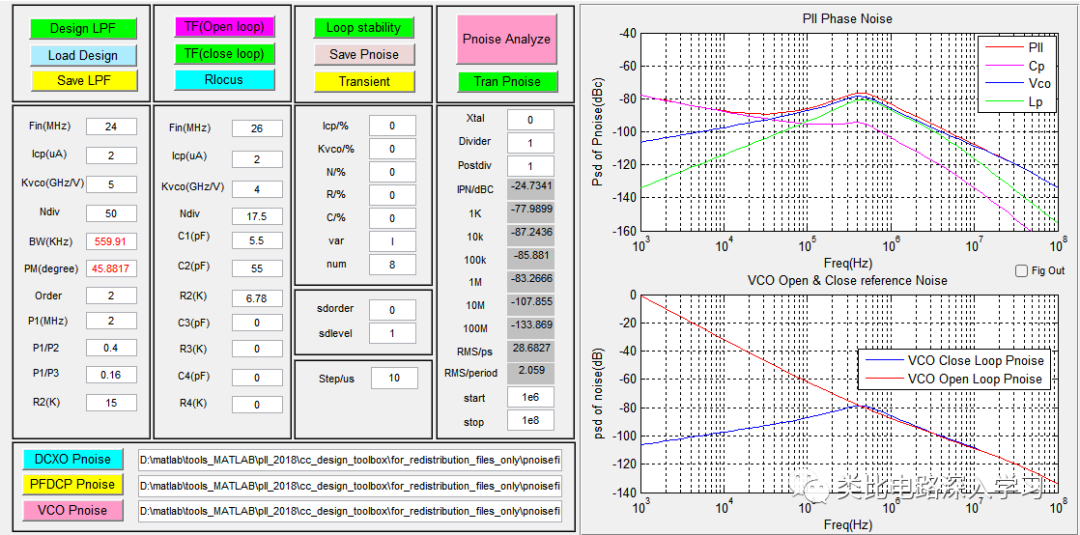

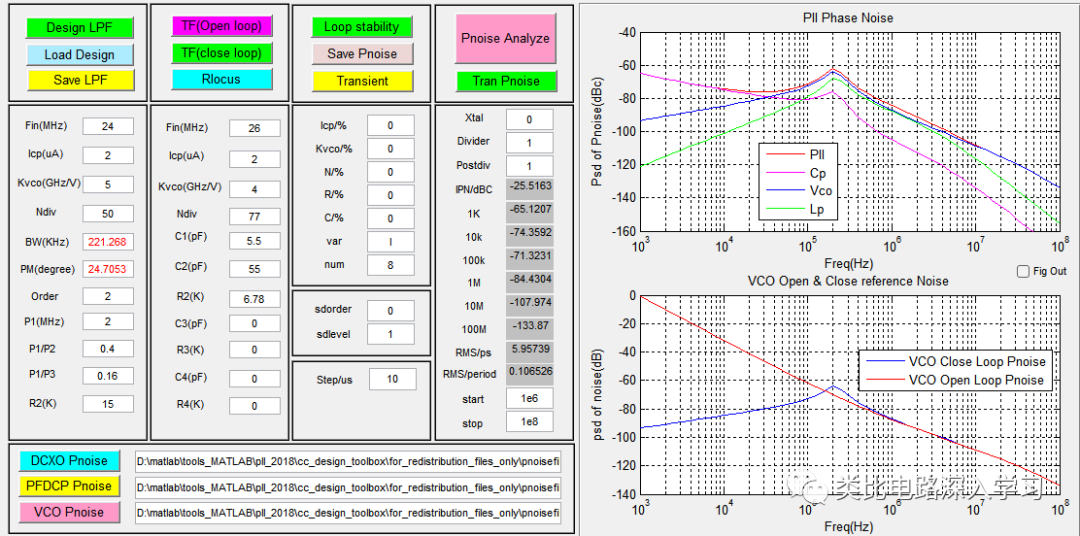

上述參數(shù)利用pll_tool進行驗證,其中各模塊的噪聲取設計中的典型值。

N=4/17.5/77

N=17.5

1)環(huán)路帶寬和相位裕度分別為,560KHz和45.9°

2)period jitter rms=2.06ps@455MHz

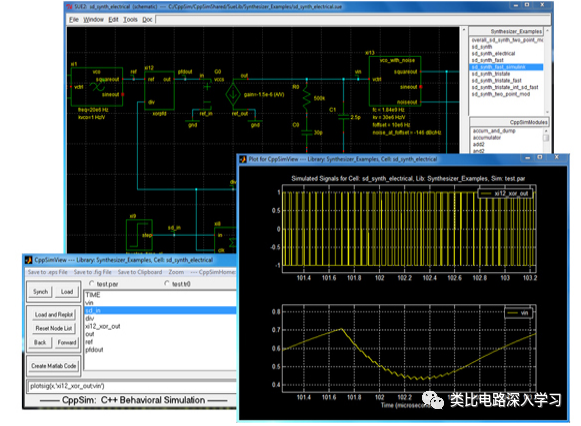

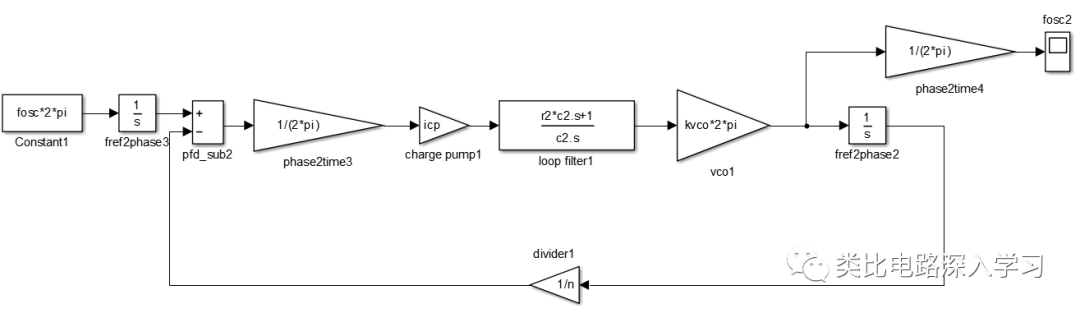

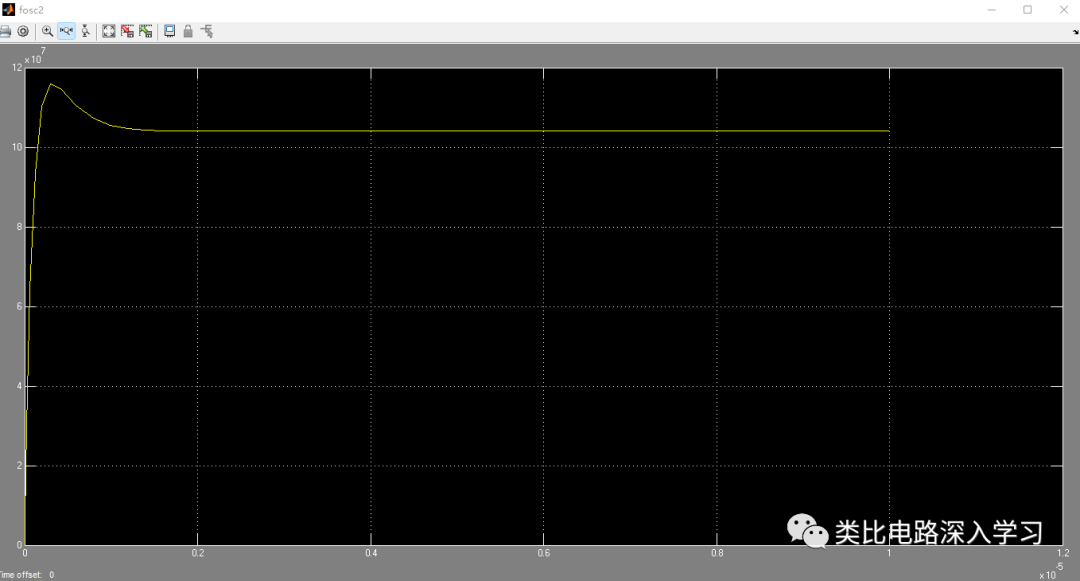

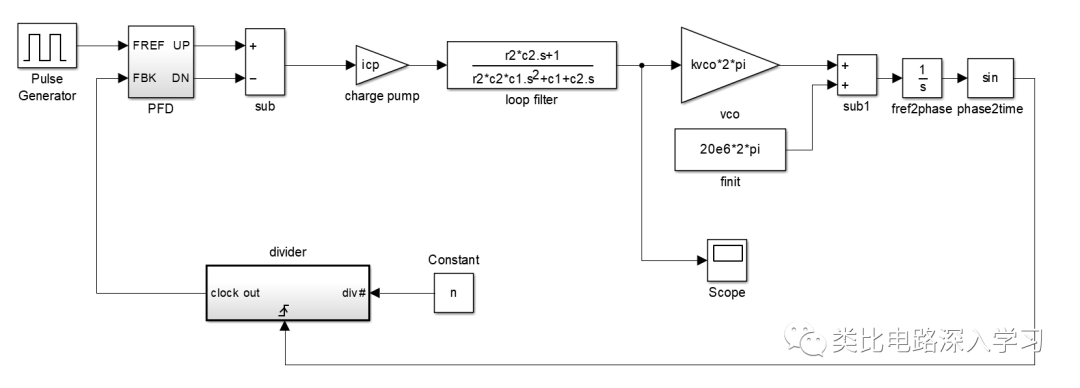

下面用matlab simulink對設計進行仿真

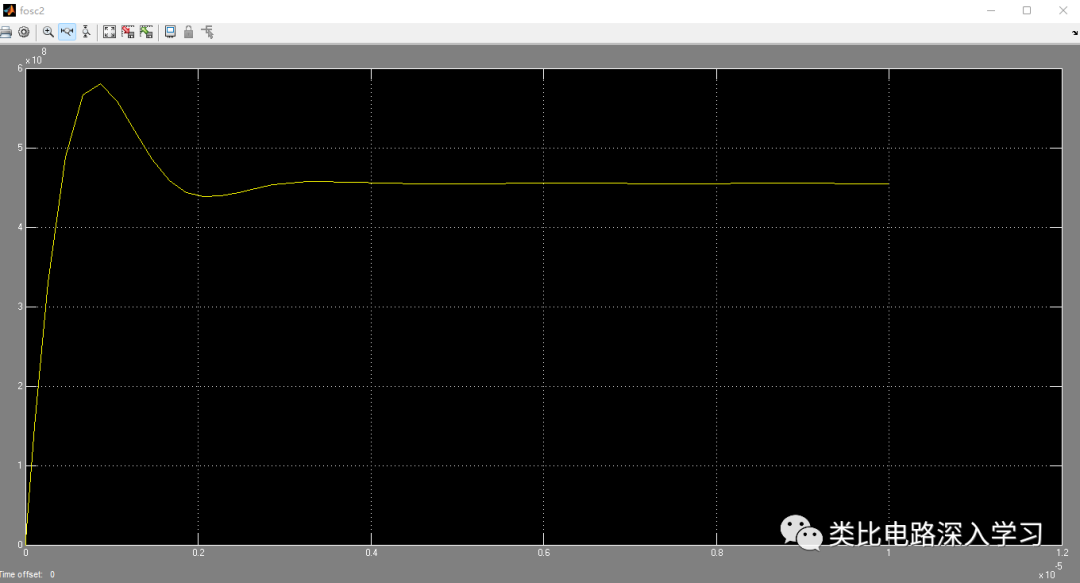

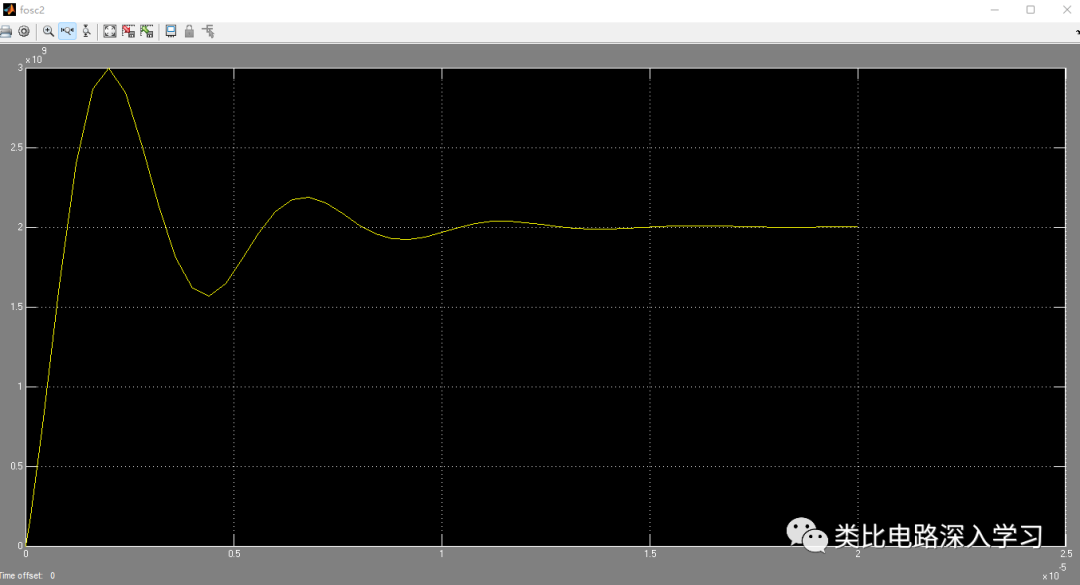

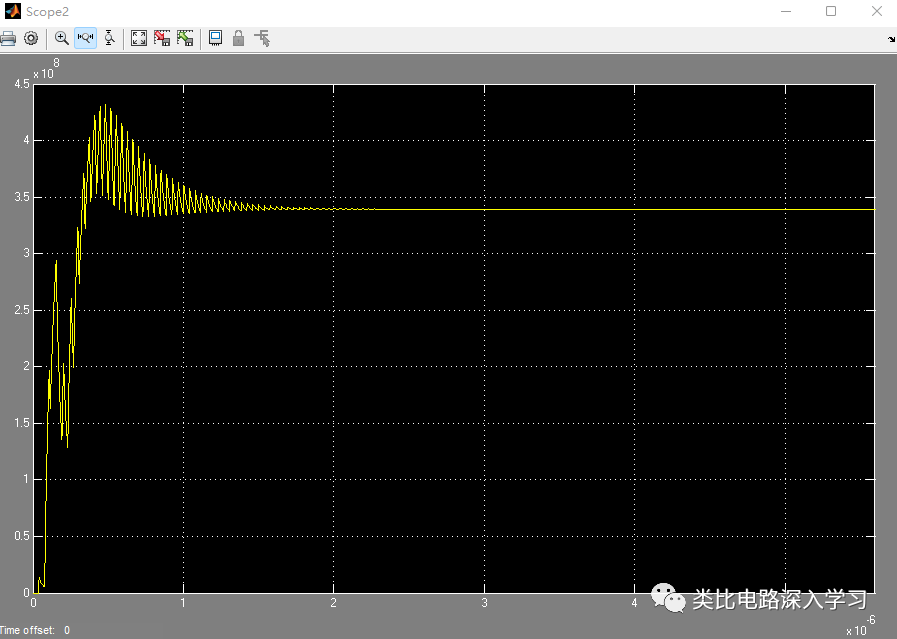

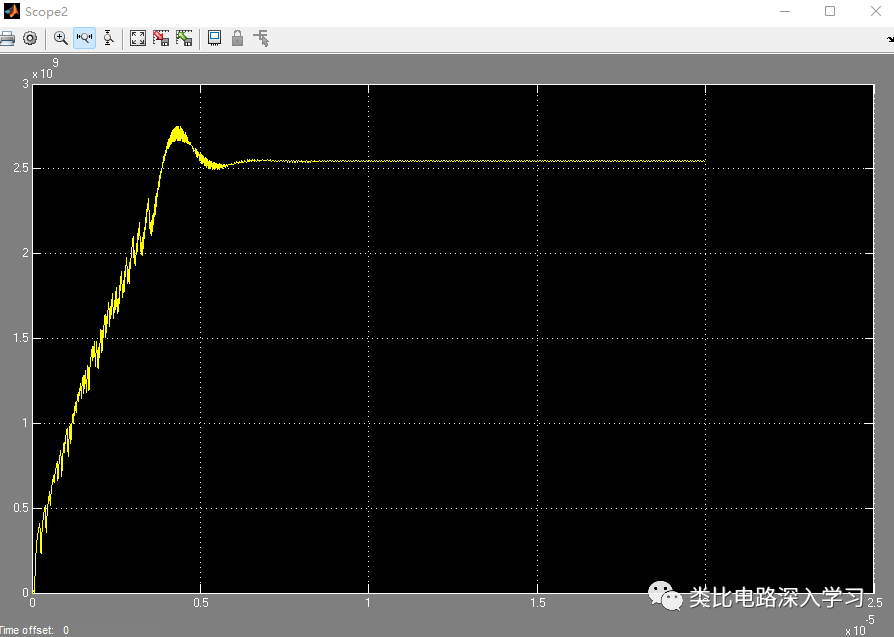

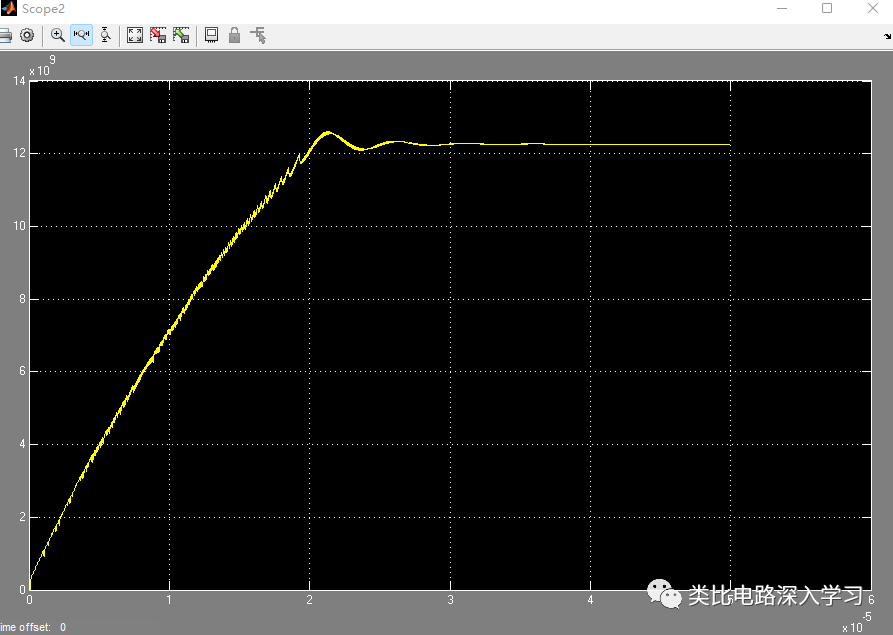

N=4/17.5/77

2)大信號模型

N=4/17.5/77

綜上,環(huán)路參數(shù)匯總?cè)缦?/p>

| 參數(shù) | 選定值 |

|---|---|

| 參考時鐘頻率FIN | 26MHz |

| 輸出時鐘頻率FOUT | 104MHz~2.002GHz |

| 環(huán)路分頻比N | 4~77 |

| 電荷泵電流Icp | 2uA |

| 壓控振蕩器的增益Kvco | 4GHz/V |

| 環(huán)路濾波器階數(shù) | 二階 |

| 環(huán)路帶寬BW | 500KHz |

| 環(huán)路相位裕度PM | 50° |

| R1 | 6.87kΩ |

| C1 | 55pF |

| C2 | 5.5pF |

-

matlab

+關(guān)注

關(guān)注

188文章

2994瀏覽量

233134 -

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

592瀏覽量

88435 -

pll

+關(guān)注

關(guān)注

6文章

880瀏覽量

136015 -

建模

+關(guān)注

關(guān)注

1文章

315瀏覽量

61405 -

仿真分析

+關(guān)注

關(guān)注

3文章

106瀏覽量

33871

發(fā)布評論請先 登錄

關(guān)于鎖相環(huán)(PLL)的工作原理

LabVIEW鎖相環(huán)(PLL)

鎖相環(huán)設計仿真與應用

鎖相環(huán)的性能,仿真和設計(第3版)

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

鎖相環(huán)(PLL)的工作原理及應用

鎖相環(huán)PLL的基礎知識

鎖相環(huán)(PLL)建模及仿真分析

鎖相環(huán)(PLL)建模及仿真分析

評論