1、組合邏輯的競(jìng)爭(zhēng)冒險(xiǎn)

組合邏輯:任何時(shí)刻電路的穩(wěn)定輸出,僅僅取決于該時(shí)刻各個(gè)輸入變量的取值。

組合邏輯的競(jìng)爭(zhēng)冒險(xiǎn):當(dāng)輸入信號(hào)同事變化時(shí),組合邏輯必然產(chǎn)生毛刺。

解決方法:用時(shí)序邏輯,每次寄存器的輸出結(jié)果取決于上一個(gè)時(shí)鐘的寄存器的值,不會(huì)產(chǎn)生毛刺。

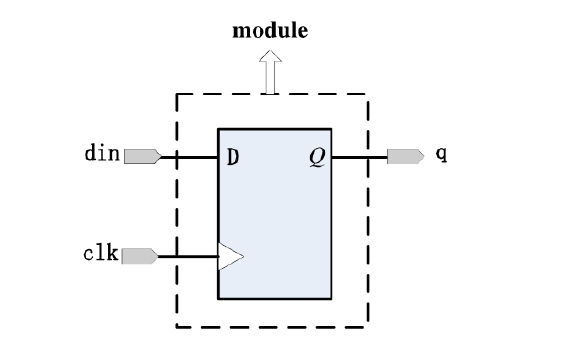

2、寄存器reg可以用在時(shí)序邏輯也可以用在組合邏輯

時(shí)序邏輯就是平時(shí)寫的clk觸發(fā)

組合邏輯例如always@(b) out1 =~ b;

觸發(fā)器具有記憶性原因:普通的門電路輸出信號(hào)只取決于當(dāng)前輸入信號(hào),無記憶性,但是觸發(fā)器

的輸出還和之前的狀態(tài)有關(guān),比如JK觸發(fā)器:Qn+1 = JQn_ + K_Qn

3、時(shí)序,組合邏輯,阻塞與非阻塞區(qū)別

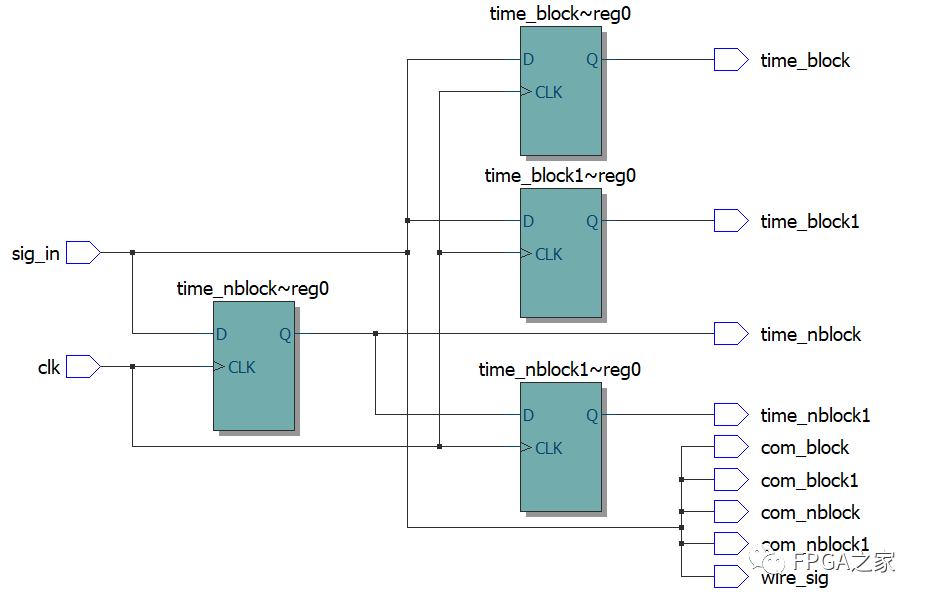

//time 非阻塞 always @(posedge clk) begin time_nblock <= sig_in; time_nblock1 <= time_nblock; end //time 阻塞 always @(posedge clk) begin time_block = sig_in; time_block1 = time_block; end //combine 非阻塞 always @(*) begin com_nblock <= sig_in; com_nblock1 <= com_nblock; end //combine 阻塞 always @(*) begin com_block = sig_in; com_block1 = com_block; end

綜合出來的電路

時(shí)序電路,會(huì)生成D觸發(fā)器,根據(jù)電路可以看出阻塞賦值和非阻塞賦值,一個(gè)always塊結(jié)束之后,阻塞賦值結(jié)果都是一樣的,但是非阻塞

賦值的話,是同事變化的,time_nblock得到sig的同時(shí),time_nblock1也得到time_nblock之前得值。

阻塞賦值從電路上看,非阻塞和阻塞都是一樣得,modelsim仿真也是這么個(gè)情況。

一般來說,時(shí)序邏輯用非阻塞賦值,組合邏輯用阻塞賦值。

4、與門

assignq = (al == 1) ? d : 0;

5、亞穩(wěn)態(tài)

亞穩(wěn)態(tài)定義:在進(jìn)行fpga設(shè)計(jì)時(shí),往往只關(guān)心“0”和"1"兩種狀態(tài)。然而在工程實(shí)踐中,除了”0“、”1“外還有其他狀態(tài),亞穩(wěn)態(tài)就是其中之一。

亞穩(wěn)態(tài)是指觸發(fā)器或鎖存器無法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)[1]。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無法預(yù)測(cè)該單元的輸出電平,

也無法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在亞穩(wěn)態(tài)期間,觸發(fā)器輸出一些中間級(jí)電平,甚至可能處于振蕩狀態(tài),并且這種無用的輸

出電平可以沿信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。亞穩(wěn)態(tài)是異步數(shù)字電路設(shè)計(jì)中的固有現(xiàn)象,但是由于其偶發(fā)性和溫度敏感性的特點(diǎn),

在產(chǎn)品前期測(cè)試過程中很難發(fā)現(xiàn)。

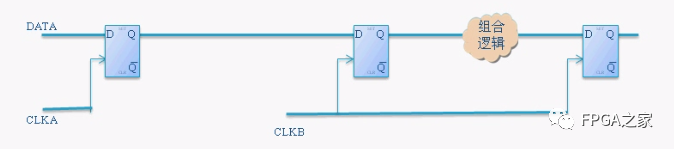

亞穩(wěn)態(tài)產(chǎn)生的原因:1、時(shí)序不滿足,例如不滿足建立時(shí)間和保持時(shí)間。

2、不同時(shí)鐘域接口

例如當(dāng)數(shù)據(jù)剛傳過來的時(shí)候,clkb恰好來了一個(gè)上升沿

亞穩(wěn)態(tài)的解決方法:1、單比特信號(hào)打兩拍寄存器,我看網(wǎng)上亞穩(wěn)態(tài)有一個(gè)震蕩周期,如果震蕩周期大于一個(gè)時(shí)鐘的話那么一級(jí)緩存之后仍然會(huì)有亞穩(wěn)態(tài)

現(xiàn)象,所以兩級(jí)緩存就比較靠譜了。

2、多比特信號(hào)fifo

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123338 -

Verilog

+關(guān)注

關(guān)注

28文章

1366瀏覽量

111818 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61878 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

6144

原文標(biāo)題:verilog知識(shí)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

哪有FPGA的verilog編程基礎(chǔ)知識(shí)?

Verilog HDL練習(xí)題和Verilog基礎(chǔ)知識(shí)適合verilog新人

介紹關(guān)于編程的基礎(chǔ)知識(shí)

介紹PLC的原理及基礎(chǔ)知識(shí)

Verilog HDL基礎(chǔ)知識(shí)

Verilog_HDL基礎(chǔ)知識(shí)非常好的學(xué)習(xí)教程 (1)

Verilog教程之Verilog HDL數(shù)字集成電路設(shè)計(jì)方法和基礎(chǔ)知識(shí)課件

Verilog的基礎(chǔ)知識(shí)

Verilog HDL的基礎(chǔ)知識(shí)

verilog基礎(chǔ)知識(shí)介紹

verilog基礎(chǔ)知識(shí)介紹

評(píng)論