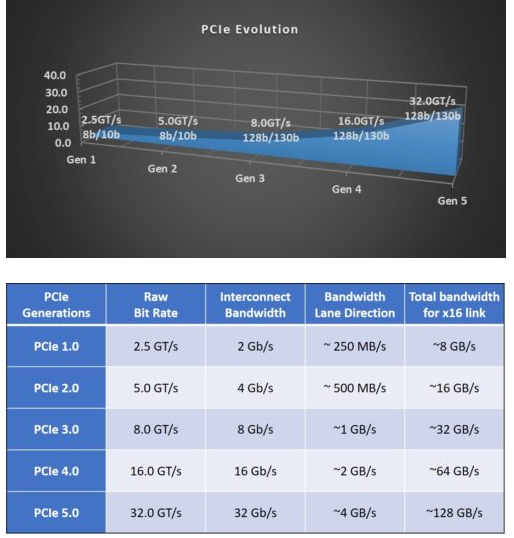

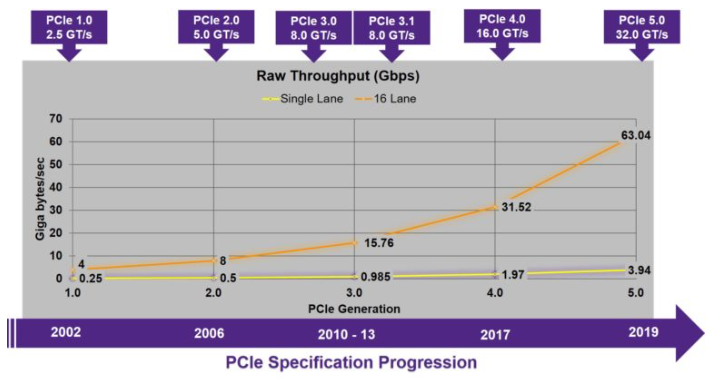

PCI Express 0.32規(guī)范將比特率提高一倍,達(dá)到每通道128GT/s,為x16 Link(16通道)提供約<>GB/s的帶寬。下圖提供了不同 PCIe 代的比特率和帶寬的比較。

PCIe 物理層在以 128.130 GT/s 數(shù)據(jù)速率運(yùn)行時(shí)將使用 32b/0b 編碼。此新數(shù)據(jù)速率將與先前的數(shù)據(jù)速率向后兼容。PCIe 鏈路將以 0.2 GT/s 的速度訓(xùn)練到 L5 狀態(tài),就像以前一樣,然后移動(dòng)到更高的數(shù)據(jù)速率。采用 1b/2b 編碼和 8b/10b 編碼的 TS128 和 TS130 有序集得到增強(qiáng),包括 32.0 GT/s 數(shù)據(jù)速率支持。均衡階段類似于上一代 8.0 GT/s 和 16.0 GT/s 數(shù)據(jù)速率。在以 0.2 GT/s 的速度對 L5 進(jìn)行初始鏈路訓(xùn)練后,鏈路將以 8.0 GT/s 的速度執(zhí)行均衡,然后依次執(zhí)行 16.0 GT/s 和 32.0 GT/s 均衡。當(dāng)支持 32.0 GT/s 時(shí),以較低的數(shù)據(jù)速率跳過(或重新排序)均衡是一項(xiàng)可選功能。除了跳過均衡的此選項(xiàng)外,還將通過鏈路訓(xùn)練協(xié)商備用協(xié)議。

采用 128b/130b 編碼的 ElEOS 有序集擴(kuò)展為包括更長的 0 和 1 運(yùn)行長度。 在 32.0 GT/s 時(shí),添加了另外 19 組具有各種預(yù)設(shè)的順應(yīng)性模式。添加了新的擴(kuò)展功能結(jié)構(gòu)和幾個(gè)寄存器字段,以容納32.0 GT/s的數(shù)據(jù)速率。對于 32.0 GT/s 的數(shù)據(jù)速率,接收器和重定時(shí)器的通道裕量支持預(yù)計(jì)不會改變。

審核編輯:郭婷

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123400 -

PCI

+關(guān)注

關(guān)注

5文章

678瀏覽量

131450 -

PCIe

+關(guān)注

關(guān)注

16文章

1324瀏覽量

84703

發(fā)布評論請先 登錄

基于C的測試和驗(yàn)證套件集成到常規(guī)UVM測試平臺的方法

如何使用Xilinx AXI VIP對自己的設(shè)計(jì)搭建仿真驗(yàn)證環(huán)境的方法

Synopsys為更快速的SoC驗(yàn)證推出下一代驗(yàn)證IP

基于FPGA的PCIe總線接口的DMA控制器的實(shí)現(xiàn)并進(jìn)行仿真驗(yàn)證

Synopsys為Arm AMBA CXS的VIP提供EDA驗(yàn)證解決方案

4-AMBA VIP 編程接口

開始使用AXI VIP,對UVM有一些基本的了解

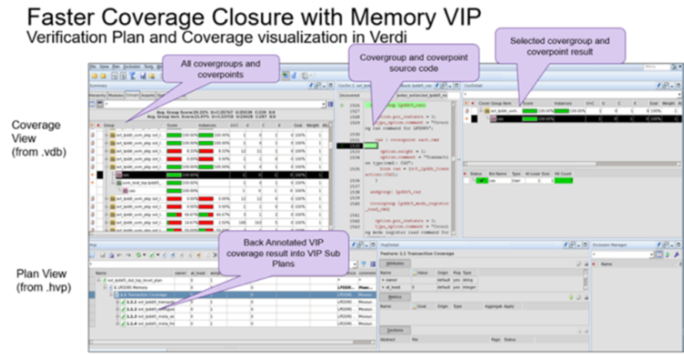

覆蓋模型 – 填補(bǔ)內(nèi)存VIP的漏洞

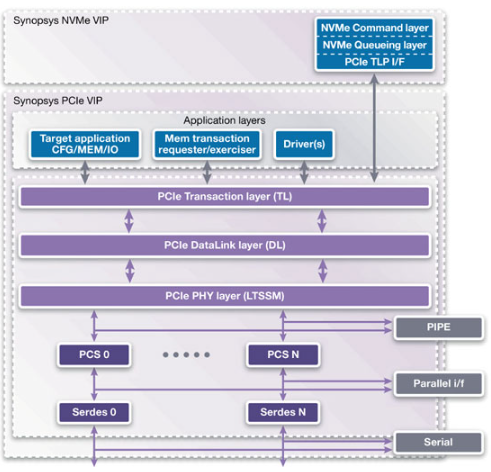

使用Synopsys VIP簽署PCIe 5.0驗(yàn)證

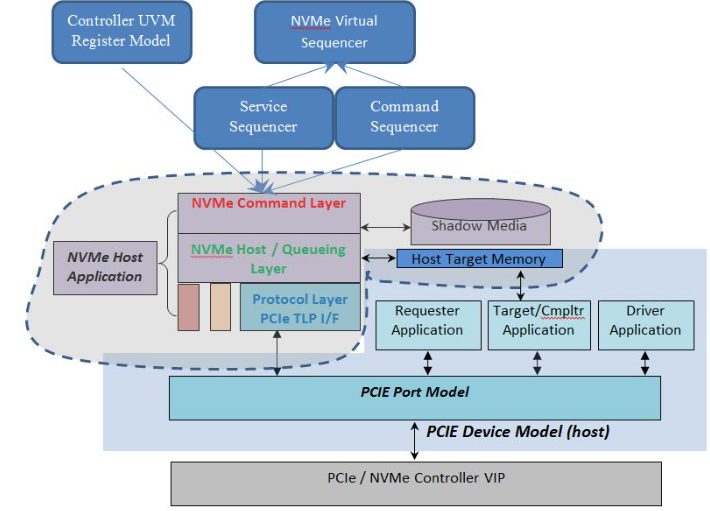

NVMe VIP:驗(yàn)證功能

新思科技NVMe VIP:高層次視圖

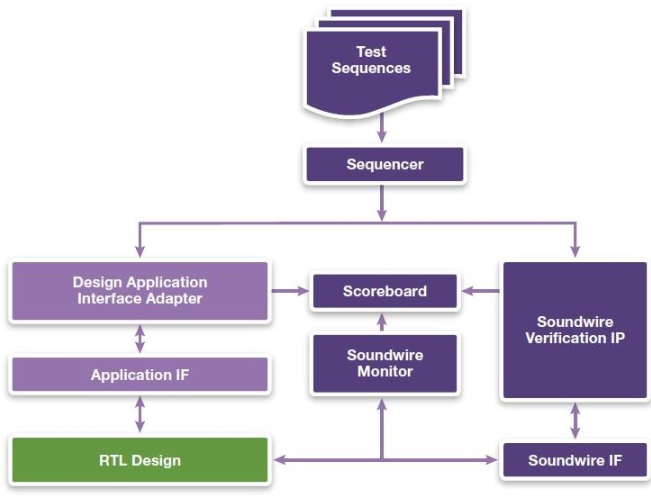

MIPI聲線測試套件

AMD如何將Synopsys AI驗(yàn)證工具用于測試

三星電子采納新思科技Synopsys.ai EDA套件,完成GAA制程驗(yàn)證

新思科技VSO.ai如何顛覆芯片驗(yàn)證

使用Synopsys VIP和測試套件進(jìn)行驗(yàn)證

使用Synopsys VIP和測試套件進(jìn)行驗(yàn)證

評論