買電腦時誰不想要個大內存呢,其他電子產品的存儲器需求也是如此。大存儲器對于像自動駕駛和智能設備這類被AI和ML技術加持的高性能計算應用則更加重要,因為它們通常需要實時計算結果,這個數據量可想而知。隨著這類數據密集型應用日益普及,芯片開發者需要快速生成衍生設計和不同版本,才能更好地滿足終端用戶需求。

因此,存儲器件變得容量越來越大,設計越來越復雜。在開發存儲器件時,怎樣做才能既滿足嚴苛的性能、功耗、面積(PPA)目標,又能確保產品按時上市呢?

先進的存儲器設計需要不一樣的開發流程

當今的存儲器會更多地采用2.5D/3D結構的multi-die設計,這類架構十分具有挑戰性。

以完整的存儲器陣列為例,在設計先進的高帶寬(HBM)DRAM或3D NAND閃存芯片時必須要考慮晶粒之間的互連以及電源分配網絡(PDN),以便針對PPA和硅可靠性進行優化。

傳統的存儲器設計和驗證技術已經無法支持先進的存儲器件設計了。仿真大型陣列非常耗時,并且由于周轉時間過長,會導致產品上市延遲。另外,在流程后期發現設計問題時,解決問題需要使用手動迭代循環,還會進一步導致延遲。

存儲器設計和驗證過程的“前移”是應對上述挑戰的唯一方法。存儲器設計前移讓開發者們可以更早地執行更好的分析,避免流程后期出現意外,并最大限度地減少迭代。

通過前移還可以避免存儲器開發中影響整體周轉時間和上市時間的四個關鍵瓶頸:宏單元特征提取、模塊設計優化、版圖前到版圖后的仿真差距,以及定制版圖設計。首先來逐一探討下這四個瓶頸。

AI+ML,打破存儲器設計瓶頸

瓶頸1:宏單元特征提取

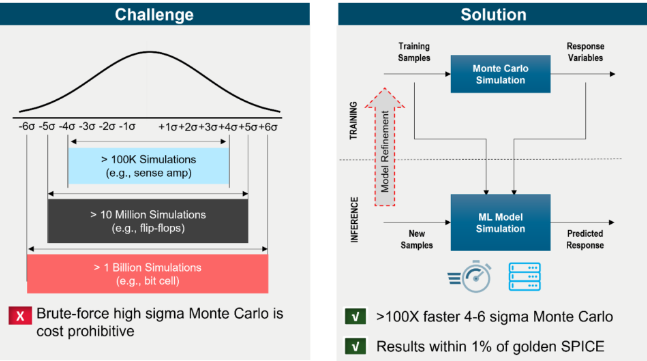

存儲器宏單元特征提取需要蒙特卡洛仿真,但在設計先進的存儲器時,執行詳盡蒙特卡洛仿真所需的時間和資源會大大增加,這使得其成為一個難以實現的解決方案。為了實現高西格瑪特征提取并確保設計的穩健性,需要運行數十億次的仿真。

機器學習技術恰好可以在這方面發揮作用。高精度的設計替代模型經過訓練,能夠預測高西格瑪電路行為。通過采用該模型,可以顯著減少仿真運行次數。

根據公開的案例分析,與傳統方法相比,這種方法可以實現100-1000倍的加速,同時能夠提供精度在1%以內的黃金SPICE結果。

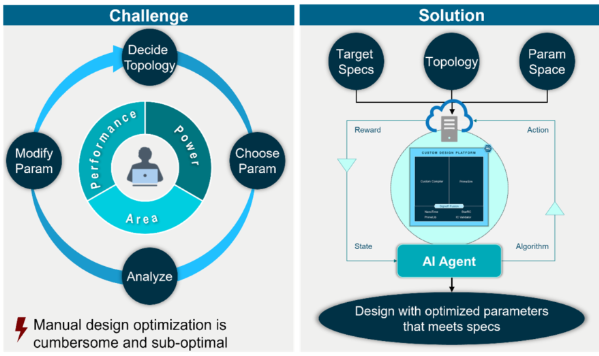

瓶頸2:模塊設計優化

在存儲器設計項目中,導致周轉時間和上市時間延長的主要因素是需要根據分析結果來迭代更改設計。傳統的流程是,先決定拓撲結構,再選擇晶體管尺寸和R/C值等設計參數,接著對設計進行仿真,然后是檢查輸出。如果結果不符合項目的PPA目標,則必須調整參數,重新進行仿真并重新評估結果。這種手動迭代循環會占用寶貴的開發資源并導致進度延誤。

針對這一挑戰,如果機器和算法能自動優化設計,情況會怎么樣呢?

近年來,我們已經看到設計空間優化作為一個完整的人工智能驅動工作流程出現在數字設計中。人工智能代理能夠自動選擇器件參數,運行仿真,從結果中學習并進行微調,從而以迭代方式收斂到正確的器件參數集。

依靠AI驅動的設計優化,可以顯著減少手動工作,更快地實現設計目標,速度提升好幾個數量級。

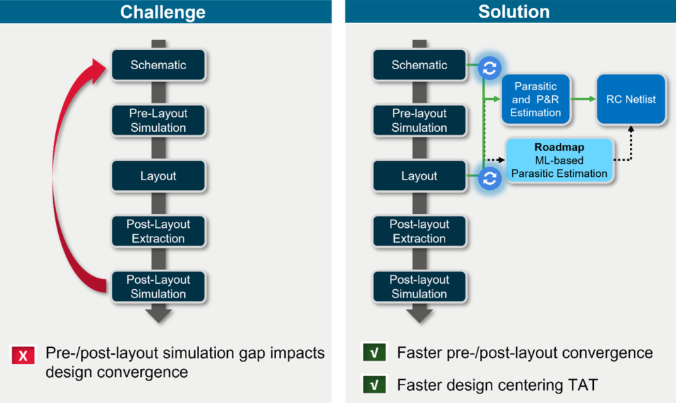

瓶頸3:版圖前到版圖后的仿真差距

導致周轉時間和上市時間延長的另一個主要迭代來源是版圖前到版圖后的仿真差距。開發者希望在版圖之前盡可能準確地預先提取寄生參數對時序、功耗、噪聲和穩定性等設計規格的影響,從而避免在從版圖中提取寄生參數時出現意外。不幸的是,在傳統流程中,這些類型的意外很常見,從而導致需要重復版圖和仿真。

對此,解決辦法是什么呢?

那就是早期寄生效應分析工作流程。通過該流程,可以準確地估算預版圖和部分版圖設計中的凈寄生參數。根據公開的案例分析,通過使用早期寄生效應分析工作流程來預先提取寄生參數,可將設計中版圖前后的時序差異從20-45%降低到0-20%。

有一項新興技術在這方面表現出了巨大前景,那就是利用機器學習通過預測互連寄生效應來進一步增強早期寄生效應分析工作流程。

瓶頸4:定制版圖

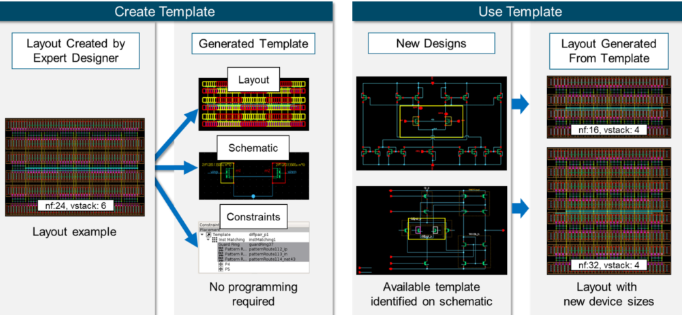

雖然加快存儲器設計的仿真和分析速度是實現設計流程前移的重要一環,但是在定制版圖階段也同樣有機會來減少花費的時間和精力。在存儲器設計中,經常會重復出現相同的子電路拓撲。這樣一來,便可以由專業開發者提取布局布線模式來創建成模板,然后其他開發者可以重復使用這些現成的模板。初級開發者可以利用這些模板,根據所需的任何設備尺寸創建新的版圖。這樣不僅可以節省時間,還可以讓初級開發者從原始版圖所體現的專業知識和經驗中受益。

根據公開的案例分析,無論開發者的經驗如何,通過創建和使用模板,存儲器中關鍵模擬電路的版圖周轉時間可以縮短50%以上,并且版圖質量會更加一致。

機器學習技術代表著版圖設計的下一個前沿,能夠實現模擬布局布線自動化,并推動版圖效率進一步提高。

實現存儲器開發前移的最佳方法

新思科技定制設計系列中提供了上述所有相關技術,能夠幫助開發者克服這四個主要的存儲器設計和驗證瓶頸。

新思科技PrimeSim?連續電路仿真技術提供了機器學習驅動的高西格瑪蒙特卡洛仿真和一致的工作流程,消除了點工具流程中固有的麻煩和不一致。

與新思科技PrimeWave?設計環境相結合,PrimeSim解決方案還能提供早期寄生效應分析。此外,新思科技Custom Compiler?設計和版圖解決方案全面支持基于模板的設計再利用。

結語

芯片的每一次更新換代,都意味著存儲器設計和驗證會變得愈加具有挑戰性。新思科技擁有所有相關技術,助力開發者們實現存儲器設計前移,縮短周轉和上市時間,并實現開發者們所期望的PPA。

審核編輯:郭婷

-

存儲器

+關注

關注

38文章

7637瀏覽量

166453 -

人工智能

+關注

關注

1804文章

48736瀏覽量

246659 -

ML

+關注

關注

0文章

150瀏覽量

34978

發布評論請先 登錄

使用tina測量opa227的輸入失調電壓和失調電流,結果數量級和手冊標準值差很多,為什么?

抗輻射加固封裝國產存儲器的電子輻照試驗

使用Matlab捕獲N9010A跟蹤數據縮放了幾個數量級

請問AD9361跳頻穩定時間是一個什么數量級?

開關電源的NTC阻值一般是什么數量級的?

如何實現處理器的速度跟外圍硬件設備的速度在一個數量級上呢

傳感器檢測精度再度提高,檢測精度和分辨率提升了2個數量級

AI賦能下的當下與未來,人臉識別的準確度已經提升了4個數量級

存儲創新技術正煥發著勃勃生機

中國電子系統2天時間建設蘇州市疫情管控平臺 可同時支持10萬數量級企業及1000萬數量級員工的活動軌跡分析

英偉達已首次實現SDF實時渲染 速度提升2-3個數量級

兼顧PPA和上市時間,機器學習讓存儲器設計提速N個數量級

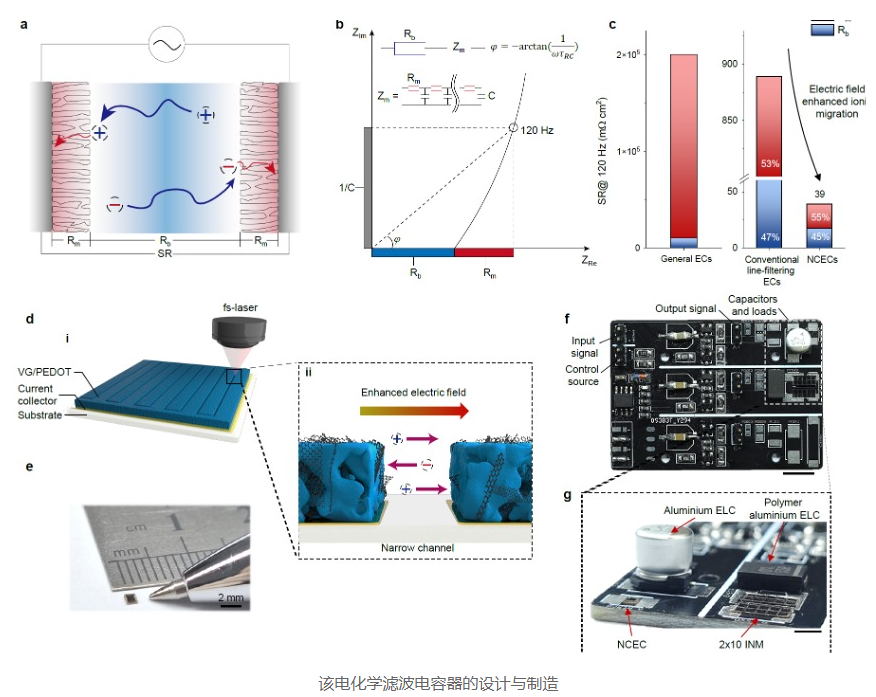

清華電化學電容新突破,比容量高出電解電容兩個數量級

機器學習讓存儲器設計提速N個數量級

機器學習讓存儲器設計提速N個數量級

評論