隨著數字技術的快速發展,數字信號處理已深入到各個學科領域。在數字信號處理中,許多算法如相關、濾波、譜估計、卷積等都可通過轉化為離散傅立葉變換(DFT)實現,從而為離散信號分析從理論上提供了變換工具。但DFT計算量大,實現困難。快速傅立葉(FFT)的提出,大大減少了計算量,從根本上改變了傅立葉變換的地位,成為數字信號處理中的技術之一,廣泛應用于雷達、觀測、跟蹤、高速圖像處理、保密無線通信和數字通信等領域。

目前,硬件實現FFT算法的方案主要有:通用數字信號處理器(DSP)、FFT專用器件和現場可編程門陣列(FPGA)。DSP具有純軟件實現的靈活性,適用于流程復雜的算法,如通信系統中信道的編譯碼、QAM映射等算法。DSP完成FFT運算需占用大量DSP的運算時間,使整個系統的數據吞吐率降低,同時也無法發揮DSP軟件實現的靈活性。采用FFT專用器件,速度雖能夠達到要求。但其外圍電路復雜,可擴展性差,成本昂貴。隨著FPGA發展,其資源豐富,易于組織流水和并行結構,將FFT實時性要求與FPGA器件設計的靈活性相結合,實現并行算法與硬件結構的優化配置,不僅可以提高處理速度,并且具有靈活性高。開發費用低、開發周期短、升級簡單的特點。針對某OFDM系統中FFT運算的實際需要,提出了基于FPGA的設計來實現FFT算法,并以16位長數據,64點FFT為例,在QuartusⅡ軟件上通過綜合和仿真。

2 FFT原理及算法結構

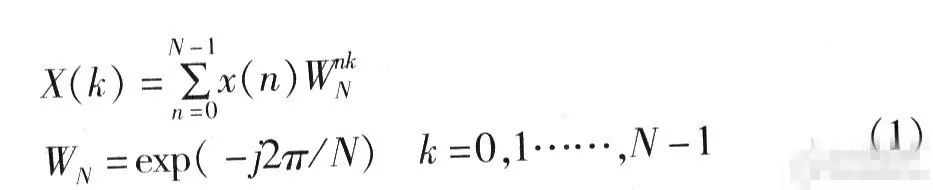

FFT是離散傅立葉變換(DFT)的快速算法。對于N點離散的有限長時問序列x(n),其傅里葉變換為:

完成N點的DFT需要N2次復數乘法和N(N-1)次復數加法。點數大時,計算量也大,所以難以實現信號的實時處理。FFT的基本思想是利用旋轉因子WN的周期性、對稱性、特殊性以及周期N的可互換性,將長度為N點的序列DFT運算逐次分為較短序列的DFT運算,合并相同項,大大減少了計算量。

FFT算法分為兩大類:一類是針對N=2的整數次冪的算法,如基2算法、基4算法、實因子算法和分裂算法等:另一類是N≠2的整數次冪算法,以winograd為代表的一類算法。硬件實現時,不僅要考慮算法運算量的大小,而且要考慮算法的復雜性和模塊化。控制簡單、實現規整的算法在硬件系統中要優于僅降低運算量的算法。現有FFT算法的FPGA設計方案基本上都是針對于類算法,而第二類算法盡管有其重要的理論價值,但硬件不易實現。由于該設計點數不是太多,綜合考慮FFT處理器的面積和成本。所以采用按時間抽取的基2快速傅立葉算法(基2DIT-FFT)。

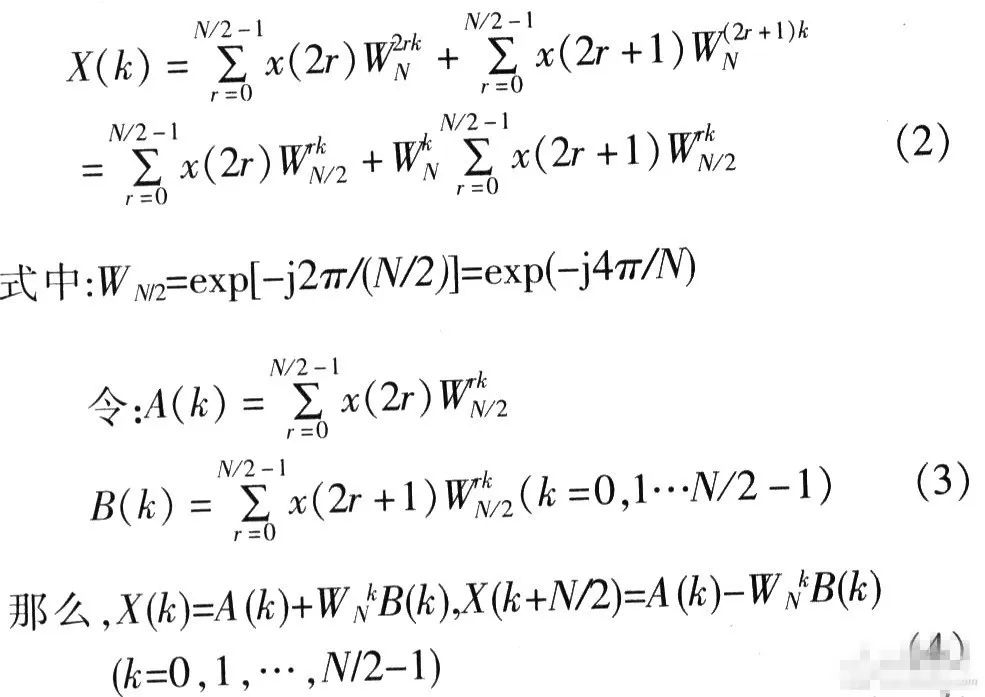

對于長度為N=2m的序列x(n),其中m是整數,將x(n)按奇偶分成兩組,即令:n=2r和n=2r+1,而r=0,1,…,N/2-1,于是:

所以A(k)和B(k)可完整表示X(k)。依次類推,可一直向前追溯到2點的FFT,這樣整個N點的FFT算法分解成log 2N級運算,每級有N/2個基2碟形運算。圖1是N=8的DIT-FFT運算流圖。

3 FFT處理器的結構設計

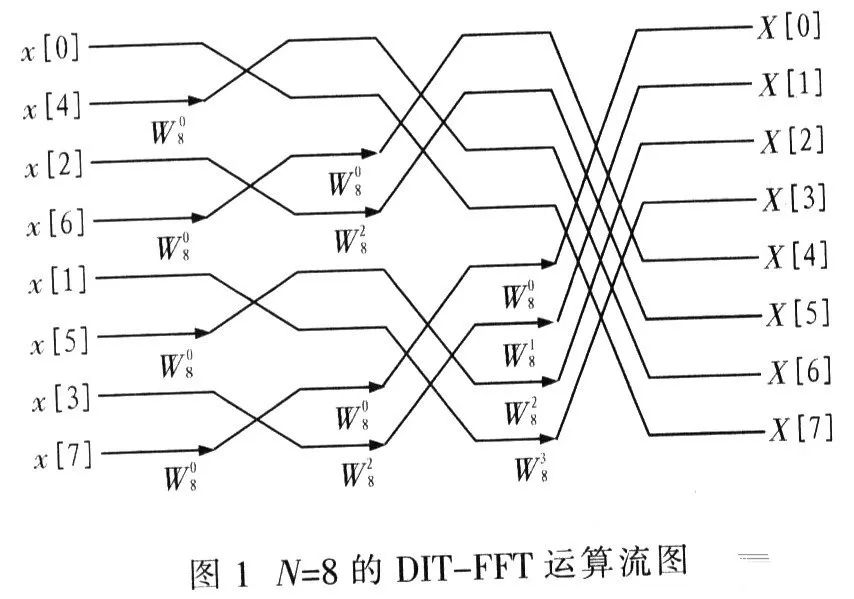

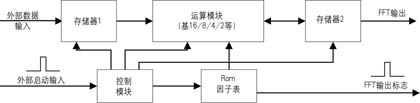

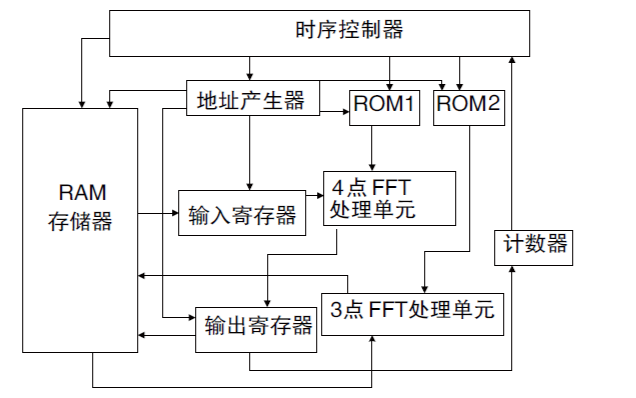

FFT實現的設計方案有順序處理、級聯處理、并行處理和陣列處理。順序處理每次運算僅用一個蝶形單元,處理方式簡單,運算速度較慢。級聯處理、并行處理和陣列處理的速度較快,但占用資源較多。考慮到該設計運算點數較少,因此采用改進的順序處理方案,在原有順序處理的基礎上對FFT處理過程中數據傳輸進行控制。使得該結構在繼承原有順序處理電路簡單、占用資源較少優點同時又兼有級聯處理運算速度較快的優點。采用自頂向下的方法對處理器模塊化,其結構框圖如圖2所示。

4 模塊設計與綜合仿真

整個FFT處理器是由存儲器、蝶形運算單元、旋轉因子單元、控制單元和數據控制單元組成,各個單元通過控制單元產生的控制和使能信號進行工作。

4.1 蝶形運算單元

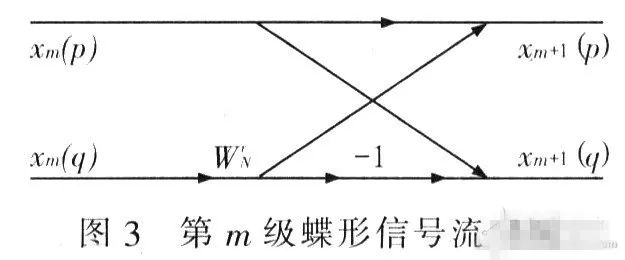

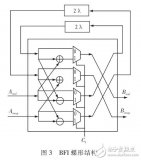

蝶形運算單元是整個FFT處理單元的重要部分,直接影響整個FFT單元性能。基2時間抽取的蝶形信號流程圖如圖3所示,p和q為數據序號,xm(p))和xm(q)是第m級蝶形運算的輸入,xm+1(p)和xm+1(q)是該蝶形運算的輸出,WrN為相應的旋轉因子。

采用FPGA實現FFT算法

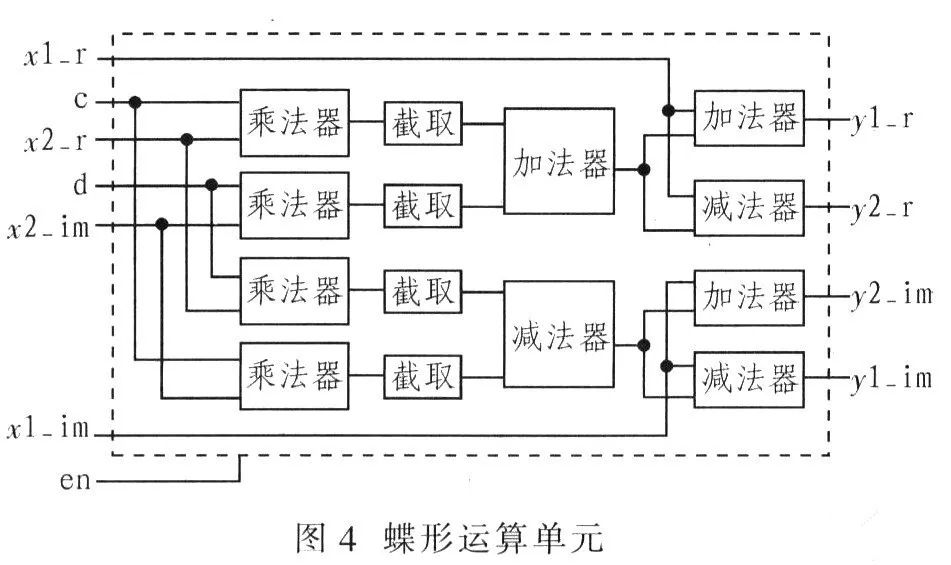

由上式看出,一個基2蝶形運算要進行1次復乘、2次復加。為了提高運算速度采用并行運算,采用4個實數乘法器、3個實數加法器和3個實數減法器組成。設輸入數據:x1=x1_r+jx1_im,x2=2_r+jx2_im,旋轉因子為WrN=c-jd,則輸出y1=y1_r+jy1_im和y2=y2_r+jy2_im。實現蝶型運算單元如圖4所示。

數據格式選擇定點16位二進制補碼。設計時必須考慮乘法器速度,將會直接影響整個FFT處理單元的運算速度,該設計的乘法器利用QuartusⅡ開發軟件中所提供的宏單元生成。乘法器的兩輸入均為16位,輸出32位。因為乘法器中帶有旋轉因子項.所以乘法運算后不應改變輸入的幅值即乘法器的輸出仍為16位,因此要對輸出數據進行截取,截取其中16位作為加(減)法器的輸入。

4.2 存儲單元

在FFT處理單元中存儲器是必不可少的單元,蝶形運算數據的輸入輸出和中間結果的存儲都要經過存儲器,因此它們的頻繁讀寫操作對整個FFT處理速度影響較大。圖2中存儲器A和存儲器B由RAM和狀態機組成,各自分別具有數據總線、地址總線和觸發時鐘。存儲器A接收外部輸入數據,存儲器B是中間結果單元,除級蝶形運算外每級數據的輸入輸出均經過該存儲器。在兩塊存儲器和蝶形運算模塊之間加入兩個數據控制器配合工作,可以在寫入上一組中間結果的同時讀取下一組蝶形運算數據,從而提高FFT的處理速度。

4.3 旋轉因子單元

旋轉因子單元是用于存儲FFT運算所需的旋轉因子WrN=exp(-j2πr/N)。在Matlab中旋轉因子分為實部和虛部產生,由于它們是小于1的小數,故在設計中需將其定點化。其過程是將旋轉因子擴大214倍。取整數部分轉化為16位定點數,以.hex文件格式保存,利用QuartusⅡ軟件的Megawizard工具設計。ROM,并將.hex文件同化在其中。根據旋轉因子的對稱性和周期性,在利用ROM存儲旋轉因子時,可以只存儲旋轉因子表的一部分,通過地址的改變查詢出每級蝶形運算所需的旋轉因子。

4.4 控制單元

控制單元用于協調驅動各模塊,在FFT運算中具有關鍵作用。存儲器A、旋轉因子單元及數據控制器的讀信號,存儲器B的讀寫信號都是由控制單元產生。控制單元通過一個有限狀態機(FSM)實現,使用兩個內部計數器控制狀態機的翻轉。控制單元具有單獨的輸入時鐘,可產生相應的控制信號。

4.5 綜合仿真

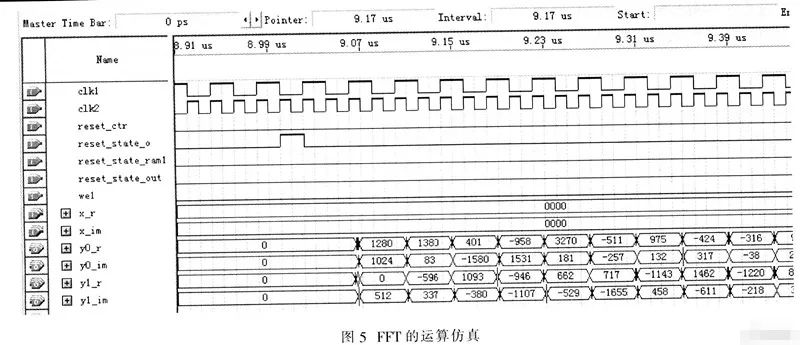

選用Altera公司的QuartusⅡ軟件作為開發平臺,以Stratix系列中的EP1S25型FPGA為器件,采用白頂向下的設計思路和VHDL語言,實現對各個模塊單元的設計、綜合和仿真。為了簡化設計,只在數據輸入時鐘下輸入了一組64個復數,其余輸入設為0,并且實部和虛部都限定在±l,±2,±3,±4,e5之內。為防止溢出先將輸入數據乘以一定比例因子2-9,再乘以2 15轉化為十六進制數。輸出的結果如圖5所示。需要注意的是:仿真結果乘以2 -6后才是實際結果。將仿真結果與Matlab計算的結果相比較,數據基本一致,說明了設計正確,其誤差主要于數據的截取和旋轉因子的近似。

5 結束語

FFT算法是數字信號處理中一種重要運算,廣泛應用于雷達、觀測、跟蹤、高速圖像處理、保密無線通信和數字通信等領域。這里討論了一種基于FPGA的64點FFT處理器的設計方案,輸入數據的實部和虛部均以16位二進制數表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發平臺對處理器各個的模塊進行設計,在StraTIx系列中的EP1S25型FPGA通過了綜合和仿真,運算結果正確。采用FPGA實現FFT算法在體積、速度、靈活性等方面都具有優越性。

-

dsp

+關注

關注

555文章

8142瀏覽量

355216 -

FFT

+關注

關注

15文章

443瀏覽量

60577 -

仿真

+關注

關注

51文章

4239瀏覽量

135307 -

數字信號處理器

+關注

關注

5文章

478瀏覽量

27736

發布評論請先 登錄

基于FPGA的超高速FFT硬件實現

FFT算法的FPGA實現

基于FPGA的FFT算法硬件實現

FFT 算法的一種 FPGA 實現

用FPGA實現FFT算法

基于FPGA的FFT實現方案

基于Xilinx FPGA 實現FFT算法的電力諧波檢測的設計方案詳解

采用FPGA實現FFT算法示例

采用FPGA實現FFT算法示例

評論