BOSHIDA電源模塊 電源基礎(chǔ)知識(shí) 功率 MOSFET 工作特性

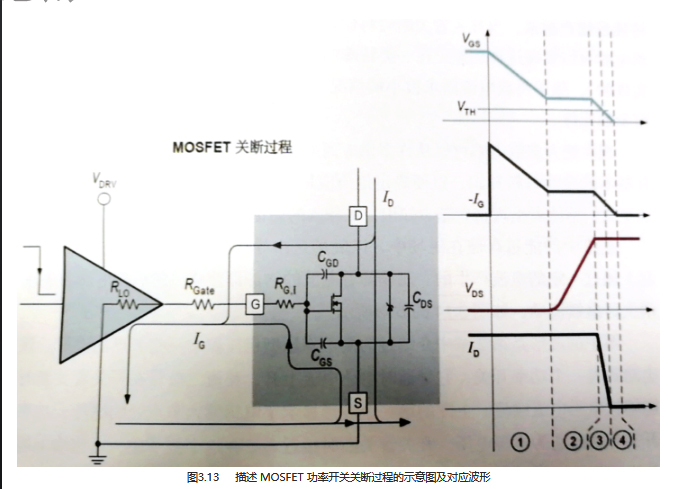

再次可以看到在關(guān)斷過程中也有類似的四個(gè)明顯不同的區(qū)間,但是它們都很大程度上受到柵極驅(qū)動(dòng)器電路特性的影響。在通常的應(yīng)用中,柵極驅(qū)動(dòng)電壓相對(duì)于柵極閾值會(huì)提高到較高水平,以便讓 MOSFET 充分導(dǎo)通得到最低的RDs(ON)。

這個(gè)高驅(qū)動(dòng)電壓提供了一個(gè)相對(duì)較大的驅(qū)動(dòng)電流,其導(dǎo)通時(shí)大小由( VDrive-VThreshold) /RGate決定。然而,在關(guān)斷時(shí),驅(qū)動(dòng)器輸出端口變成低電平,這意味著柵極驅(qū)動(dòng)電流現(xiàn)為(-VThreshold) /RGate,這通常導(dǎo)致實(shí)際開關(guān)管關(guān)斷過程緩慢。與開通相比,這些步驟仍然相同,但順序相反:

區(qū)間1 : CGs通過外部驅(qū)動(dòng)電路進(jìn)行放電,內(nèi)部柵極電壓回落到閡值電壓電平,漏極沒有任何變化。

區(qū)間2:柵極電壓開始關(guān)斷器件,CGD電容可以通過上升的漏極電壓和柵極驅(qū)動(dòng)允許的電流進(jìn)行充電。同樣,在此期間,柵極電壓和電流都保持相對(duì)恒定,流經(jīng)CGD的電流因受到RGate +RLo阻抗的影響,會(huì)減緩整個(gè)關(guān)斷過程。當(dāng)恒定的測(cè)試電流 ID 開始轉(zhuǎn)移到鉗位電路并遠(yuǎn)離MOSFET時(shí),該區(qū)間結(jié)束。

區(qū)間3:當(dāng)漏極電壓達(dá)到測(cè)試電路的鉗位電壓時(shí),CGD上的電流停止流動(dòng),柵極電壓繼續(xù)線性下降到閾值電壓,器件開始關(guān)斷。

區(qū)間4:當(dāng)柵極電壓低于閾值時(shí),MOSFET 完全關(guān)斷,柵源極間電容完全放電完成時(shí),此過程結(jié)束。

請(qǐng)注意,在此測(cè)試電路和許多SMPS應(yīng)用中,導(dǎo)通和關(guān)斷期間,漏極電壓變化時(shí)漏極電流都是一直在流動(dòng)。 這導(dǎo)致每次轉(zhuǎn)換時(shí)可能產(chǎn)生功率尖峰,一個(gè)自然的想法就是讓驅(qū)動(dòng)電路頻率變得足夠高(這樣轉(zhuǎn)換時(shí)間最小)。這是一個(gè)折中的過程,因?yàn)閷⒐β势骷械霓D(zhuǎn)換損耗減小,則需要更高的驅(qū)動(dòng)電流,這增加了驅(qū)動(dòng)電路的損耗。由于這些開關(guān)損耗在每個(gè)開關(guān)周期都產(chǎn)生,所以驅(qū)動(dòng)器件和功率開關(guān)中的總損耗隨著開關(guān)頻率線性地增加。

審核編輯:湯梓紅

-

MOSFET

+關(guān)注

關(guān)注

149文章

8225瀏覽量

218298 -

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8607瀏覽量

148968 -

電源模塊

+關(guān)注

關(guān)注

33文章

1882瀏覽量

94079

發(fā)布評(píng)論請(qǐng)先 登錄

MOSFET開關(guān)損耗計(jì)算

開關(guān)電源的基礎(chǔ)知識(shí)題目及答案(免積分)

功率器件熱設(shè)計(jì)基礎(chǔ)知識(shí)

PCB繪制基礎(chǔ)知識(shí)

射頻前端設(shè)計(jì)中的功率等級(jí)基礎(chǔ)知識(shí)

FPGA基礎(chǔ)知識(shí)及設(shè)計(jì)和執(zhí)行FPGA應(yīng)用所需的工具

Verilog HDL的基礎(chǔ)知識(shí)

功率MOSFET的開通和關(guān)斷過程原理

負(fù)載開關(guān)基礎(chǔ)知識(shí)

電源多路復(fù)用器基礎(chǔ)知識(shí)

電源基礎(chǔ)知識(shí) 功率MOSFET工作特性

電源基礎(chǔ)知識(shí) 功率MOSFET工作特性

評(píng)論