一、二進(jìn)制譯碼器

- 譯碼器定義

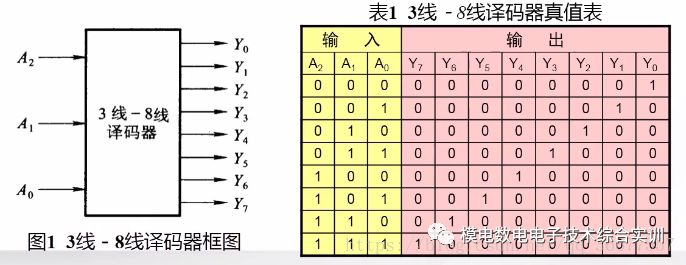

邏輯功能:將每個(gè)輸入的二進(jìn)制代碼對(duì)應(yīng)輸出為高、低電平信號(hào)。

譯碼是編碼的反操作。

常用的譯碼器有二進(jìn)制譯碼器,二-十進(jìn)制譯碼器,顯示譯碼器等。

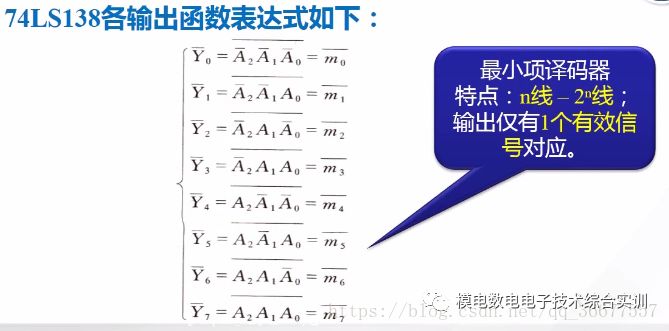

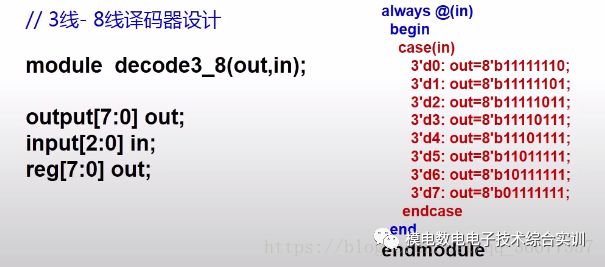

- 3線-8線譯碼器

優(yōu)點(diǎn):結(jié)構(gòu)簡(jiǎn)單,易于集成。

缺點(diǎn):電路的輸入電阻較低而輸出電阻較高;輸出的高低電平信號(hào)發(fā)生偏移(0.7V);

因此,二極管門(mén)陣列譯碼器通常用于大規(guī)模(LSI)集成電路。

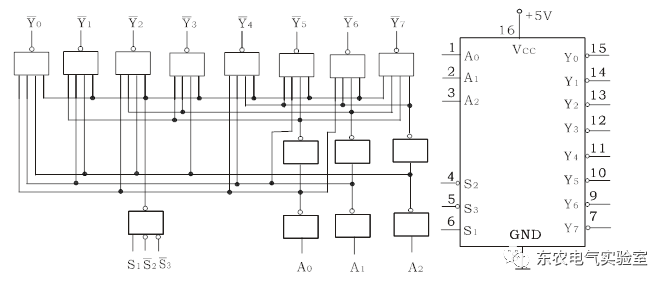

- 三極管集成二進(jìn)制譯碼器電路

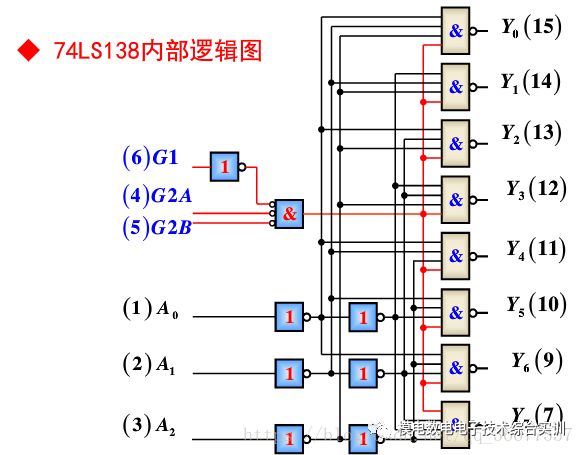

中規(guī)模(MSI)集成電路通常采用三極管集成門(mén)(如TTL)電路。

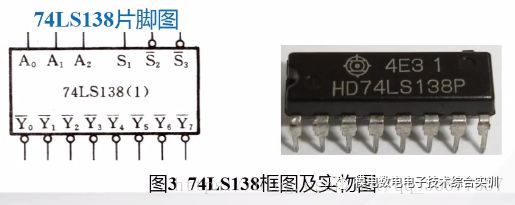

下面以74LS138,3線-8線譯碼器為例來(lái)粉刺集成譯碼器的工作原理:

-

二進(jìn)制

+關(guān)注

關(guān)注

2文章

803瀏覽量

42122 -

譯碼器

+關(guān)注

關(guān)注

4文章

312瀏覽量

50927 -

邏輯功能

+關(guān)注

關(guān)注

0文章

14瀏覽量

3186

發(fā)布評(píng)論請(qǐng)先 登錄

譯碼器的邏輯功能和使用方法

組合邏輯電路實(shí)驗(yàn)

組合邏輯電路PPT電子教案

組合邏輯3-8譯碼器的設(shè)計(jì)及實(shí)驗(yàn)

第二章_組合邏輯電路之譯碼器

第二章 組合邏輯電路之譯碼器

如何利用譯碼器進(jìn)行組合邏輯電路的設(shè)計(jì)呢

介紹在FPGA開(kāi)發(fā)板上組合邏輯電路的設(shè)計(jì)實(shí)現(xiàn)

組合邏輯電路設(shè)計(jì)實(shí)驗(yàn)

電子技術(shù)--組合邏輯電路

利用MSI設(shè)計(jì)組合邏輯電路

數(shù)字電路基礎(chǔ)之組合邏輯電路的詳細(xì)資料概述

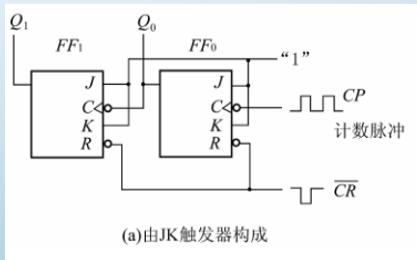

組合邏輯電路和時(shí)序邏輯電路的學(xué)習(xí)課件免費(fèi)下載

組合邏輯電路中的譯碼器介紹

組合邏輯電路中的譯碼器介紹

評(píng)論