等離子體均勻性和等離子體位置的控制在未來更加重要。對于成熟的技術節點,高的產量、低的成本是與現有生產系統競爭的關鍵因素。如果可以制造低成本的可靠的刻蝕系統,從長遠來看,可以為客戶節省大量費用,有可能促使IC制造商取代現有系統發展低成本的新系統。最關鍵的是成品率,正常運行時間應相同或高于現在的系統,而且產量更高,耗材更低,使生產商可以相信通過一年的系統更新,節省的運作成本可以還清設備成本。

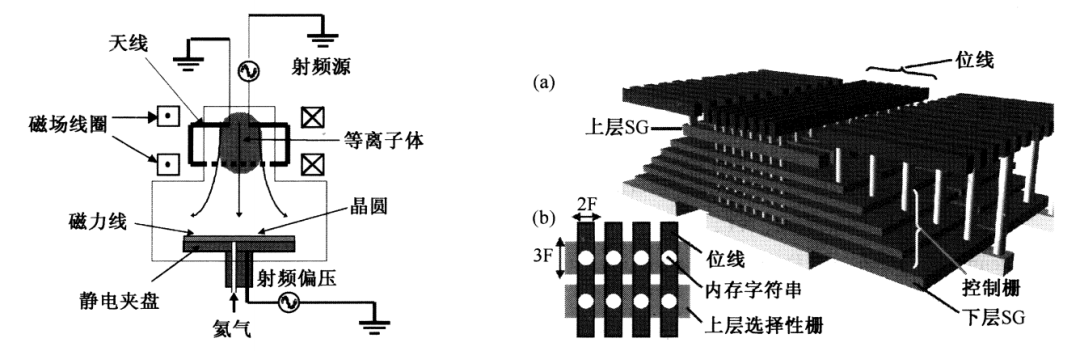

最近,新材料已被添加到IC芯片制造工藝中,如HKMG和ULK介質。這些新材料的刻蝕是刻蝕工藝面臨的挑戰之一。新器件結構,如三維FinFET器件、三維柵器件、垂直結構器件等也被應用于先進的IC芯片制造。對于三維FinFET器件,單晶硅刻蝕工藝變得越來越具有挑戰性,特別是制作在體硅襯底上的FinFET。對于先進的埋字線DRAM,刻蝕工藝需要約1:1的單晶硅和氧化硅刻蝕選擇性。進一步提高NAND快閃存儲密度的方法之一是釆用3D堆疊結構(見下圖)。下圖顯示了4層NAND快閃單元用于形成一個4位快閃存儲器。實際應用中可能需要16位字符。存儲器字符孔刻蝕工藝已經非常具有挑戰性了,而且字線接觸孔刻蝕不同深度將更加困難。如硅通孔(TSV)3D封裝工藝也對刻蝕工藝提出了更多的挑戰和機遇。不同于亞微米和納米級圖形刻蝕工藝,TSV的刻蝕工藝有較大的關鍵尺寸CD,從50um到5um,而且還需要高的刻蝕速率達到所需的產量。

本節內容回顧

1.IC芯片封裝時,需要刻蝕的4種材料是單晶硅、多晶硅、電介質(二氧化硅與氮化硅)和金屬(TiN、ALCu、Ti、W和WSi2)。

2.4種主要的刻蝕工藝是硅刻蝕、多晶硅刻蝕、電介質刻蝕和金屬刻蝕。

3.濕法刻蝕利用化學溶液溶解需要刻蝕的材料。

4.干法刻蝕利用化學氣體,經過物理刻蝕、化學刻蝕或兩種刻蝕技術的組合方式刻蝕掉襯底表面的材料。

5.濕法刻蝕具有高的選擇性、高的刻蝕速率和低成本。受等向性刻蝕輪廓的限制,濕法刻蝕不能用于圖形尺寸小于3am圖形化刻蝕工藝。

6.濕法刻蝕普遍用于先進的半導體工藝中去除薄膜并監測電介質薄膜的質量。

7.等離子體刻蝕工藝中,刻蝕劑注入反應室并在等離子體中分解。自由基將擴散到界面層并被表面吸收。在等離子體轟擊下,將和表面的原子或分子產生反應,產生的揮發性生成物從表面釋放出來,擴散穿過邊界層后,經由反應室對流作用被抽出。

8.有兩種非等向性刻蝕機制:損傷機制和阻絕機制。電介質刻蝕使用損傷機制,硅、多晶硅和金屬刻蝕使用阻絕刻蝕機制。

9.電介質刻蝕使用氟元素化學品,經常使用CF4.CHF3和AlCF4是主要的刻蝕劑,而CHF’是聚合物,可以用于改善PR和硅的刻蝕選擇性。Ar用于增強離子轟擊。O2能增加刻蝕速率。而玨可以用于改善對PR和硅刻蝕選擇性。

10.對于低左和ULK電介質刻蝕,CO可以改善刻蝕工藝的控制。

11.硅刻蝕使用HBr作為刻蝕劑,O2和氟用于側壁刻蝕。

12.多晶硅可以利用Cl2或SF6刻蝕,被用于改善氧化物的選擇性,而HBr有利于側壁沉積。

13.金屬刻蝕使用Cl2>BCl3和N2提高側壁層的鈍化作用。

14.銅金屬化不需要金屬刻蝕工藝,而是需要電介質槽形刻蝕。

15.ULK電介質刻蝕后的光刻膠去除技術越來越復雜,一般使用硬遮蔽層TiN。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52119瀏覽量

435642 -

等離子體

+關注

關注

0文章

128瀏覽量

14470 -

封裝

+關注

關注

128文章

8459瀏覽量

144722 -

制造工藝

+關注

關注

2文章

198瀏覽量

20246 -

刻蝕

+關注

關注

2文章

202瀏覽量

13315

原文標題:半導體行業(一百七十)之刻蝕工藝(二十一)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體刻蝕工藝簡述

半導體刻蝕工藝簡述

評論