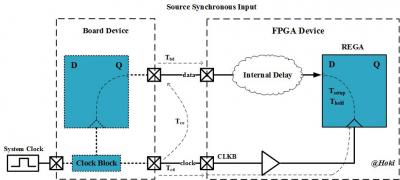

在設(shè)置input_delay時(shí),我們經(jīng)常會(huì)使用下面的方式:

set_input_delay-clockclk-min2[get_portsdata_in] set_input_delay-clockclk-max4[get_portsdata_in]

但有時(shí)也會(huì)在后面增加一個(gè)-add_delay的參數(shù):

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max1.9[get_portsdata_in]-clock_fall-add_delay set_input_delay-clockclk-min0.9[get_portsdata_in] set_input_delay-clockclk-min1.1[get_portsdata_in]-clock_fall-add_delay

在默認(rèn)情況下,一個(gè)port只需要一個(gè)min和max的dealy值,如果我們設(shè)置兩次,那么第二次設(shè)置的值會(huì)覆蓋第一次的值:下面的第一行就無效了。

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max2.5[get_portsdata_in]

但如果是加了-add_delay參數(shù),就可以多個(gè)約束同時(shí)存在:

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max2.5[get_portsdata_in]-add_delay

但其實(shí),第一行也是無效的,因此2.5比2.1要大,如果滿足2.5了,那一定滿足2.1。

因此,-add_delay參數(shù)一般都是用于雙沿采樣的場景:

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max1.9[get_portsdata_in]-clock_fall-add_delay

如果不增加-add_delay參數(shù),那么第二條會(huì)覆蓋第一條約束,那么上升沿的約束就沒有了。

在UG903中,也有下面的描述:

AddDelayInputDelayCommandOption The-add_delayoptionmustbeusedif: ?Amax(ormin)inputdelayconstraintexists,and ?Youwanttospecifyasecondmax(ormin)inputdelayconstraintonthesameport. Thisoptioniscommonlyusedtoconstrainaninputportrelativetomorethanoneclock edge,as,forexample,DDRinterface

審核編輯:劉清

-

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66342 -

ADD

+關(guān)注

關(guān)注

1文章

20瀏覽量

9560

原文標(biāo)題:set_input_delay中-add_delay的作用

文章出處:【微信號(hào):傅里葉的貓,微信公眾號(hào):傅里葉的貓】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

FPGA的IO約束如何使用

Vivado IP核心約束錯(cuò)誤的解決辦法?

保持輸入雙倍數(shù)據(jù)速率的時(shí)間錯(cuò)誤的解決辦法?

IDDR LVDS25時(shí)序違規(guī)如何改善?

input_delay應(yīng)該設(shè)置為多少?

FPGA設(shè)計(jì)約束技巧之XDC約束之I/O篇 (上)

set_max_delay被覆蓋的解決辦法

怎么解決有關(guān)于data保存時(shí)間的時(shí)序錯(cuò)誤?

STM32上進(jìn)行Delay延時(shí)的方法

詳解FPGA的時(shí)序input delay約束

set_output_delay的本質(zhì)是什么?淺談set_ouput_delay時(shí)序

set_input_delay中-add_delay的作用簡析

set_input_delay中-add_delay的作用簡析

評(píng)論