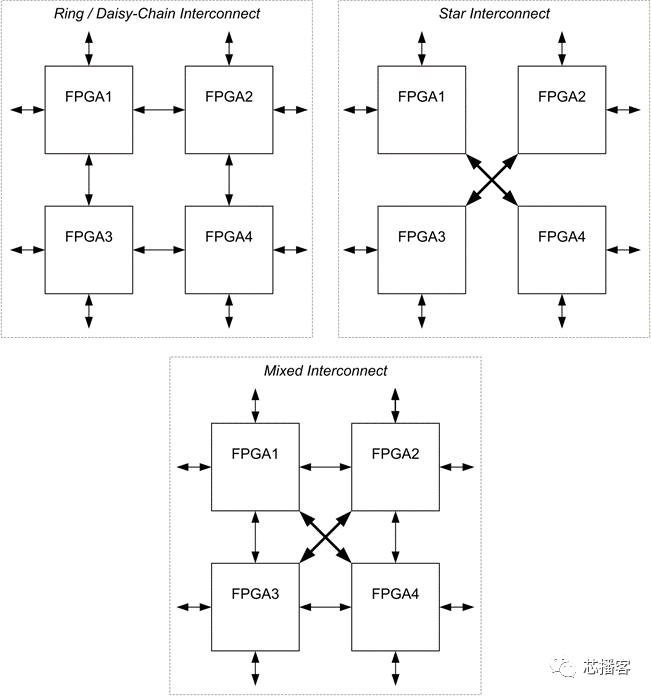

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制,通常只有1000個左右的用戶IO引腳。然后,這1000個引腳需要連接到其他FPGA或板上的外圍設備,以形成盡可能普遍適用的互連網絡,但這應該是什么樣子?引腳應該以菊花鏈環形排列的形式連接各個FPGA,還是所有FPGA引腳都應該以星形連接在一起?FPGA是否應僅鏈接到相鄰的FPGA,或者是否應做出一些規定以鏈接到更多遠程設備?

其實,每中連接方式都有優點和缺點。

菊花鏈互連要求信號通過FPGA本身以連接遠程設備。這種直通連接不僅限制了其他信號的引腳可用性,而且還顯著增加了整體路徑延遲。依賴于直通互連的電路板或系統通常比其他類型的電路板運行得更慢。然而,這樣的電路板可能適合于一種由單個寬數據路徑主導的設計,很少或沒有分支。

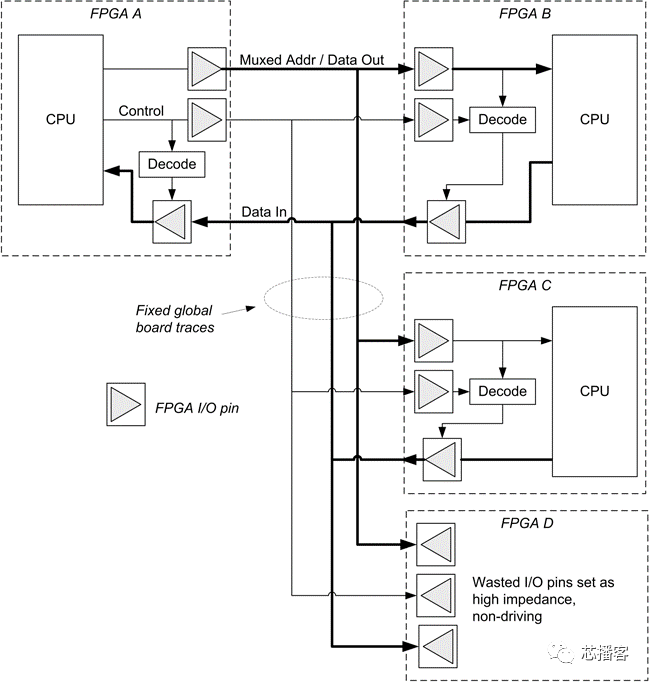

星形連接的使用可能更快,因為任何FPGA都可以通過直接導線驅動任何其他FPGA,但星形連接通常使用FPGA引腳的效率最低。如下圖所示。可以看到一個簡單的多路復用總線上的三個設計塊是如何被劃分為一個板上四個FPGA中的三個,其中板采用基于星形的固定互連。由于直接連接,三個塊之間的連接將是高速的,但第四個FPGA上的許多引腳將被浪費。

此外,這些未使用的引腳將需要配置為高阻抗,以便不干擾期望的信號。如果第四個FPGA將用于設計的另一部分,那么這種引腳浪費可能非常嚴重,并且可能會對將設計的其余部分映射到剩余資源的能力產生很大影響。

如果電路板是在內部設計和制造的,我們可以根據需要精確地安排互連,以滿足原型項目的需求。互連通常類似于SoC設計的頂層框圖,特別是當使用原型設計方法來簡化將頂層SoC塊劃分為FPGA時。這種自由度可能會為該原型項目產生最佳的互連布置,但對于后續項目來說可能是次優的。此外,如果SoC設計在發展過程中發生變化,則在原型項目開始時修復互連資源可能會導致問題。

同樣,具有固定互連的商用原型驗證板不太可能滿足給定項目的確切需求,因此需要做出妥協。典型的在許多商用原型驗證板上找到的解決方案是前面提到的直接互連布置之間的混合。 理想的互連拓撲是什么

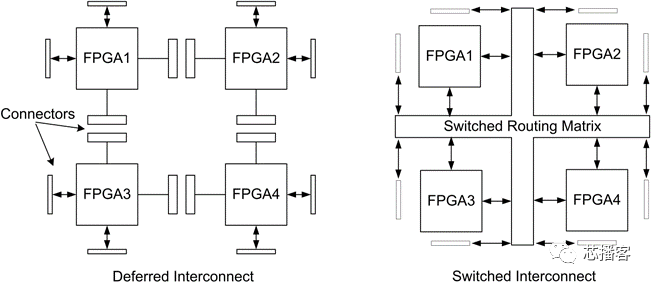

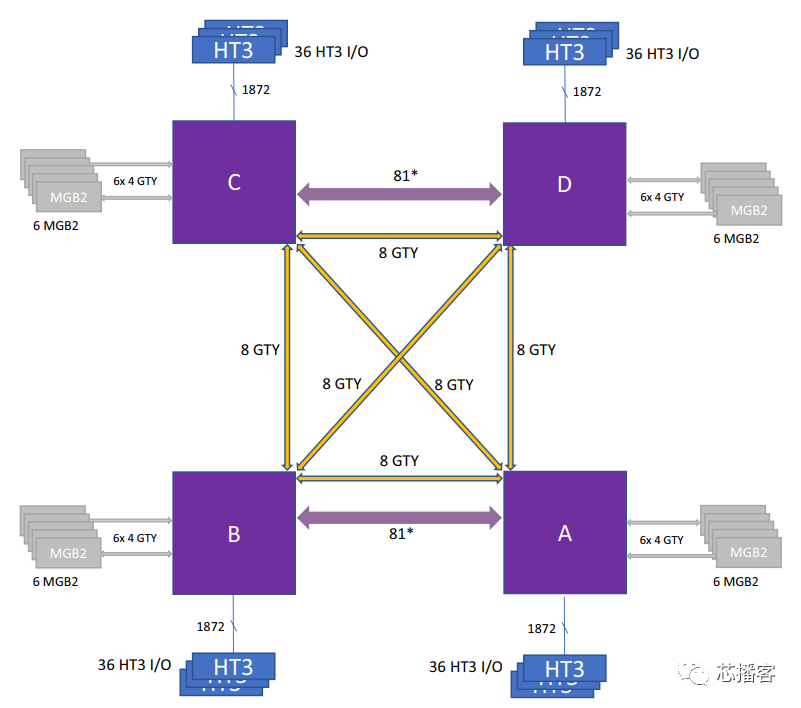

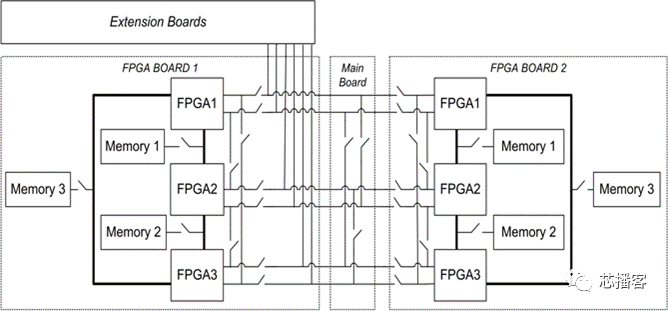

我們正在尋求盡可能靈活的互連布置,但要有高性能,并且也可以盡可能地定制,以滿足給定原型項目的互連需求。供應商應理解這些明顯矛盾的需求所推斷出的妥協,并應盡量選擇適用于盡可能多的最終用戶項目的最佳互連安排。最靈活的解決方案是使用某種形式的間接互連,其中兩個最常見的示例如下圖所示。這兩個例子是延遲互連和交換互連。

在延遲互連拓撲中,FPGA之間的固定連接相對較少,但每個FPGA引腳都被路由到附近的連接器。然后,根據每個特定項目的需要,使用其他介質(某些類型的連接器板或柔性電纜)連接這些連接器。例如,在上圖中,我們看到了一種連接器布置,通過在每個FPGA的多個連接器之間使用連接電纜,可以在FPGA1和FPGA 4之間進行大量連接。如果需要,堆疊連接器仍允許多個點之間的星形連接。

下圖是基于HAPS的平臺的示意圖和照片,顯示了使用夾層連接器板和帶狀電纜進行的本地和遠程連接。

連接器的粒度將影響其靈活性,但延遲互連為將FPGA連接在一起以及將FPGA連接到系統的其他部分提供了大量可能性。此外,由于連接不是固定的,因此很容易斷開電纜和連接器板,并在下一個原型項目中以新拓撲重新連接FPGA。

間接互連的第二個例子是交換互連,它依靠可編程開關將互連的不同部分連接在一起。當然,可以使用手動開關,但連接密度要低得多,出錯的可能性也會增加。假設,我們有一個理想化的中央交換路由矩陣,它可以將任何點連接到電路板上的任何點。

該矩陣可編程并配置為滿足任何給定設計的分區和路由需求。由于是可編程的,它還可以在項目之間或甚至在項目期間快速更改,以便輕松探索不同的設計選項。對于遠程操作,可能是在另一個站點的軟件驗證實驗室,可以將設計圖像加載到系統中,并配置交換互連,而無需任何人接觸原型本身。

交換互連方法的另一個顯著優點是它非常快速且易于更改,因此用戶不必認為互連是靜態的,而是更動態的。在將設計配置到板上之后,仍然可以將未使用的引腳或其他連接路由到其他點,例如,允許快速探索解決方案或調試方案,或將額外信號路由到測試和調試端口。

交換互連的另一個優點是可以將交換機的編程置于設計劃分工具的控制之下。在這種情況下,如果分區器意識到,為了實現最佳分區,它需要某些FPGA之間的更多連接,它可以立即執行該選項,同時使用這些修改的互連資源繼續分區任務。在這些場景中,細粒度的交換機結構非常有用,因此可以盡可能少地進行必要的連接來解決分區問題,同時仍然允許其他地方使用其余的本地連接。

如上圖所示。這里我們可以看到,除了同一板上的FPGA之間的固定跡線之外,還有可編程開關,可用于通過附加跡線連接FPGA。類似的交換機可以將內存模塊鏈接到平臺或鏈接到其他板或平臺,從而構建具有更多FPGA的更大系統。并非所有的交換機組合都是合理的,而且在大多數情況下,由于它們太多,無法手動控制,因此它們由軟件自動配置,軟件也了解系統拓撲和分區要求。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614044 -

連接器

+關注

關注

99文章

15217瀏覽量

139290 -

交換機

+關注

關注

21文章

2721瀏覽量

101352 -

SoC設計

+關注

關注

1文章

151瀏覽量

19074 -

柔性電纜

+關注

關注

0文章

9瀏覽量

2288

原文標題:【芯知識】多片FPGA原型驗證系統互連拓撲分析

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

所有FPGA引腳都應該以星形連接在一起嗎?

所有FPGA引腳都應該以星形連接在一起嗎?

評論