眾所周知,隨著芯片越來越大,功能越來越豐富,以及移動市場的切實需求,低功耗的芯片設(shè)計,越來越受到推崇。這里,結(jié)合多年的低功耗設(shè)計經(jīng)驗,把一些理念和方法,分享給各位。

通過一些理論書籍,大家都知道功耗的來源主要分為兩種,一種是動態(tài),一種是靜態(tài)。

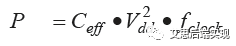

先來看一下,動態(tài)功耗的計算公式為,

dynamic power = switching power + internal power

switching power 計算公式為:

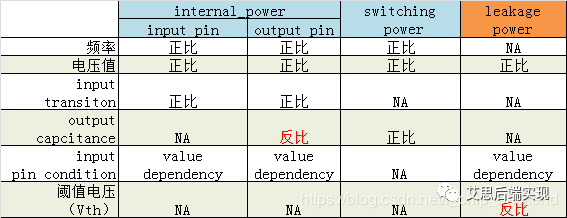

由此可知,動態(tài)功耗和頻率、關(guān)斷時的負(fù)載電容以及電壓的平方成正比,換言之,可以通過,改變頻率、負(fù)載電容以及電壓來改變動態(tài)功耗。

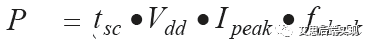

internal power 計算公式為

這里的tsc指的是NMOS/PMOS internal短路的時間。Ipeak指的是整個短路電流和導(dǎo)通電流的總和。

在實際的std-cell library里,工具使用了一個簡化的查找表方式來處理internal-power,示例如下

P = func(input_transition, input_pin_condition, output_capacitance)

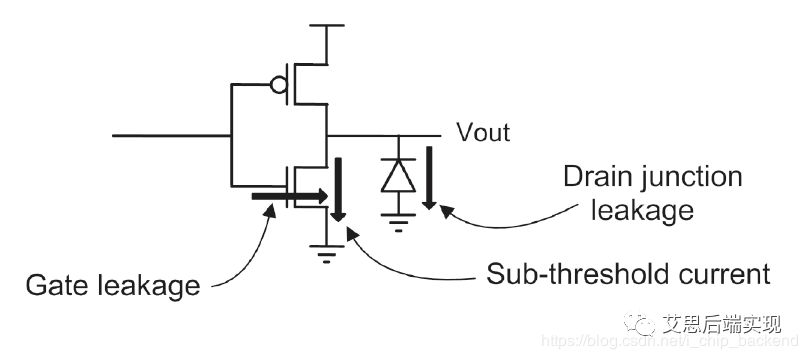

漏電功耗(leakage power)的計算模型

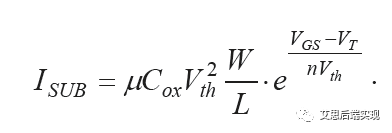

對應(yīng)的漏電電流計算公式是:

這里的Vth, CoxW/L都是工藝相關(guān),不可以調(diào)整,Vgs就是VDD,Vt指的是閾值電壓。可以看到,閾值電壓越高漏電功耗就越低,但是由于工藝復(fù)雜的增加,閾值電壓越高的器件,對應(yīng)的翻轉(zhuǎn)速度就會變慢,導(dǎo)致影響性能

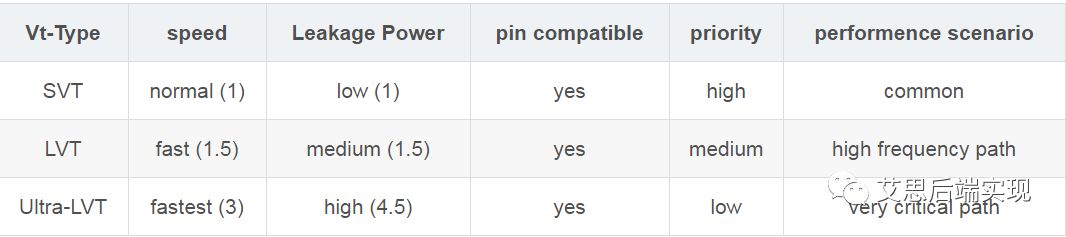

基于以上的理論,可以推導(dǎo)出下表:

下邊就一起來看一下,目前的設(shè)計領(lǐng)域里邊流行的那些降低功耗的技術(shù)手段吧。

clock gating

這個是一個在綜合器里非常常用,也很通用的手段。總而言之,clock gating不但可以優(yōu)化動態(tài)功耗,同時還可以優(yōu)化面積(具有漏電功耗提高的可能),這里也有一些別的數(shù)據(jù)作為參考

… reports an area reduction of 20% and a power savings of 34% to 43% depending on the operating mode

綜合工具在自動插入clock gating的時候,把原有的data上的通用邏輯加以整合,掛到了clock 的EN控制端,這樣就可以大幅度的節(jié)省面積,尤其是在多位寬的總線。反言之,在非常窄的總線上,clock-gating在面積和功耗上不一定會有效果,譬如小于三位的總線。

工藝演進(jìn)

隨著晶體管的尺寸越來越小,三極管導(dǎo)通所需要的電壓也就越來越小了,從上邊的表哥里邊可以看到,降低電壓,可以有效改變動態(tài)功耗的處境。

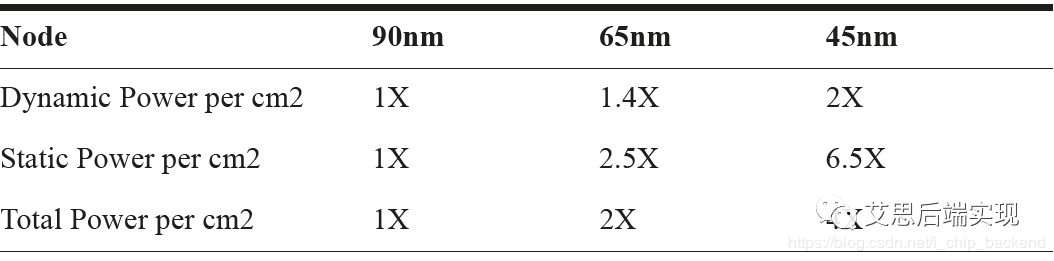

從40/28nm的0.99v到現(xiàn)在7nm的0.7v,通過改變工藝都可以有效降低動態(tài)功耗。相反,對于相同尺寸的die,工藝的提高預(yù)示著可以放置更多的管子。

芯片的功耗隨著工藝的提高,呈現(xiàn)出整體放大的趨勢,尤其是漏電功耗,如下圖

先進(jìn)工藝的性能和速度大幅度提高,追擊先進(jìn)工藝是大勢所趨,但是相應(yīng)的,現(xiàn)代芯片的功耗挑戰(zhàn),會比以往來得更猛烈。

power gating (可關(guān)斷電源)

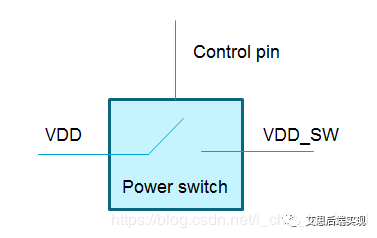

電壓降低了,動態(tài)功耗確實可以變小,但是Vdd和Vth的差值會變得更小,Vth (閾值電壓:MOS導(dǎo)通時所需要的的電壓)更不可能一直毫無代價降低,所以,在實際的實現(xiàn)中,使用Switchable Power domain的方式,來整體關(guān)斷某個或者某個區(qū)域、層級的器件,從而來降低整體靜態(tài)功耗。這個實現(xiàn)電源控制的器件,就叫做power gating。

原理很簡單,就是在當(dāng)前的std-cell的PG rail上面加一個開關(guān),通過外界信號來控制,從而達(dá)到可以std-cell電源的目的

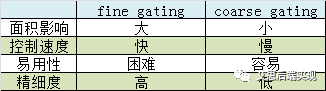

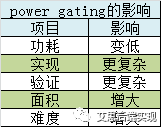

仔細(xì)想一下,這種結(jié)構(gòu)可以所在std-cell的內(nèi)部,也可以做在power rail上,前者通常被叫做fine gating,后者會被稱作coarse gating。第一種的設(shè)計效果更好,甚至可以具體到某一個std-cell的電源開關(guān)控制,但是std-cell面積會變大。第二種,顯而易見,如果使用在rail上,精細(xì)度會變差,但是,面積會很有優(yōu)勢,具體的實現(xiàn)方法也會簡化。具體的比較如下表:

結(jié)合實際,在正常的使用中,并非所有的std-cell都需要單獨控制,大部分都是一個功能模塊的整體調(diào)配,所以現(xiàn)在很多設(shè)計里邊都會使用coarse gating而非fine gating的實現(xiàn)方法(如果真的使用fine gating,不知道后端實現(xiàn)工程師會不會咬人)

模塊關(guān)斷的方法可以大幅度降低leakage,但是也會帶來一些新的挑戰(zhàn),主要是后端實現(xiàn)的時候:isolation,power switch 以及PG route都會有很大的變化。

除此之外,前端的low power仿真也需要格外注意,如果某些scenario沒有考慮好,核心模塊在不期望的時候被關(guān)斷,那么會引起系統(tǒng)性問題的。具體加下表:

動態(tài)電壓和頻率調(diào)節(jié)(Dynamic Voltage and Frequency Scaling)和自適應(yīng)電壓調(diào)節(jié)Adaptive Voltage Scaling (AVS)

在當(dāng)下,為了節(jié)省功耗,各位工程師也是拼了。在后端實現(xiàn)的不斷調(diào)整和改變的同時,前端的TX們也沒有閑著。DVFS就是一個基于設(shè)計,功能原理的有效降低功耗的一個典型方案。

在芯片的實際使用中,真實的使用場景會比較復(fù)雜,就拿手機而言,譬如

用戶待機的時候,只需要網(wǎng)絡(luò)連接可能就足夠了

聽歌的時候可能是不需要屏幕的支持

用戶在拍照的時候網(wǎng)絡(luò)的功能需求也不是很強烈

當(dāng)你玩游戲的時候,CPU可能就要調(diào)度所有的硬件來支持游戲的流程運行,

通過不同的場景,芯片基于用戶需求來適當(dāng)?shù)恼{(diào)度各個功能的使用和性能調(diào)節(jié)

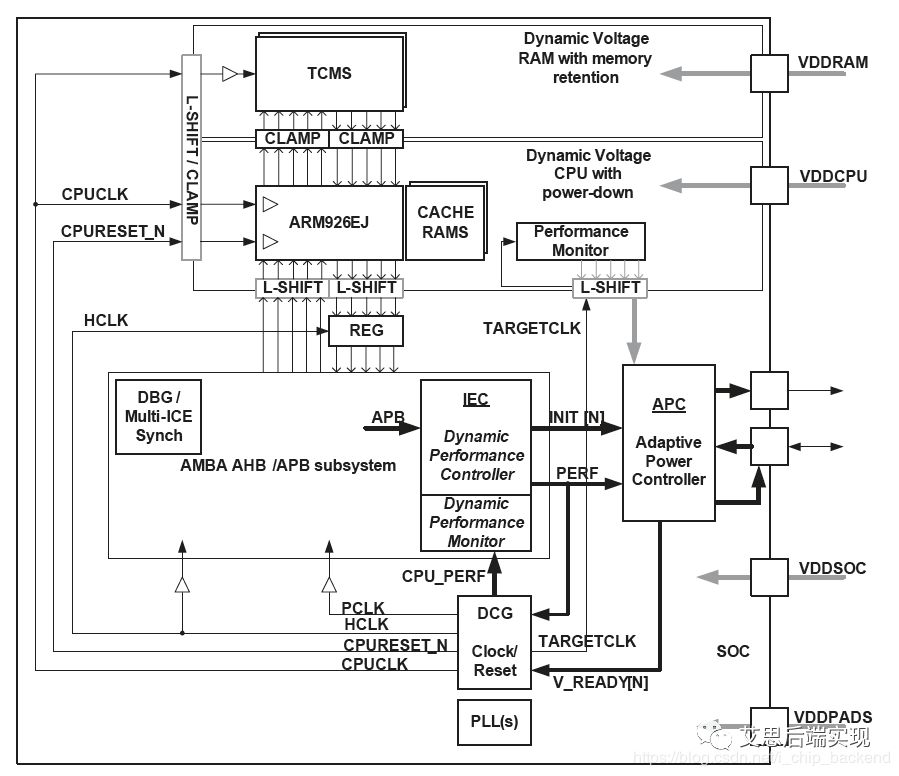

這個示例是一個UART的構(gòu)造框圖,基于這樣的一個邏輯架構(gòu),規(guī)劃出不同的使用場景,從而可以展現(xiàn)出不同場景下面所需要的電壓和頻率。

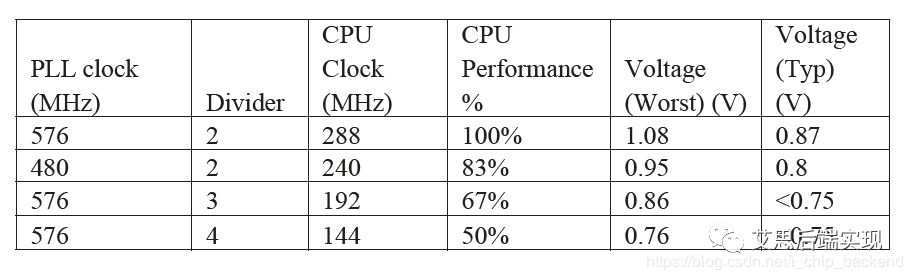

最后可以定義出一個類似上邊的一個表格,在系統(tǒng)判斷出不同的使用場景后,就會配置出不同的電壓和頻率值,從而達(dá)到不同場景下的功耗優(yōu)化的可能,這也就是常說的DVFS,類似于一種對于預(yù)定義場景的一種查找表的操作。

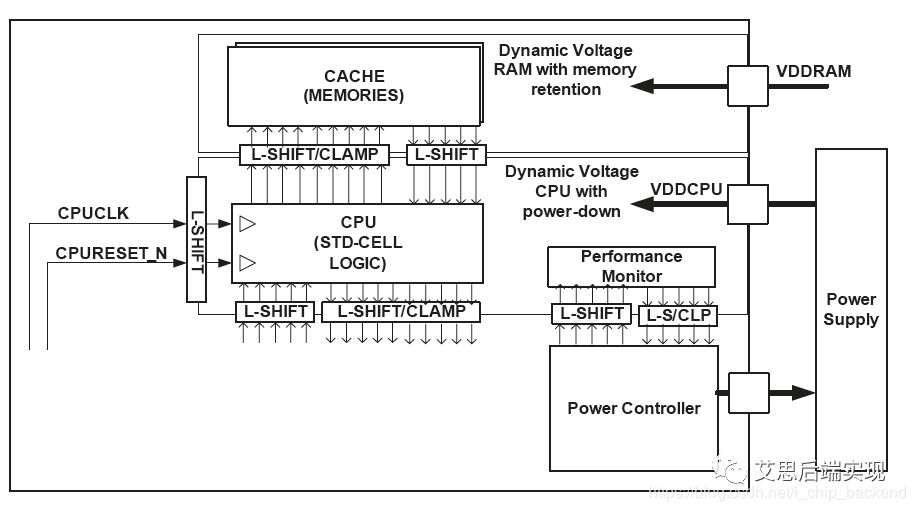

AVS是在DVFS上邊更為先進(jìn)的一種調(diào)整方式,框圖如下:

和DVFS的簡單查找表不同,這里會在系統(tǒng)里邊集成一個PM(Performance Monitor),對于系統(tǒng)的運行進(jìn)行實時監(jiān)控,通過判斷,動態(tài)的調(diào)整電壓和頻率,這里可以引入一些自學(xué)習(xí)的功能,從而根據(jù)不同用戶的使用習(xí)慣,來提供更為細(xì)致的自定制服務(wù)。可以設(shè)想,愈發(fā)細(xì)致的個性化服務(wù),加之自學(xué)習(xí)的預(yù)判功能,都可以進(jìn)一步的提高電源功耗的優(yōu)化。

Vt cell的應(yīng)用

從上一篇文章可以看到,不同Vt下的cell特性是不同的,現(xiàn)在的工藝都會提供不同傾向的Vt庫,見下表

可以看到,合理使用不同的Vt cell可以滿足不同PPA的需求,在使用過程中,應(yīng)該優(yōu)先使用SVT的cell,而后是LVT,最后萬不得已的時候再使用ULVT(ULVT的leakage可不是一般的大啊,一般會達(dá)到SVT的四到五倍的量級)

工具可以完美支持mix-Vt的設(shè)計。工具的策略是,在功耗優(yōu)化的過程中,根據(jù)用戶設(shè)定的Vt等價置換規(guī)則,在不影響timing的情況下,選擇leakage小的cell,這樣在兼顧性能的時候可以滿足power的需求。

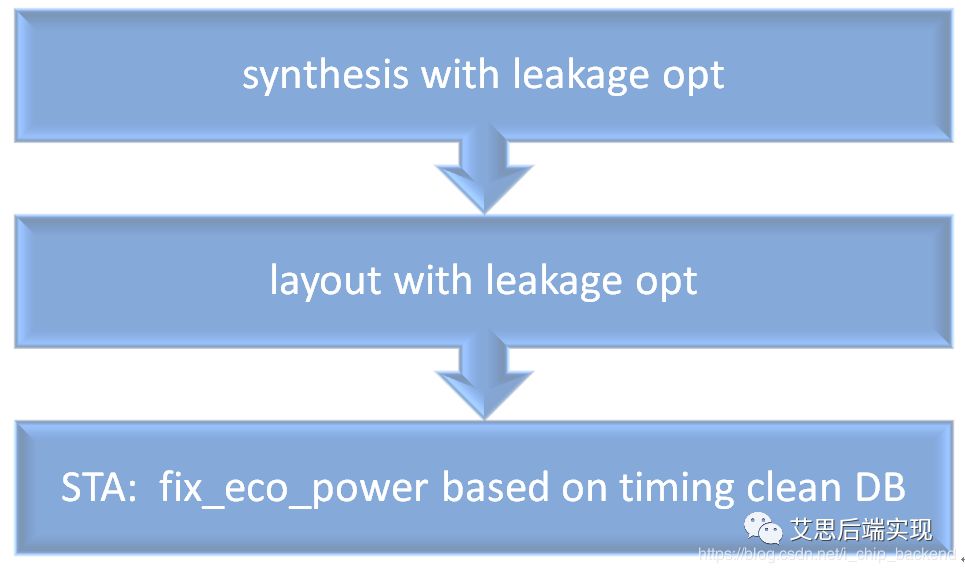

由于,后端實現(xiàn)的時候,通常由三個階段需要用到這個技術(shù)手段,這里給出一個通常的應(yīng)用場景供大家參考

秘籍:一定要做最后一步,效果會非常顯著,可以有效地提高leakage power。

版圖優(yōu)化

在版圖實現(xiàn)當(dāng)中,后端實現(xiàn)的工具是非常靈活的,低功耗的設(shè)計當(dāng)中,經(jīng)常會使用到power-domain和voltage-area這些技術(shù)來優(yōu)化power,簡單的講,通過UPF,在設(shè)計里邊定義一些switch-off power和always domain,在某些功能不使用的時候,就把SW domain關(guān)掉,這個時候,SW里的power-gating cell的輸出會呈現(xiàn)出一個無線接近電源(footer power-gating)或者地(header power-gating)的狀態(tài),從而理論上確保了SW domain的leakage是零(但是,這是指理論的,由于power gating cell本身會有漏電的問題,所以零的漏電只是理論上的)。

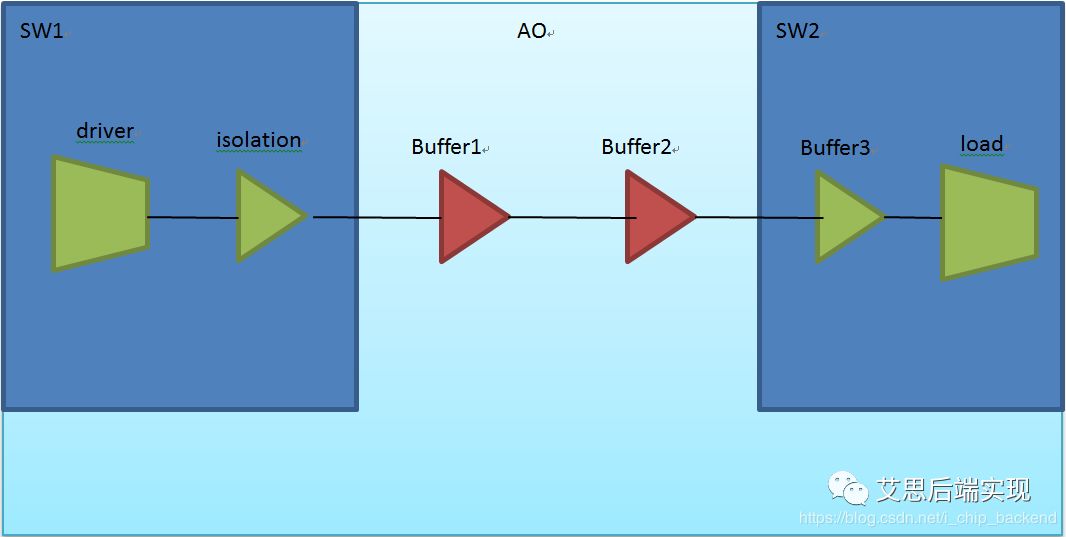

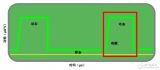

這里可以引申出一系列的思路,版圖工程師可以盡可能的讓更多的cell放到SW domain,從而在實際使用的情境下,可以拿到更好的功耗。看一下這個例子:

一條路徑,從SW1出發(fā)到達(dá)SW2,中間一共有四級,其中SW里邊有一個buffer和一個isolation,AO里邊,有兩個buffer ,從power上講,在SW1和SW2同時關(guān)斷的時候,這兩個AO的buffer,不會有任何的動態(tài)功耗(dynamic power),這是因為SW1的isolation的輸出已經(jīng)被鉗位(clamp)到無效態(tài)(一個常值),但是這兩個buffer的leakage power是不能省略的,所以下圖的floorplan,從power優(yōu)化上來講一定是個更好的選擇

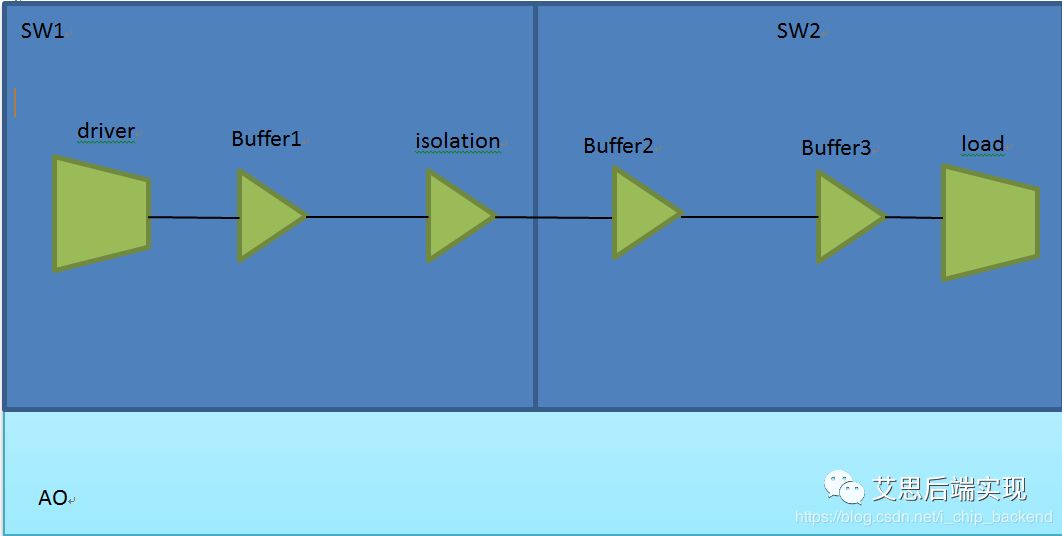

可以看到,中間的級數(shù)沒有發(fā)生改變,但是之前的buffer1和buffer2,都已經(jīng)被放置到了SW domain了,這樣,在SW關(guān)斷的時候,這兩個buffer的leakage power就是零(理論上)。這里只是一個連接和兩個buffer的示例,實際中VA之間的連接非常復(fù)雜,通過版圖的優(yōu)化調(diào)整,可以讓出更多的leakage power。

低功耗設(shè)計是一套完整的理論體系,從原理、代碼、UPF、綜合、版圖等等,每個步驟的一點點提高,都會帶來不同程度的優(yōu)化,勿以優(yōu)化小而不為,點點滴滴的進(jìn)步就會造就更加節(jié)能的芯片實現(xiàn)。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52115瀏覽量

435571 -

NMOS

+關(guān)注

關(guān)注

3文章

355瀏覽量

35344 -

低功耗

+關(guān)注

關(guān)注

10文章

2727瀏覽量

104498 -

動態(tài)功耗

+關(guān)注

關(guān)注

0文章

12瀏覽量

11585 -

負(fù)載電容

+關(guān)注

關(guān)注

0文章

143瀏覽量

10722

原文標(biāo)題:淺談芯片低功耗的設(shè)計實現(xiàn)

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

超小藍(lán)牙模組,遠(yuǎn)距離,低功耗#藍(lán)牙芯片 #低功耗藍(lán)牙 #物聯(lián)網(wǎng) #硬聲創(chuàng)作季

淺談CC2640超低功耗無線MCU

無線模塊如何實現(xiàn)低功耗

怎么實現(xiàn)低功耗單芯片高性能音頻CODEC的設(shè)計?

低功耗硬件電路設(shè)計中電源芯片選型

時鐘芯片的低功耗設(shè)計研究

如何使用Freeze技術(shù)實現(xiàn)低功耗設(shè)計

低功耗藍(lán)牙芯片的應(yīng)用可顯著降低功耗和成本

淺談電源芯片選型之低功耗

STM32與FreeRTOS實現(xiàn)低功耗

淺談芯片低功耗的設(shè)計實現(xiàn)

淺談芯片低功耗的設(shè)計實現(xiàn)

評論