介紹

在芯片做功能ECO時(shí),DFT部分的邏輯常常被破壞,這是由于正常工作模式下修改設(shè)計(jì)的原因。在功能ECO時(shí),DFT的控制信號(hào)被設(shè)為無效,ECO工具意識(shí)不到DFT邏輯被更改,并且形式驗(yàn)證也驗(yàn)證不出來。我們發(fā)現(xiàn),當(dāng)ECO過的網(wǎng)表送給DFT工具,DFT工具需要運(yùn)行很長時(shí)間來識(shí)別網(wǎng)表是否存在問題。

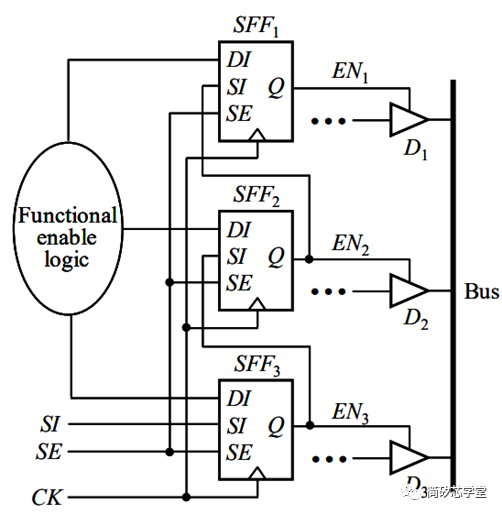

NanDigits GOF提供了一種快速DFT DRC檢查的功能,來檢查DFT邏輯中的問題。DFT中最基本的DRC檢查就是確認(rèn)掃描鏈?zhǔn)欠裢暾褪钦f,GOF可以捕獲和輸出測(cè)試進(jìn)行中的測(cè)試pattern。另外,在測(cè)試模式下,DFT的時(shí)鐘和復(fù)位必須是要受控的,以便來使能合適的測(cè)試pattern。

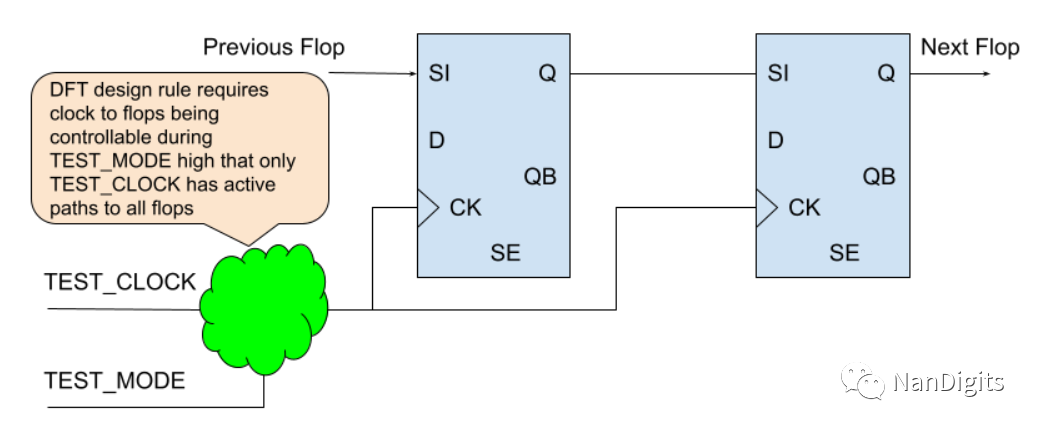

下圖是DFT模式使能后的示意圖,TEST_MODE=1,TEST_CLOCK被送到每個(gè)DFF的時(shí)鐘端。

示例

下面是GOF做DFT DRC檢查的腳本,先讀入lib庫和網(wǎng)表,再設(shè)置使能DFT模式,并創(chuàng)建時(shí)鐘、復(fù)位、si/so掃描鏈對(duì),最后運(yùn)行dft_drc()命令來執(zhí)行DFT DRC的檢查。

# dft_drc.pl

set_log_file("dft_drc.log");#設(shè)計(jì)log

read_library("art.5nm.lib");#讀入lib庫

read_design('-imp', 'dft_top.v'); # 讀入帶有DFT的網(wǎng)表

set_top("DFT_TOP"); # 設(shè)置頂層

set_pin_constant("test_scan_shift",1);# 設(shè)scanshift為1

set_pin_constant("all_test_reg/Q",1);#設(shè)TDRall_test寄存器輸出Q為1

set_pin_constant("test_mode_reg/Q",1);#設(shè)TDRtest_mode寄存器輸出Q為1

create_clock("occ_add_1_inst/U0/Z",10);#創(chuàng)建時(shí)鐘,周期10ns,可能有多個(gè)

create_clock("occ_add_2_inst/U0/Z",10);

create_reset("power_on_reset",0);#創(chuàng)建reset

set_top("DESIGN_TOP"); # pin_si/pin_so是DFT_TOP的內(nèi)部pin

set_scan_pairs("pin_si[0]","pin_so[0]");#添加掃描鏈對(duì)

set_scan_pairs("pin_si[1]", "pin_so[1]");

set_top("DFT_TOP");#回到頂層

my$err=dft_drc;#運(yùn)行DFT DRC檢查

if($err){

gprint("DFT DRC found $err errors

");

}

運(yùn)行DFT DRC檢查:

gof -run dft_drc.pl

結(jié)語

NanDigits GOF提供了快速DFT DRC的檢查和修復(fù),來保證功能ECO不會(huì)影響到DFT掃描鏈,縮短功能ECO后的DFT修復(fù)和驗(yàn)證的時(shí)間,幫助客戶更快的Tapeout。最新版GOF10.4支持此功能,歡迎試用評(píng)估。

審核編輯:劉清

-

DFT

+關(guān)注

關(guān)注

2文章

233瀏覽量

23202 -

DRC

+關(guān)注

關(guān)注

2文章

153瀏覽量

36887 -

ECO

+關(guān)注

關(guān)注

0文章

52瀏覽量

15101 -

控制信號(hào)

+關(guān)注

關(guān)注

0文章

191瀏覽量

12237

原文標(biāo)題:用NanDigits GOF來做DFT DRC檢查

文章出處:【微信號(hào):ExASIC,微信公眾號(hào):ExASIC】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

典型的DRC案例介紹

HyperLynx DRC功能和優(yōu)勢(shì)

電氣設(shè)計(jì)規(guī)則檢查工具HyperLynx DRC

Altium顯示DRC錯(cuò)誤的檢查方法

PCB設(shè)計(jì)電氣規(guī)則檢查器解決DRC問題

為什么DRC檢查總是會(huì)報(bào)錯(cuò)

基于Cadence軟件DRACULA工具的DRC檢查

PCB layout有DRC檢查,為什么還要用DFM?

【實(shí)用干貨】PCB layout有DRC檢查,為什么還要用DFM?

用NanDigits GOF做DFT DRC檢查詳細(xì)的介紹和舉例

一種快速DFT DRC檢查的功能介紹

用NanDigits GOF來做DFT DRC檢查的介紹和舉例

什么是DFT友好的功能ECO呢?

解析什么是DFT友好的功能ECO?

實(shí)踐GoF的23種設(shè)計(jì)模式:解釋器模式

NanDigits GOF提供一種快速DFT DRC檢查的功能

NanDigits GOF提供一種快速DFT DRC檢查的功能

評(píng)論