FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。

1)盡可能采用單一時鐘;

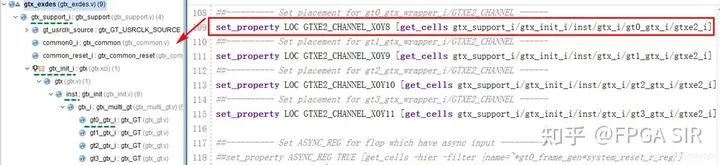

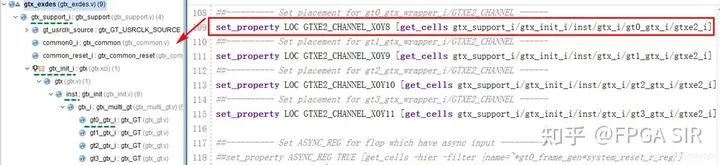

2)如果有多個時鐘域,一定要仔細劃分,千萬小心,同時設置時序約束;

1)盡可能采用單一時鐘;

2)如果有多個時鐘域,一定要仔細劃分,千萬小心,同時設置時序約束;

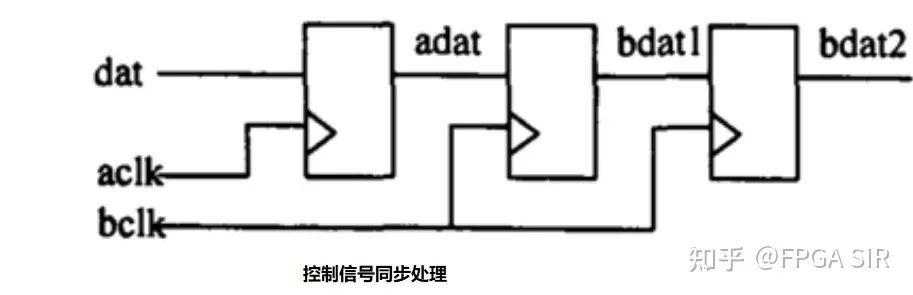

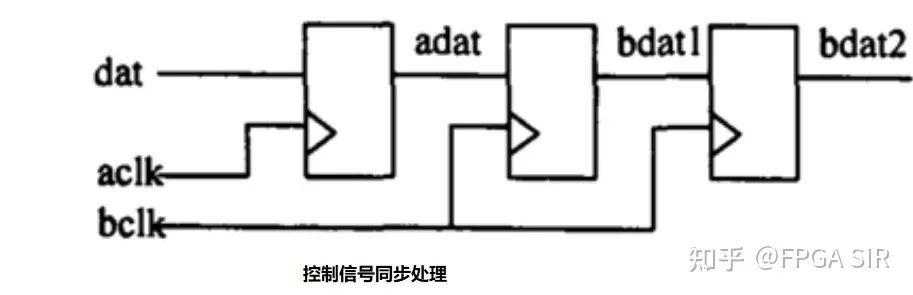

?3)跨時鐘域的信號一定要做同步處理;

對于控制信號的異步處理是寄存器打兩拍緩存;

?3)跨時鐘域的信號一定要做同步處理;

對于控制信號的異步處理是寄存器打兩拍緩存;

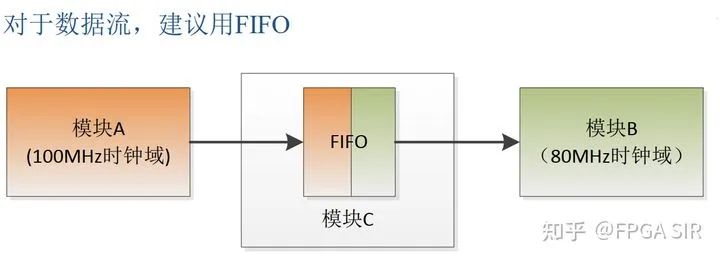

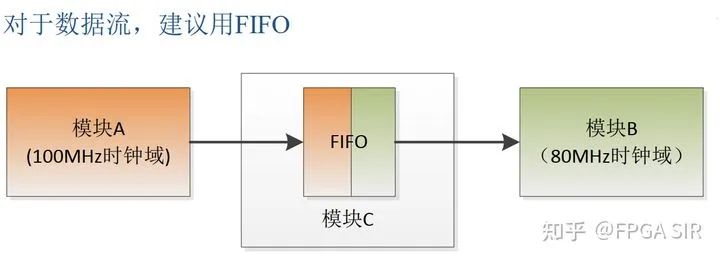

對于數據信號的異步處理是異步fifo緩存,同時注意FIFO兩側的數據流的速率問題;

對于數據信號的異步處理是異步fifo緩存,同時注意FIFO兩側的數據流的速率問題;

4)盡可能將FPGA內部的PLL、DLL利用起來,這會給你的設計帶來大量的好處;

5)對于高速的IO接口,需對高速IO設置的delay約束。

4)盡可能將FPGA內部的PLL、DLL利用起來,這會給你的設計帶來大量的好處;

5)對于高速的IO接口,需對高速IO設置的delay約束。

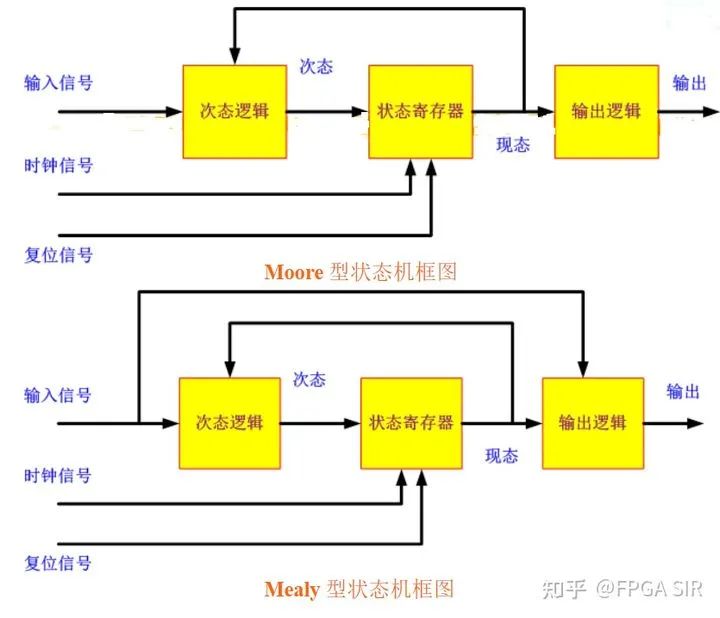

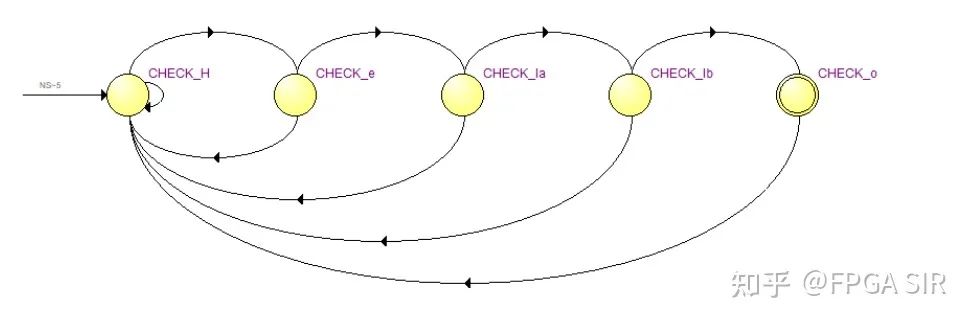

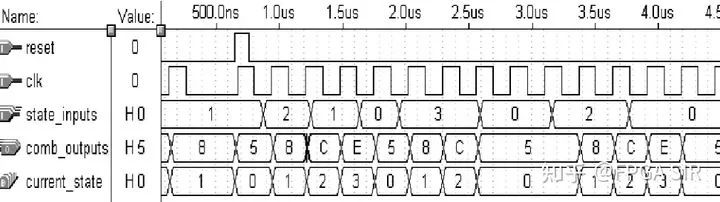

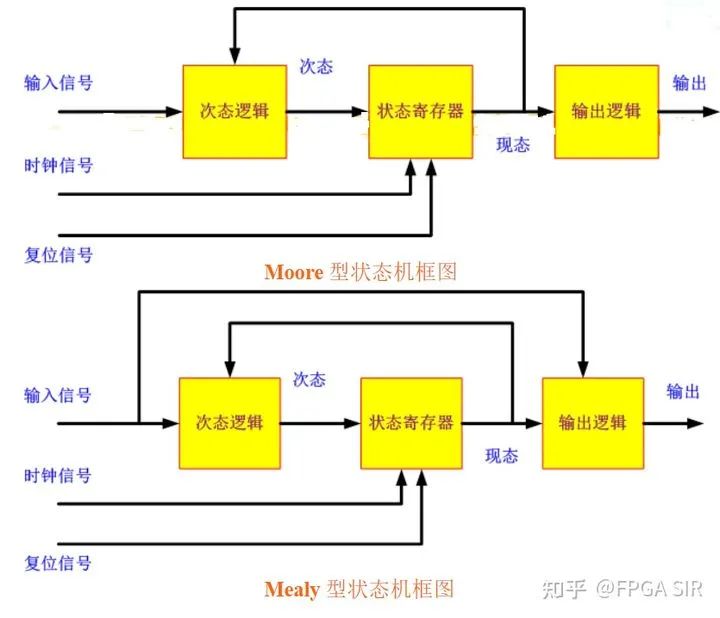

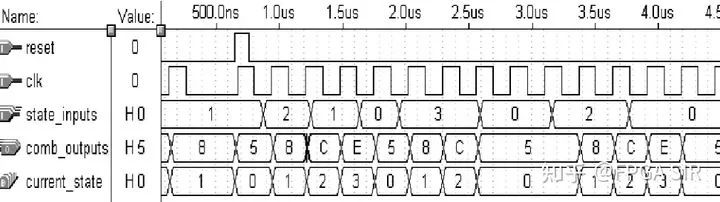

? ? ? ?FSM:有限狀態機,FPGA最基本的程序設計之一。FSM分為moore型和merly型,moore型的狀態遷移和變量無關,merly型則有關。

? ? ? ?FSM:有限狀態機,FPGA最基本的程序設計之一。FSM分為moore型和merly型,moore型的狀態遷移和變量無關,merly型則有關。

實際使用中大部分都采用merly型。

狀態機的編碼:二進制編碼(Binary),格雷碼編碼(Gray-code),獨熱碼(One-hot)。

實際使用中大部分都采用merly型。

狀態機的編碼:二進制編碼(Binary),格雷碼編碼(Gray-code),獨熱碼(One-hot)。

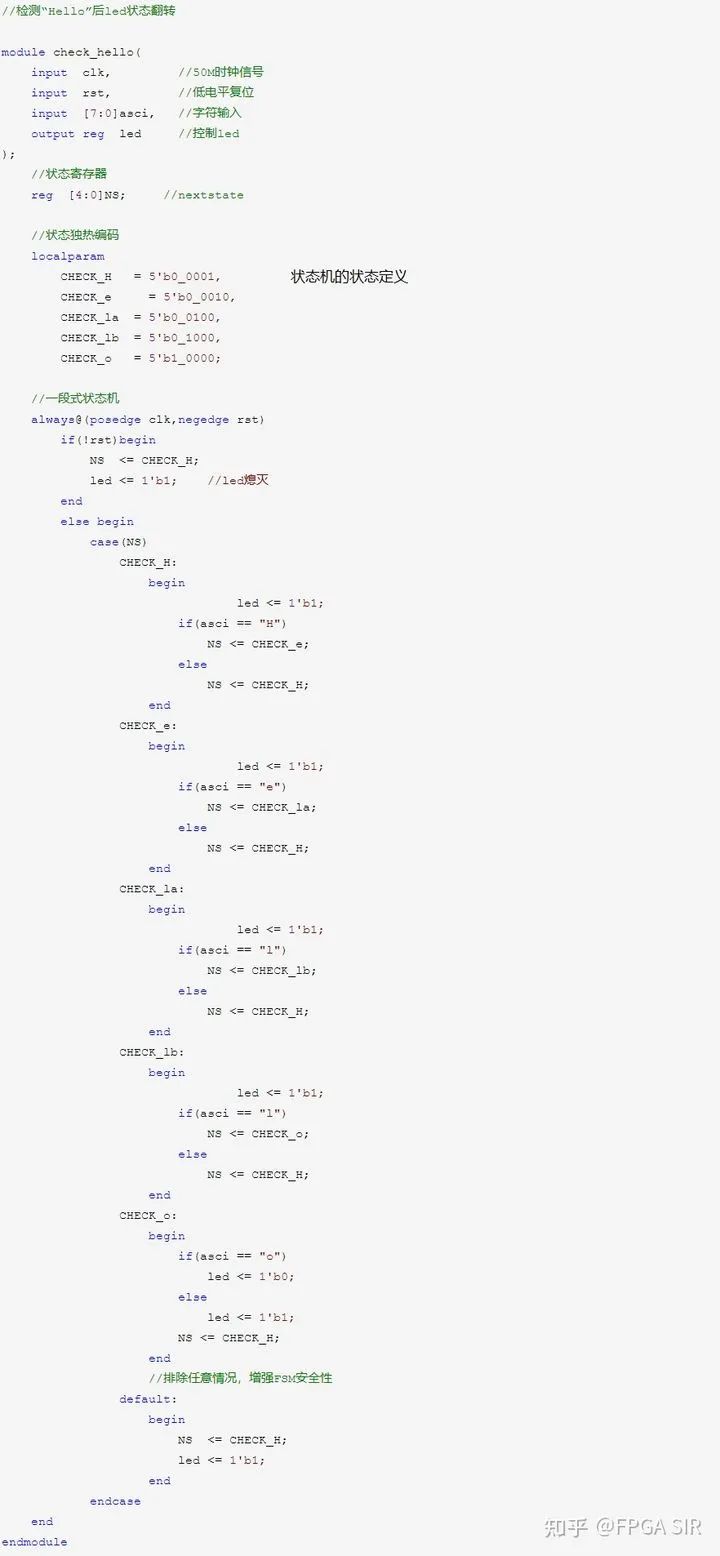

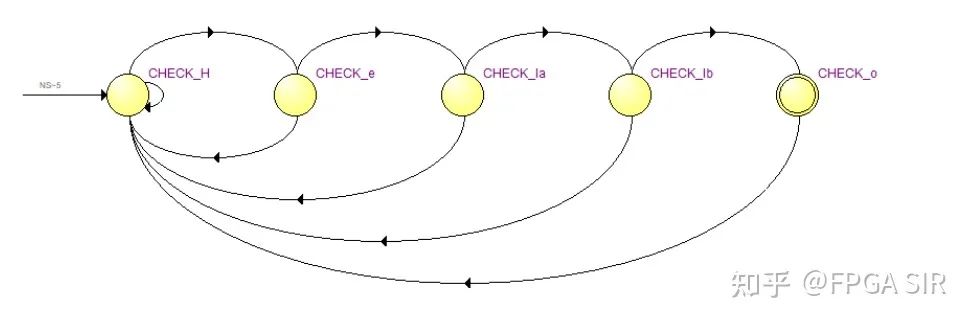

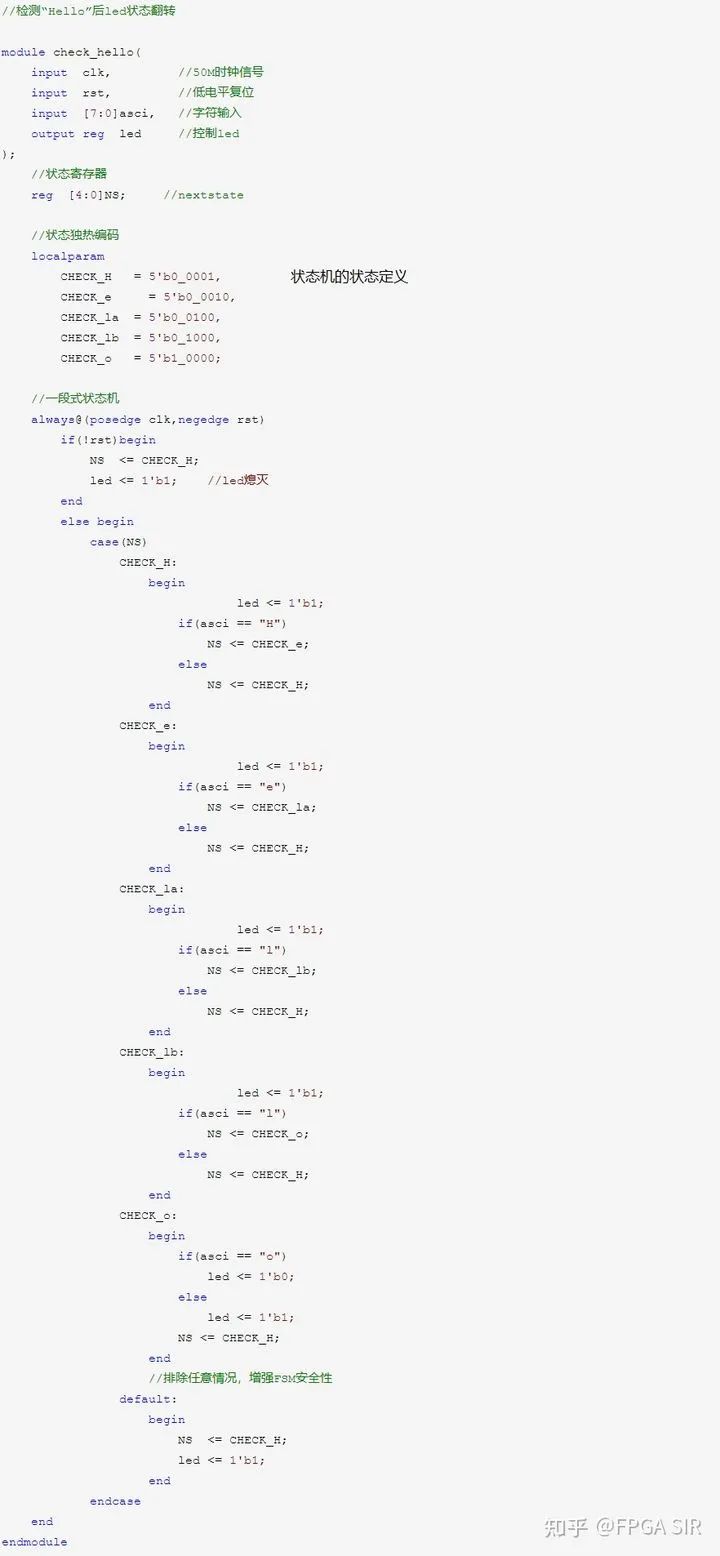

狀態機FSM一段式FPGA編碼參考。

狀態機FSM一段式FPGA編碼參考。

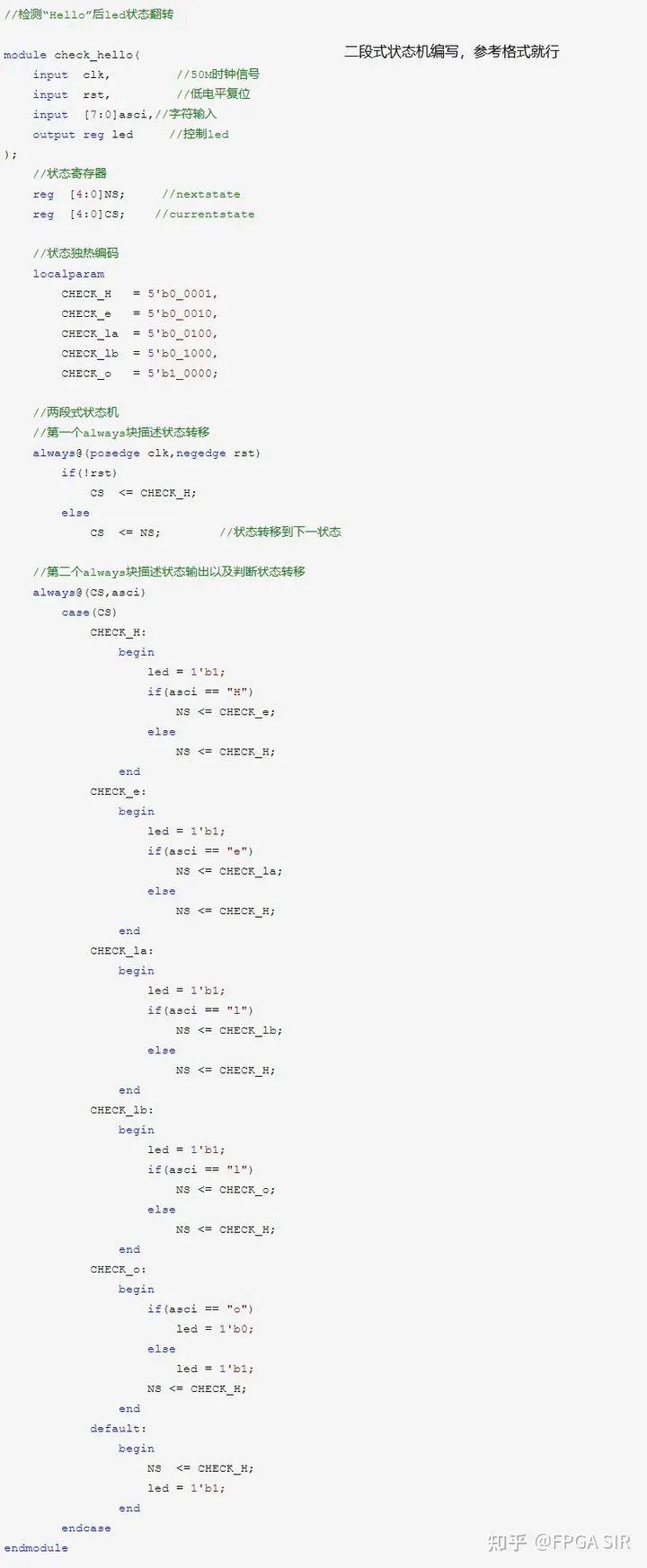

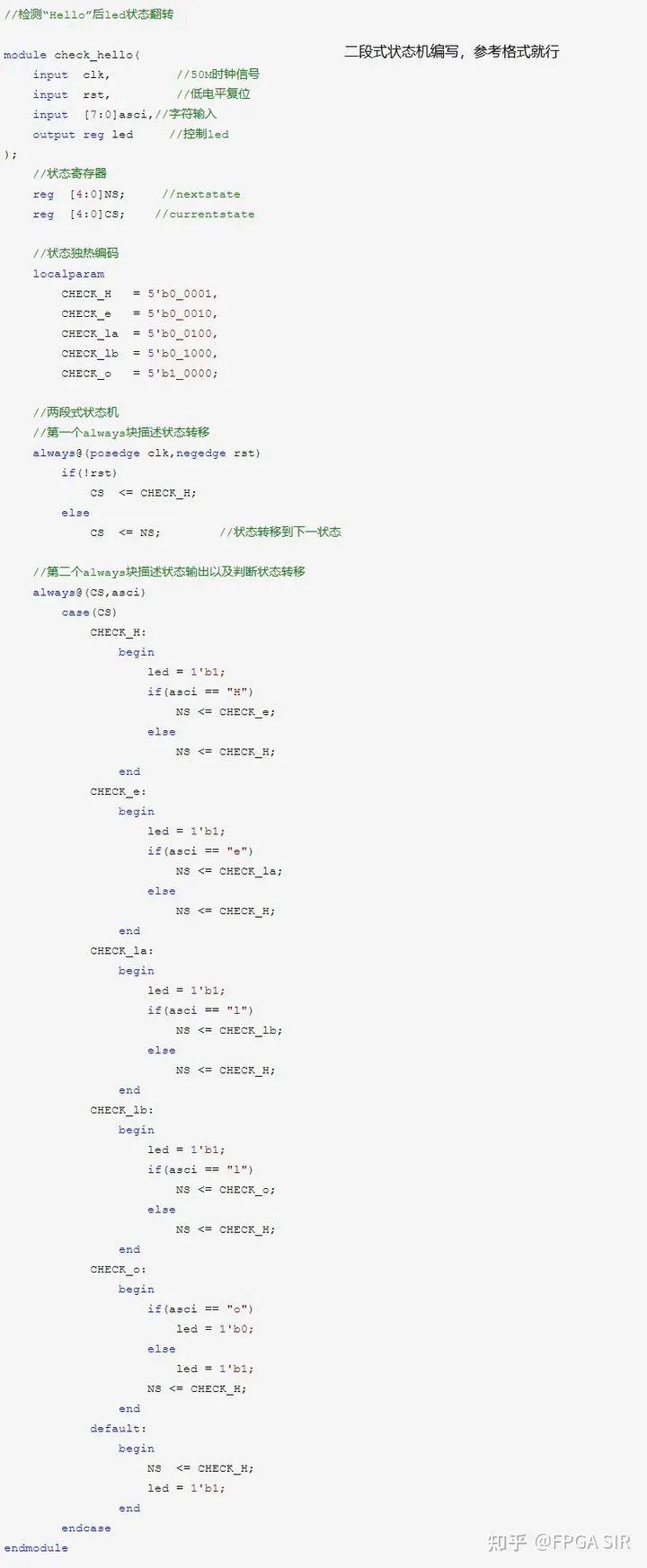

狀態機FSM二段式FPGA編碼參考。

狀態機FSM二段式FPGA編碼參考。

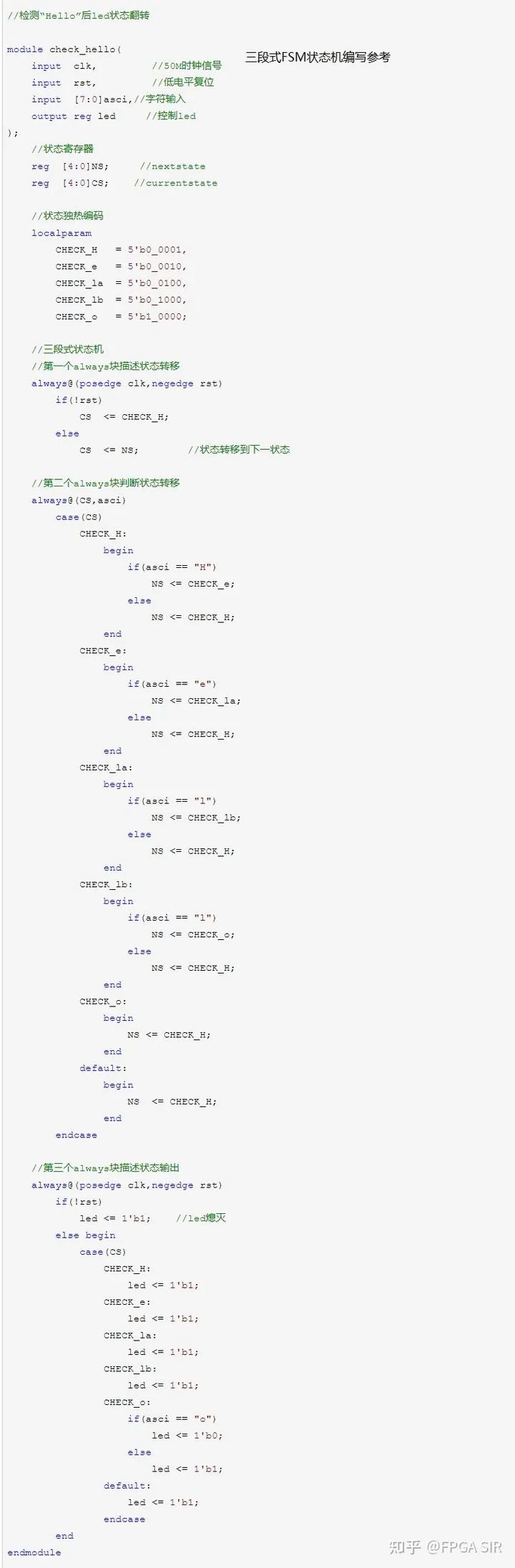

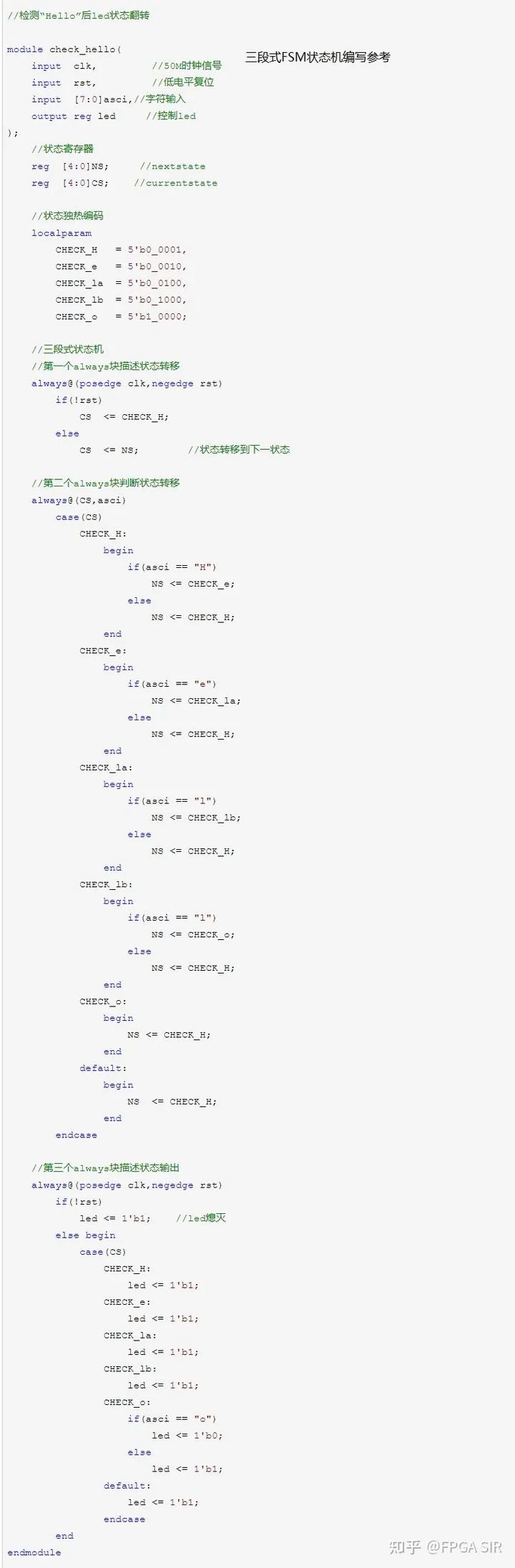

狀態機FSM三段式FPGA編碼參考。

狀態機FSM三段式FPGA編碼參考。

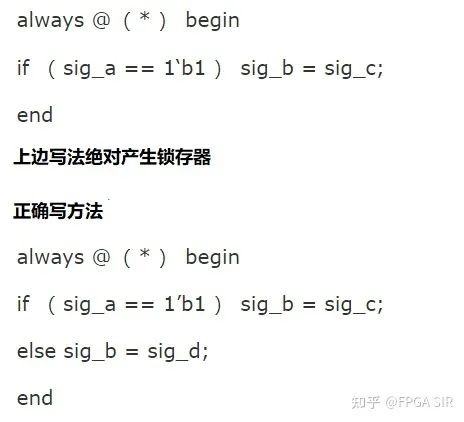

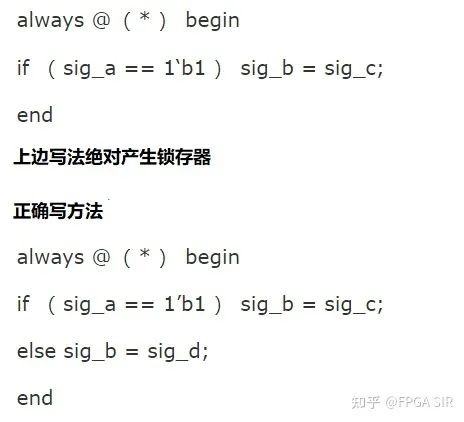

1)在組合邏輯always塊中,if語句一定要有else。

2)在組合邏輯always塊中,case語句的default一定不能少。

3)組合邏輯進程敏感變量不能少也不能多。

1)在組合邏輯always塊中,if語句一定要有else。

2)在組合邏輯always塊中,case語句的default一定不能少。

3)組合邏輯進程敏感變量不能少也不能多。

1)模塊仿真:針對每一個最小基本模塊的仿真;

單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到100%,這三種覆蓋率都可以通過modelsim來查看,不過需要在編譯該模塊時要在Compile option中設置好。

1)模塊仿真:針對每一個最小基本模塊的仿真;

單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到100%,這三種覆蓋率都可以通過modelsim來查看,不過需要在編譯該模塊時要在Compile option中設置好。

2)集成仿真:將多個大模塊合在一起進行仿真,覆蓋率要求盡量高;

3)系統仿真:將整個硬件系統合在一起進行仿真。

此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及BFM、Testbench等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。

審核編輯 :李倩

2)集成仿真:將多個大模塊合在一起進行仿真,覆蓋率要求盡量高;

3)系統仿真:將整個硬件系統合在一起進行仿真。

此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及BFM、Testbench等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。

審核編輯 :李倩

1)盡可能采用單一時鐘;

2)如果有多個時鐘域,一定要仔細劃分,千萬小心,同時設置時序約束;

1)盡可能采用單一時鐘;

2)如果有多個時鐘域,一定要仔細劃分,千萬小心,同時設置時序約束;

?3)跨時鐘域的信號一定要做同步處理;

對于控制信號的異步處理是寄存器打兩拍緩存;

?3)跨時鐘域的信號一定要做同步處理;

對于控制信號的異步處理是寄存器打兩拍緩存;

對于數據信號的異步處理是異步fifo緩存,同時注意FIFO兩側的數據流的速率問題;

對于數據信號的異步處理是異步fifo緩存,同時注意FIFO兩側的數據流的速率問題;

4)盡可能將FPGA內部的PLL、DLL利用起來,這會給你的設計帶來大量的好處;

5)對于高速的IO接口,需對高速IO設置的delay約束。

4)盡可能將FPGA內部的PLL、DLL利用起來,這會給你的設計帶來大量的好處;

5)對于高速的IO接口,需對高速IO設置的delay約束。

? ? ? ?FSM:有限狀態機,FPGA最基本的程序設計之一。FSM分為moore型和merly型,moore型的狀態遷移和變量無關,merly型則有關。

? ? ? ?FSM:有限狀態機,FPGA最基本的程序設計之一。FSM分為moore型和merly型,moore型的狀態遷移和變量無關,merly型則有關。

實際使用中大部分都采用merly型。

狀態機的編碼:二進制編碼(Binary),格雷碼編碼(Gray-code),獨熱碼(One-hot)。

實際使用中大部分都采用merly型。

狀態機的編碼:二進制編碼(Binary),格雷碼編碼(Gray-code),獨熱碼(One-hot)。

狀態機FSM一段式FPGA編碼參考。

狀態機FSM一段式FPGA編碼參考。

狀態機FSM二段式FPGA編碼參考。

狀態機FSM二段式FPGA編碼參考。

狀態機FSM三段式FPGA編碼參考。

狀態機FSM三段式FPGA編碼參考。

1)在組合邏輯always塊中,if語句一定要有else。

2)在組合邏輯always塊中,case語句的default一定不能少。

3)組合邏輯進程敏感變量不能少也不能多。

1)在組合邏輯always塊中,if語句一定要有else。

2)在組合邏輯always塊中,case語句的default一定不能少。

3)組合邏輯進程敏感變量不能少也不能多。

1)模塊仿真:針對每一個最小基本模塊的仿真;

單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到100%,這三種覆蓋率都可以通過modelsim來查看,不過需要在編譯該模塊時要在Compile option中設置好。

1)模塊仿真:針對每一個最小基本模塊的仿真;

單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到100%,這三種覆蓋率都可以通過modelsim來查看,不過需要在編譯該模塊時要在Compile option中設置好。

2)集成仿真:將多個大模塊合在一起進行仿真,覆蓋率要求盡量高;

3)系統仿真:將整個硬件系統合在一起進行仿真。

此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及BFM、Testbench等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。

審核編輯 :李倩

2)集成仿真:將多個大模塊合在一起進行仿真,覆蓋率要求盡量高;

3)系統仿真:將整個硬件系統合在一起進行仿真。

此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及BFM、Testbench等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21967瀏覽量

614188 -

仿真

+關注

關注

51文章

4241瀏覽量

135318 -

數據信號

+關注

關注

0文章

61瀏覽量

12100

原文標題:FPGA常見的基本設計要點

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

FPGA常見的IO接口標準設置

最近準備采用Xilinx FPGA進行多機通信,即主FPGA芯片將采集到的不同層的圖像數據流分別輸出給對應的4塊從FPGA芯片中,主從FPGA之間的連接機制采用星形拓撲結構。經計算,圖

發表于 10-17 09:14

?5070次閱讀

FPGA設計驗證關鍵要點

FPGA設計驗證關鍵要點不同于ASIC設計,FPGA設計中的標準元件或客制化實作,一般欠缺大量的資源及準備措施可用于設計驗證。由于可以重新程式化元件,更多時候驗證只是事后的想法。本文將探討在F

發表于 05-21 20:32

Protel99SE要點、經驗及常見問題

Protel99SE要點、經驗及常見問題:PCB emi設計要點PCB LAYOUT技術大全PCB精品技術技巧PCB設計常見問題PCB設計流程(新手必讀)Protel 99se快捷鍵大

發表于 09-13 15:13

?0次下載

Virtex5 FPGA在ISE + Planahead上部分可重構功能的流程和技術要點

部分可重構技術是Xilinx FPGA的一項重要開發流程。本文結合Virtex5 FPGA,詳細講解在ISE + Planahead上完成部分可重構功能的流程和技術要點。

FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明

本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

發表于 03-27 10:56

?20次下載

常見的fpga芯片有哪些

FPGA(現場可編程門陣列)芯片是一種可編程邏輯器件,其內部包含了大量的可編程邏輯單元和連接關系,可以通過編程來實現不同的邏輯功能。目前市面上有許多常見的FPGA芯片,這些芯片各自具有不同的規格、性能和特點,適用于不同的應用場景

FPGA常見的基本設計要點

FPGA常見的基本設計要點

評論