在傳統(tǒng)的收發(fā)器設(shè)計(jì)中,50 Ω單端接口廣泛用于RF和IF電路。當(dāng)電路互連時(shí),它們都應(yīng)該看到匹配的50 Ω輸出和輸入阻抗。然而,在現(xiàn)代收發(fā)器設(shè)計(jì)中,差分接口經(jīng)常用于在IF電路中獲得更好的性能,但實(shí)現(xiàn)它們需要設(shè)計(jì)人員面對(duì)幾個(gè)常見(jiàn)問(wèn)題,包括阻抗匹配、共模電壓匹配和難以計(jì)算的增益。了解發(fā)射器和接收器中的差分電路有助于優(yōu)化增益匹配和系統(tǒng)性能。

差分接口優(yōu)勢(shì)

差分接口有三個(gè)主要優(yōu)點(diǎn)。首先,差分接口可以抑制外部干擾和接地噪聲。其次,可以抑制偶數(shù)階輸出失真分量。這對(duì)于零中頻(ZIF)接收器非常重要,因?yàn)榈皖l信號(hào)中出現(xiàn)的偶數(shù)階分量無(wú)法濾除。第三,輸出電壓可以是單端輸出的兩倍,從而在給定電源上將輸出線性度提高6 dB。

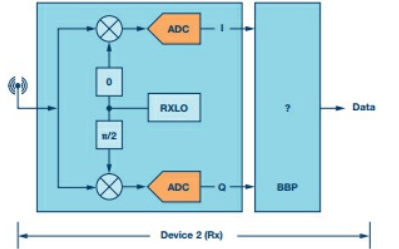

本文討論三種情況下的接口解決方案:ZIF接收器、超外差接收器和發(fā)射器。這三種架構(gòu)廣泛用于無(wú)線遠(yuǎn)程無(wú)線電單元 (RRU)、數(shù)字中繼器和其他無(wú)線儀器。

ZIF 接收器接口設(shè)計(jì)和增益計(jì)算

在零中頻(ZIF)接收器設(shè)計(jì)中,中頻信號(hào)很復(fù)雜,直流和極低頻信號(hào)可提供有用的信息。典型的解調(diào)器在驅(qū)動(dòng)200 Ω至450 Ω負(fù)載時(shí)可以提供最佳性能,而ADC驅(qū)動(dòng)器通常具有50 Ω以外的輸入阻抗,因此將系統(tǒng)與直流耦合電路連接既關(guān)鍵又困難。

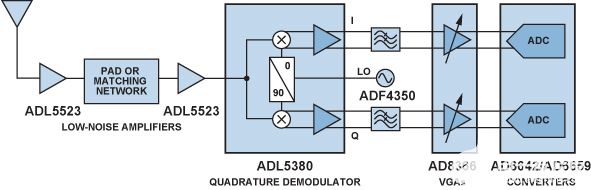

圖1顯示了使用兩個(gè)低噪聲放大器(LNA)、一個(gè)ADL5380 400 MHz至6000 MHz正交I/Q解調(diào)器、一個(gè)作為本振(LO)的寬帶頻率合成器ADF4350和雙通道數(shù)字可編程可變?cè)鲆娣糯笃?/u>(VGA)的ZIF接收器配置。表1顯示了相關(guān)的ADL5380接口和增益參數(shù)。

圖1.ZIF 接收器框圖。

表 1.ADL5380接口和增益參數(shù)

|

測(cè)試條件 |

VS = 5 V, TA = 25°C, fLO = 900 MHz, fIF = 4.5 MHz, PLO = 0 dBm, ZIN = 50 ? |

|

|

參數(shù) |

值 |

評(píng)論 |

|

電壓轉(zhuǎn)換增益 |

6.9分貝 |

I 和 Q 輸出上的 450-Ω 差分負(fù)載 |

|

5.9分貝 |

I 和 Q 輸出上的 200 Ω 差分負(fù)載 |

|

|

共模輸出電壓 |

2.5 V |

ADJ 連接到 VS |

|

I/Q差分輸出阻抗 |

50 ? |

|

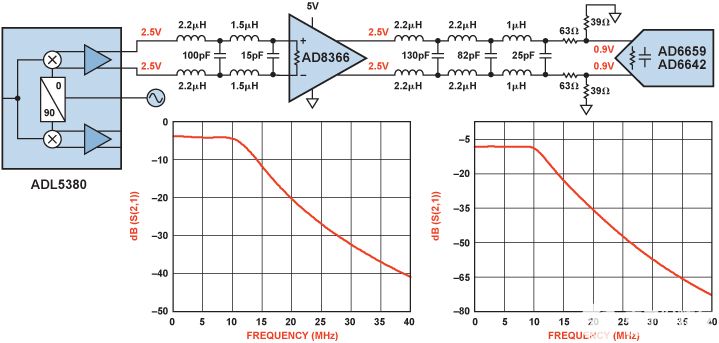

當(dāng)與具有217 Ω差分輸入阻抗的AD8366連接時(shí),ADL5380具有5.9 dB電壓增益和–0.5 dB功率增益[5.9 dB – 10log (217/50)]。為獲得最佳性能,通過(guò)將ADL5380 ADJ引腳連接到V,將ADL5380和AD8366之間的共模電壓設(shè)置為2.5 VS.在ADL5380和AD8366之間放置一個(gè)插入損耗為0.5 dB的差分四階巴特沃茲低通濾波器,可抑制噪聲和不需要的高頻分量。雖然濾波器會(huì)導(dǎo)致一些不匹配,但在基帶頻率下是可以容忍的。

表 2.AD8366接口和增益參數(shù)

|

測(cè)試條件 |

VS = 5 V, TA = 25°C, ZS = 200 ?, ZL = 200 ?, f = 10 MHz |

|

|

參數(shù) |

值 |

評(píng)論 |

|

電壓轉(zhuǎn)換增益 |

4.5分貝 |

最小數(shù)字增益設(shè)置 |

|

20.25分貝 |

最大數(shù)字增益設(shè)置 |

|

|

共模輸出電壓 |

1.5 V |

最低 |

|

2.5 V |

最大或輸入自偏置 |

|

|

差分輸入阻抗 |

217 ? |

|

|

共模輸出電壓 |

1.6 V |

最低 |

|

3 V |

最大 |

|

| 2.5 V | VCMA和VCMB保持浮動(dòng)狀態(tài) | |

|

差分輸出阻抗 |

28 ? |

|

|

線性輸出擺幅 |

6 V 峰峰值 |

1dB 增益壓縮 |

AD8366的共模輸出電壓可設(shè)置為2.5 V;當(dāng)VCM保持浮動(dòng)時(shí),它具有最佳的線性度。遺憾的是,AD6642在0.9 V共模輸入電壓(0.5 × AVDD)下性能最佳。由于AD8366的共模輸出電壓必須在1.6 V至3 V之間,因此AD6642 VCM和AD8366 VCM端子不能直接連接,必須使用電阻將AD8366共模輸出電壓分壓至0.9 V。

為獲得最佳性能,AD8366應(yīng)驅(qū)動(dòng)200 Ω負(fù)載。為了實(shí)現(xiàn)所需的共模電平和阻抗匹配,在AD8366之后增加了63 Ω串聯(lián)電阻和39 Ω分流電阻。該電阻網(wǎng)絡(luò)將使功率增益衰減4 dB。

AD8366輸出擺幅為6 V p-p,但電阻網(wǎng)絡(luò)提供的4 dB衰減將AD6642的電壓限制為2.3 V p-p,從而保護(hù)其免受大干擾尖峰或不受控制的增益造成的損壞。

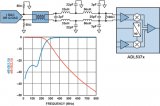

插入損耗為1.5 dB的差分六階巴特沃茲低通濾波器位于AD8366和AD6642之間,用于濾除不需要的高頻元件。I通道的完整差分接口如圖2所示。

圖2.ZIF接收機(jī)接口圖及仿真濾波器特性。

為了保留足夠的裕量以考慮增益隨溫度的變化,AD8366在正常模式下的增益設(shè)置為16 dB。

在這種配置中,整個(gè)信號(hào)鏈的增益為

5.9 dB – 10log (217/50) – 0.5 dB + 16 dB – 10log (200/217) – 1.5 dB – 4 dB

= 9.9 dB。

在ADL5380之前級(jí)聯(lián)插入的兩個(gè)LNA可實(shí)現(xiàn)32 dB增益。通過(guò)將模數(shù)轉(zhuǎn)換器配置為 2V p-p 擺幅和 78 Ω 等效輸入阻抗,它能夠處理 –34dBm 單音 RF 輸入信號(hào)。如果輸入信號(hào)在調(diào)制時(shí)峰均比(PAR)為10 dB,則–41 dBm輸入信號(hào)是接收器在不更改VGA設(shè)置的情況下可以處理的最大信號(hào)。

換句話說(shuō),電壓增益可用于計(jì)算信號(hào)鏈鏈路預(yù)算。當(dāng)輸入端口阻抗等于輸出端口阻抗時(shí),電壓增益等于功率增益。整個(gè)信號(hào)鏈的電壓增益為

32 dB + 5.9 dB – 0.5 dB + 16 dB – 1.5 dB – 8 dB = 43.9 dB。

對(duì)于單音信號(hào)輸入,要獲得 2V p-p 擺幅范圍,適當(dāng)?shù)妮斎牍β蕿?/p>

8 dBm – 43.9 dB + 10log (78/50) = –34 dBm。

結(jié)果與計(jì)算的功率增益非常匹配。

在某些應(yīng)用中,ADL5380可能需要直接連接到AD6642,在這種情況下,可以在AD6642差分輸入端增加一個(gè)500 Ω電阻,以改善匹配。ADL5380的電壓增益為6.9 dB,共模問(wèn)題與AD8366相同。應(yīng)使用 160 Ω 串聯(lián)電阻和 100 Ω分流器來(lái)實(shí)現(xiàn) 500 Ω負(fù)載和所需的共模電壓。同樣,電阻網(wǎng)絡(luò)將電壓衰減8 dB(功率衰減4 dB)。

插入損耗為1.5 dB的低通濾波器位于ADL5380和AD6642之間,用于濾除不需要的頻率分量。輸入阻抗為50 Ω,輸出阻抗為500 Ω。在這種配置中,整個(gè)信號(hào)鏈的增益為

6.9 dB – 10log (500/50) – 1.5 dB – 4 dB = –8.6 dB。

超外差接收器接口設(shè)計(jì)和增益計(jì)算

在超外差接收器中,系統(tǒng)使用交流耦合,因此在連接這些電路時(shí)不必考慮直流共模電壓。

ADL535x和ADL580x等許多混頻器具有200 Ω差分輸出阻抗,因此不同輸出阻抗的功率增益和電壓增益分別表示。

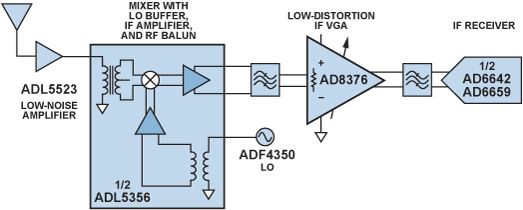

圖3所示為采用低噪聲放大器ADL5523實(shí)現(xiàn)的超外差接收器的一個(gè)通道;ADL5356雙通道平衡混頻器,內(nèi)置LO緩沖器、IF放大器和RF巴倫;低通濾波器;AD8376雙通道超低失真中頻VGA;另一個(gè)低通濾波器;以及AD6642雙通道中頻接收器。

圖3.超外差接收器圖;顯示一個(gè)頻道。

該設(shè)計(jì)采用 140MHz IF 和 20MHz 帶寬,因此器件可以交流耦合。

AD5356在200 Ω負(fù)載下性能最佳,但AD8376的輸入阻抗為150 Ω。因此,為了抑制混頻器輸出雜散并提供更好的阻抗匹配,差分LC濾波器必須具有200 Ω輸入阻抗和150 Ω輸出阻抗。在必須通過(guò)尖銳濾波器抑制輸出帶信號(hào)的應(yīng)用中,可以使用差分SAW濾波器,但這會(huì)在接收器信號(hào)鏈中引入損耗和群延遲。差分四階帶通巴特沃茲濾波器可能適用于許多無(wú)線接收器,因?yàn)镽F濾波器可以為帶外干擾提供足夠的衰減。

表 3.ADL5356和AD8376接口和增益參數(shù)

|

ADL5356 測(cè)試條件 |

VS = 5 V, TA = 25°C, fRF = 1900 MHz, fLO = 1760 MHz, LO power = 0 dBm |

|

|

參數(shù) |

值 |

評(píng)論 |

|

電壓轉(zhuǎn)換增益 |

14.5分貝 |

Z源 = 50 Ω,差分 Z負(fù)荷= 200 Ω差分 |

|

共模輸出電壓 |

2.5 V |

ADJ 連接到 VS |

|

功率轉(zhuǎn)換增益 |

8.2分貝 |

包括 4:1 IF 端口變壓器和 PCB 損耗 |

|

AD8376 測(cè)試條件 |

VS = 5 V, TA = 25°C, RS = RL = 150 ? at 140 MHz |

|

|

參數(shù) |

值 |

評(píng)論 |

|

差分輸入電阻 |

150 ? |

|

|

電壓轉(zhuǎn)換增益 |

–4 分貝 |

最低數(shù)字設(shè)置 |

| 20分貝 |

最大數(shù)字設(shè)置 |

|

|

輸出阻抗 |

16 kΩ ||0.8 pF |

|

AD8376的電流輸出電路具有高輸出阻抗,因此差分輸出之間需要150 Ω。另一個(gè)差分濾波器必須衰減二次和三次諧波失真分量,因此這個(gè)150 Ω負(fù)載分為兩部分。首先,在AD8376的輸出端安裝一個(gè)300 Ω電阻。另一個(gè)300 Ω電阻由兩個(gè)165 Ω電阻和ADC的3 kΩ輸入阻抗組成。兩個(gè) 165 Ω電阻還為 ADC 輸入提供直流共模電壓。LC濾波器的輸入和輸出阻抗均為300 Ω。完美的源和負(fù)載匹配對(duì)于高中頻應(yīng)用非常重要。完整的界面如圖 4 所示。

圖4.超外差接收機(jī)接口圖及濾波器仿真結(jié)果.

在接收器中,20 dB LNA安裝在混頻器前面。混頻器之后的濾波器具有2 dB的插入損耗;AD8376和ADC之間的濾波器具有1.2 dB的插入損耗。AD8376增益設(shè)置為14 dB,以提供足夠的裕量來(lái)應(yīng)對(duì)溫度變化。接收器的總增益為

20 dB + 8.2 dB – 2 dB + 14 dB – 1.2 dB = 39 dB.

為了將ADC輸入電壓限制在2 V p-p以下,將功率傳輸?shù)?50-Ω電阻(300 Ω ||(165 ? × 2) ||3 k Ω) 應(yīng)小于 5.2 dBm。因此,對(duì)于單音信號(hào),接收器的最大輸入功率為–33.8 dBm。如果輸入信號(hào)是10 dB PAR調(diào)制信號(hào),則使用此增益設(shè)置的最大輸入信號(hào)為–40.8 dBm。

發(fā)射機(jī)接口設(shè)計(jì)和增益計(jì)算

對(duì)于Tx通道設(shè)計(jì),ZIF和超外差架構(gòu)具有相似的接口特性,并且都需要TxDAC和調(diào)制器之間的直流耦合。大多數(shù)調(diào)制器的IF輸入電路應(yīng)由外部直流電壓偏置;TxDAC輸出可在直流耦合模式下為調(diào)制器提供直流偏置。大多數(shù)高速DAC具有電流輸出,因此需要一個(gè)輸出電阻來(lái)為調(diào)制器產(chǎn)生輸出電壓。?

圖5所示為超外差或ZIF發(fā)送器,采用AD9122 TxDAC、低通濾波器、ADL537x正交調(diào)制器、另一個(gè)RF濾波器、ADF4350頻率合成器、數(shù)控VGA、功率放大器和AD562x DAC實(shí)現(xiàn),用于控制功率放大器(PA)的柵極電壓。

圖5.變送器圖。

對(duì)于AD9122,滿量程輸出電流可以設(shè)置在8.66 mA至31.66 mA之間。對(duì)于大于20 mA的滿量程電流,無(wú)雜散動(dòng)態(tài)范圍(SFDR)會(huì)降低,但DAC的輸出功率和ACPR會(huì)隨著滿量程電流設(shè)置的降低而降低。一個(gè)合適的折衷方案是0 mA至20 mA電流輸出,由20 mA交流電流組成,電流和10 mA直流電平。

表 4.AD9122和ADL5372接口和增益參數(shù)

|

AD9122 測(cè)試條件 |

AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V |

|

|

參數(shù) |

值 |

評(píng)論 |

|

滿量程輸出電流 |

8.66毫安 |

最小數(shù)字滿量程設(shè)置 |

| 31.66毫安 | 最大數(shù)字滿量程設(shè)置 | |

|

輸出電阻 |

10兆安 |

|

|

ADL5372 測(cè)試條件 |

VS = 5 V, TA = 25°C, fLO = 1900 MHz, fIF = 140 MHz |

|

|

參數(shù) |

值 |

評(píng)論 |

|

輸出功率 |

7.1分貝 |

VIQ = 1.4 V p-p differential |

|

I 和 Q 輸入偏置電平 |

0.5 V |

推薦 |

|

差分輸入阻抗 |

2900 kΩ |

|

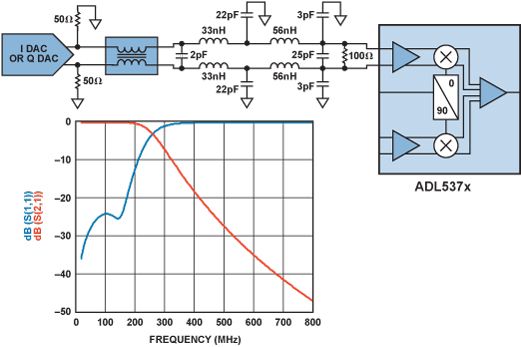

ADL5372的輸入電路需要0.5 V共模電壓,該電壓由流過(guò)50 Ω電阻的10 mA直流電流提供。0mA 至 20mA 交流電流由兩個(gè) 50 Ω電阻和一個(gè) 100 Ω 電阻共享。因此,調(diào)制器輸入之間的交流電壓為20 mA ×((50 × 2) || 100) = 1 V p-p。TxDAC和調(diào)制器之間的濾波器可去除不需要的頻率成分。濾波器的輸入和輸出阻抗為100 Ω。完整的界面如圖 6 所示。

圖6.直流耦合發(fā)射機(jī)IF接口圖及濾波器仿真結(jié)果

采用50 Ω輸出時(shí),ADL5372的電壓轉(zhuǎn)換增益為0.2 dBm。對(duì)于13 dB PAR調(diào)制器信號(hào),Tx數(shù)字預(yù)失真過(guò)程的平均功率必須至少降低15 dB。ADL5372采用1 V p-p單音輸入時(shí),調(diào)制器的平均輸出功率為7.1 dBm – 2.9 dBm = 4.2 dBm。如果考慮低通濾波器的2.2 dBm插入損耗,峰值輸出功率為4.2 dBm – 2.2 dBm = 2 dBm。在這種狀態(tài)下,調(diào)制器輸出端的平均輸出功率為–10 dBm。

對(duì)于11 dBm的平均功率信號(hào),Tx信號(hào)鏈中需要一個(gè)具有26 dBm P1dB的PA驅(qū)動(dòng)器。如果需要2 dB插入損耗RF濾波器來(lái)抑制調(diào)制器的LO饋通和邊帶輸出,則增益模塊和PA驅(qū)動(dòng)器必須提供總計(jì)21 dB的增益。本應(yīng)用建議使用集成增益模塊、數(shù)字控制衰減器和PA驅(qū)動(dòng)器的ADL5243 VGA。

結(jié)論

本文介紹ADC解調(diào)器、IF VGA、混頻器和模擬端口的ZIF和超外差接收器差分接口,以及TxDAC和FMOD之間的發(fā)送器差分接口,將ADI公司的器件用于信號(hào)鏈的有源部分。給出了為這些電路設(shè)計(jì)的應(yīng)用濾波器的增益計(jì)算和仿真結(jié)果。

審核編輯:郭婷

-

放大器

+關(guān)注

關(guān)注

145文章

14096瀏覽量

216225 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3629瀏覽量

107370 -

RF

+關(guān)注

關(guān)注

65文章

3170瀏覽量

168498

發(fā)布評(píng)論請(qǐng)先 登錄

差分接口改善射頻收發(fā)器典型設(shè)計(jì)案例

采用AD9361高性能高度集成的RF收發(fā)器

差分接口優(yōu)化射頻收發(fā)器設(shè)計(jì)介紹

什么是用于RF收發(fā)器的簡(jiǎn)單基帶處理器?

借助差分接口改善射頻收發(fā)器設(shè)計(jì)性能

借助差分接口優(yōu)化射頻收發(fā)器設(shè)計(jì)性能

AD9361 RF捷變收發(fā)器的性能及應(yīng)用

25-Gbps收發(fā)器使FPGA解決方案的性能提高了兩倍多

如何使用RF收發(fā)器實(shí)現(xiàn)簡(jiǎn)單的基帶處理器

如何使用差分接口的優(yōu)勢(shì)提高射頻收發(fā)器的性能

差分接口提高了RF收發(fā)器設(shè)計(jì)的性能

差分接口提高了RF收發(fā)器設(shè)計(jì)的性能

評(píng)論