作者:Padraic O’Reilly and Charly El-Khoury

作為許多控制系統(tǒng)的核心,數(shù)模轉換器(DAC)在決定系統(tǒng)性能和精度方面發(fā)揮著關鍵作用。本文將介紹兩款新型精密16位DAC,并展示一些緩沖高速互補電流輸出DAC輸出的想法,這些DAC的性能可與變壓器性能相媲美。

片上系統(tǒng)基準提高了精度

在惡劣環(huán)境中運行的電子系統(tǒng)可能必須承受較大的極端溫度,同時保持其準確性和穩(wěn)定性。此類系統(tǒng)通常需要多個分辨率高達16位的數(shù)模轉換器。DAC輸出電壓的精度最終取決于其基準電壓的精度。通常,對于這種溫度性能水平,將使用單獨的精密基準。然而,現(xiàn)在,新的精密四通道DAC系列包括一個低漂移基準電壓源,其性能足以用作系統(tǒng)基準。

基準電壓源應保持恒定電壓,不受負載、電源變化和溫度的影響。遺憾的是,高性能獨立基準電壓源通常體積大、成本高且耗電,而片內基準電壓源的性能通常很差。

到目前為止,面對將精確DAC與外部基準配對或與低性能片內基準電壓源配對的選擇,系統(tǒng)設計人員經常被迫選擇DAC和外部基準電壓源。他們不能依賴片內基準電壓源的性能,因為其隨溫度變化很大,而且經常缺乏最大TC規(guī)格,因此無法將其用作系統(tǒng)基準電壓源。

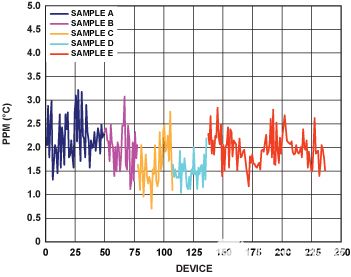

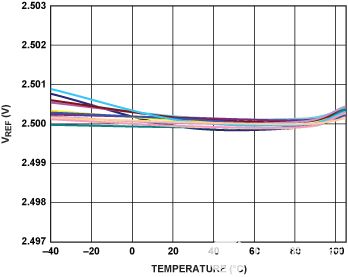

AD5686R改變了這種模式。這款四通道、電壓輸出、16位nanoDAC+數(shù)模轉換器提供片內2.5 V基準電壓源,最大溫度漂移為5 ppm/°C(典型值為2 ppm/°C)。這種性能水平與獨立替代方案相當,允許片內基準電壓源取代系統(tǒng)基準電壓源,從而節(jié)省空間、成本和功耗。5ppm/°C 的最大漂移規(guī)格允許精確計算誤差預算。AD5686R片內基準電壓源的性能如圖1和圖2所示。圖1是包含五個獨立樣品批次的數(shù)百個DAC的溫度系數(shù)散點圖。圖2顯示了9個器件在–40°C至+105°C溫度范圍內的實際輸出電壓。

圖1.幾百個AD5686R DAC的溫度系數(shù)。

圖2.9個典型AD5686R DAC的基準電壓與溫度的關系

方法:對于基準電壓源,溫度系數(shù)(TC)通常使用盒法確定,該方法評估指定溫度范圍內的最大電壓變化。TC,以ppm/°C表示,計算如下

其中

VREFmax 大是在整個溫度范圍內測量的最大基準輸出。

VREFmin 是在整個溫度范圍內測量的最小基準輸出。

VREFnom是標稱基準輸出電壓。

溫度范圍是指定的溫度范圍 (°C)。

低溫度系數(shù)是通過加熱生產中的器件并調整輸出電壓以補償溫度范圍內的曲率來實現(xiàn)的。緊密匹配可確保電阻差不會影響基準電壓源的性能,還允許DAC實現(xiàn)令人印象深刻的±2 LSB積分非線性(INL)規(guī)格。

關于AD5686R/AD5685R/AD5684R

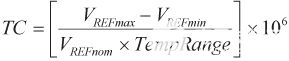

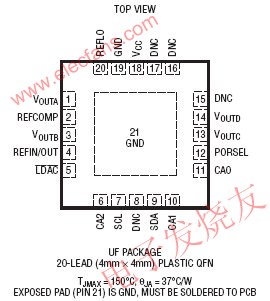

AD5686R/AD5685R/AD5684R是nanoDAC+系列的成員,是四通道、低功耗、16/14/12位DAC,具有緩沖電壓輸出。nanoDAC+系列旨在滿足對數(shù)模轉換器日益增長的需求,這些轉換器具有精度、易操作性和小封裝尺寸。這些新器件包括一個片內 2.5V、2ppm/°C 基準電壓源,默認情況下該基準電壓源處于啟用狀態(tài)。增益選擇引腳將滿量程輸出設置為2.5 V (增益 = 1)或5 V (增益 = 2)。這些器件采用 2.7V 至 5.5V 單電源供電,最大增益誤差為 0.1%,最大失調誤差為 2mV,并保證單調性。采用 LFCSP(3 mm × 3mm)和 TSSOP 封裝,其 4kV ESD 額定值使其非常堅固耐用。DAC 輸入通過 1.8V SPI 兼容接口進行編程。上電復位電路確保DAC輸出高達0 V的電源并保持該電壓,直到發(fā)生有效寫入。復位引腳允許異步復位。基準輸出引腳允許片內基準在外部用作系統(tǒng)基準。菊花鏈功能使系統(tǒng)具有更高的通道數(shù)。外部基準電壓源版本AD5686/AD5685/AD5684允許所有通道以最低成本共享單個基準電壓源。使用這些DAC的多通道系統(tǒng)的一部分如圖3所示。

圖3.系統(tǒng)框圖的一部分,顯示由Blackfin DSP控制的AD5686R和AD5686。

電壓開關、16位DAC提供低噪聲、快速建立和改進的線性度

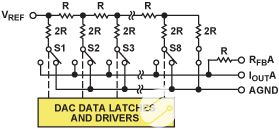

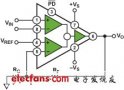

電阻階梯乘法DAC基于近40年前推出的改變游戲規(guī)則的10位CMOS AD7520,最初與反相運算放大器一起使用,放大器的求和點(I奧塔),提供了一個方便的虛擬地面(圖4)。

圖4.CMOS倍增DAC架構。

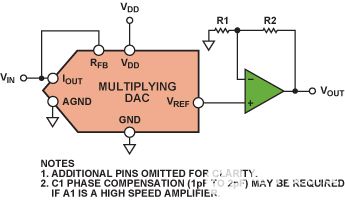

但是,它們也可以用于提供同相電壓輸出的電壓開關配置,但有一些限制,運算放大器用作電壓緩沖器(圖 5)。這里的參考電壓,V在,應用于 I外和輸出電壓 V外,可在 V 處使用裁判.為此目的進行了優(yōu)化的 12 位版本很快可用。

圖5.在電壓開關模式下乘以DAC。

快進到現(xiàn)在:隨著單電源系統(tǒng)變得越來越普遍,設計人員面臨的挑戰(zhàn)是,既要保持較高電壓下的性能水平,又要控制功耗。對具有更高分辨率(至16位)的設備的需求已經增長,能夠在這種模式下使用。

在電壓開關模式下使用乘法DAC的明顯優(yōu)勢是不會發(fā)生信號反轉,因此正基準電壓產生正輸出電壓。但是R-2R梯形架構在這種模式下使用時也有一個弱點。與在電流導引模式下使用相同的DAC相比,與R-2R梯形圖串聯(lián)使用的N溝道開關的非線性電阻會降低積分線性度(INL)。

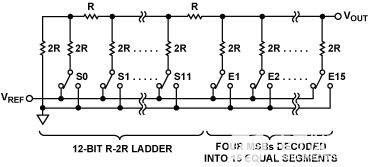

新型高分辨率DAC如AD5541A(如圖6所示)旨在克服DAC倍增的限制,同時保持電壓開關的優(yōu)勢。AD5541A采用部分分段的R-2R梯形網絡和互補開關,在?40°C至+125°C、11.8 nV/√Hz噪聲和1 μs建立時間的整個額定溫度范圍內,無需調整即可在16位下實現(xiàn)±1 LSB精度。

圖6.AD5541A架構

性能特點

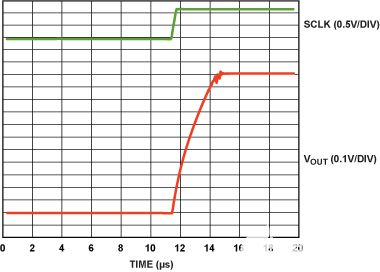

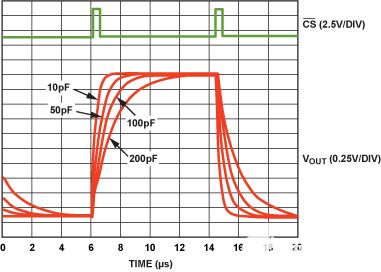

建立時間:圖7和圖8比較了電壓模式下乘法DAC和AD5541A各自的建立時間。當輸出上的容性負載最小化時,AD5541A的建立時間約為1 μs。

圖7.倍增DAC建立時間。

圖8.AD5541A建立時間

噪聲頻譜密度:表1比較了AD5541A和乘法DAC的噪聲頻譜密度。AD5541A在10 kHz時的性能稍好一些,在1 kHz時的性能要好得多。

表 1.AD5541A的噪聲頻譜密度與乘法DAC的關系

|

代數(shù)轉換器 |

NSD @ 10 kHz (nV/√Hz) |

NSD @ 1 kHz (nV/√Hz) |

|

AD5541A |

12 | 12 |

|

多米達克 |

30 | 140 |

積分非線性:積分非線性測量消除增益和失調誤差后DAC的理想輸出與實際輸出之間的最大偏差。與R-2R網絡串聯(lián)使用的交換機可能會影響INL。乘法DAC通常采用NMOS開關。在電壓開關模式下使用時,NMOS 開關的源極連接到基準電壓,漏極連接到梯形圖,柵極由內部邏輯驅動(圖 9)。

圖9.乘法DAC開關。

對于在 NMOS 器件中流動的電流,V一般事務人員必須大于閾值電壓 VT.在電壓開關模式下,V一般事務人員= V邏輯– V在必須大于 VT= 0.7 V.

乘法DAC的R-2R梯形圖設計用于將電流均勻地分配到每個支路。這要求從每條腿的頂部看,對地面的整體阻力完全相同。這可以通過縮放開關來實現(xiàn),其中每個開關的大小與其導通電阻成正比。如果一條支路的電阻發(fā)生變化,流過該支路的電流就會發(fā)生變化,從而導致線性誤差。V在不能大到關閉開關,但必須大到足以保持開關電阻較低,因為 V 的變化在影響 V一般事務人員因此,會導致導通電阻的非線性變化,如下所示:

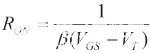

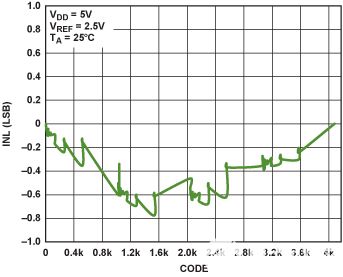

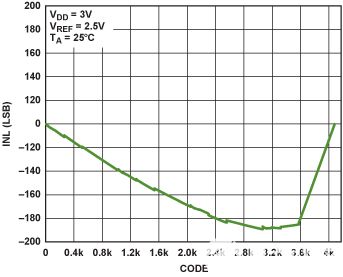

導通電阻的這種變化會使電流不平衡并降低線性度。因此,乘法DAC上的電源電壓不能降低太多。相反,基準電壓不應超過AGND的1 V,以保持線性度。采用5 V電源時,從1.25 V基準電壓源移至2.5 V基準電壓源時,線性度開始下降,如圖10和圖11所示。當電源電壓降至3 V時,線性度完全消失,如圖12所示。

圖 10.一 的 INL外反向模式下的乘法DAC,VDD= 5 V, V裁判= 1.25 V.

圖 11.一 的 INL外反向模式下的乘法DAC,VDD= 5 V, V裁判= 2.5 V.

圖 12.反向模式下乘法DAC的INL,VDD= 3 V, V裁判= 2.5 V.

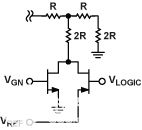

為了將這種影響降至最低,AD5541A使用互補的NMOS/PMOS開關,如圖13所示。現(xiàn)在,開關的總導通電阻來自NMOS和PMOS開關的并聯(lián)貢獻。如前所述,NMOS開關的柵極電壓由內部邏輯控制。內部產生的電壓,VGN,設置理想的柵極電壓以平衡 NMOS 的導通電阻和 PMOS 的導通電阻。開關的尺寸可隨代碼縮放,因此導通電阻隨代碼縮放。因此,電流將縮放,并保持精度。由于基準輸入的阻抗隨代碼而變化,因此應由低阻抗源驅動。

圖 13.互補的 NMOS/PMOS 交換機。

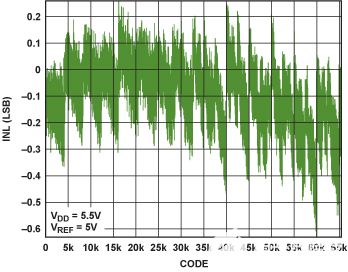

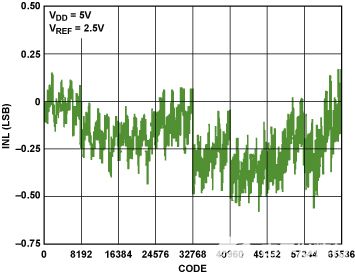

圖14和圖15顯示了采用5 V和2.5 V基準電壓源時AD5541A的INL性能。

圖 14.AD5541A的INL,VDD= 5.5 V, V裁判= 5 V。

圖 15.AD5541A的INL,VDD= 5.5 V, V裁判= 2.5 V.

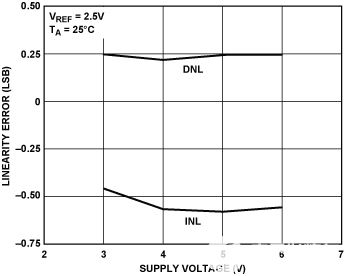

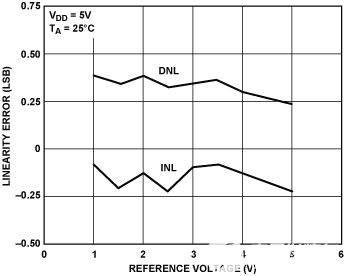

圖16和圖17顯示,在很寬的基準電壓和電源電壓范圍內,線性度變化很小。DNL 的行為與 INL 的行為類似。AD5541A線性度在整個溫度和電源電壓范圍內指定;基準電壓可以從2.5 V變?yōu)殡娫措妷骸?/p>

圖 16.AD5541A INL與電源電壓的關系

圖 17.AD5541A INL與基準電壓的關系

有關AD5541A的更多信息

AD5541A串行輸入、單電源、電壓輸出nanoDAC+數(shù)模轉換器提供16位分辨率和±0.5 LSB(典型積分和差分非線性)。它非常適合在電壓開關模式下使用乘法DAC的應用。它在溫度和電源電壓范圍內均表現(xiàn)良好,可實現(xiàn)出色的線性度,可用于需要精密直流性能和快速建立的 3V 至 5V 系統(tǒng)。使用2 V至電源電壓范圍的外部基準電壓,無緩沖電壓輸出可以驅動0 V至V的60 kΩ負載裁判.該器件具有 1μs 建立至 1/2 LSB、11.8nV/√Hz 噪聲和低毛刺,非常適合部署在各種醫(yī)療、航空航天、通信和工業(yè)應用中。其3線、低功耗SPI兼容串行接口的時鐘頻率最高可達50 MHz。 AD5541A采用2.7 V至5.5 V單電源供電,功耗僅為125 μA。 該器件采用 8 引腳和 10 引腳 LFCSP 封裝以及 10 引腳 MSOP 封裝,額定溫度范圍為 –40°C 至 +125°C,千兆以太網價為 6.25 美元/1000 秒。

高速電流輸出DAC緩沖器

變壓器通常被認為是將高速電流輸出DAC的互補輸出轉換為單端電壓輸出的最佳選擇,因為變壓器不會增加噪聲或消耗功率。雖然變壓器在處理高頻信號時運行良好,但它們無法處理許多儀器儀表和醫(yī)療應用所需的低頻信號。這些應用需要一個低功耗、低失真、低噪聲、高速放大器將互補電流轉換為單端電壓。這里介紹的三個電路接受來自DAC的互補輸出電流,并提供單端輸出電壓。將最后兩個的失真與變壓器解決方案進行比較。

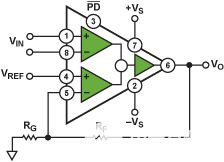

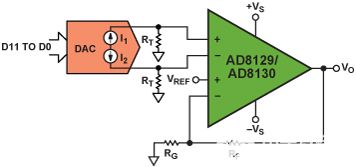

差動放大器:AD8129和AD8130差分至單端放大器(圖1)用于第一個電路(圖2)。它們在高頻下具有極高的共模抑制。AD8129在增益為10或更高的時保持穩(wěn)定,而AD8130在單位增益下保持穩(wěn)定。其用戶可調增益可通過兩個電阻R的比值進行設置F和 RG.無論增益設置如何,AD8129和AD8130引腳1和引腳8上的輸入阻抗都非常高。基準電壓 (V裁判,引腳4)可用于設置偏置電壓,該偏置電壓乘以與差分輸入電壓相同的增益。

圖1.AD8129/AD8130差動放大器

圖2.采用AD8129/AD8130的DAC緩沖器

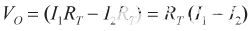

公式1和公式2顯示了放大器輸出電壓與DAC互補輸出電流之間的關系。端接電阻RT執(zhí)行電流-電壓轉換;R的比率F和 RG確定增益。V裁判在公式 2 中設置為 0。

|

(1) |

| (2) |

在圖2中,該電路與四通道高速、低功耗、14位DAC配合使用,其中互補電流輸出級可提高低功耗DAC的速度并降低失真。

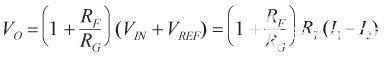

圖3顯示了使用DAC和AD8129時電路的無雜散動態(tài)范圍(SFDR)與頻率的函數(shù)關系,與RF= 2 kΩ,RG= 221 ?,RT= 100 Ω,并且VO= 8 V p-p,電源電壓的兩個值。之所以選擇AD8129,是因為與AD8130相比,它提供大輸出信號,在G = 10時穩(wěn)定,并且具有高增益帶寬積。在這兩種情況下,SFDR 通常都優(yōu)于 55 dB,超過 10 MHz,在較低的電源電壓下改善了大約 >3 dB。

圖3.DAC和AD8129的失真(帶V)O= 8 V 峰峰值

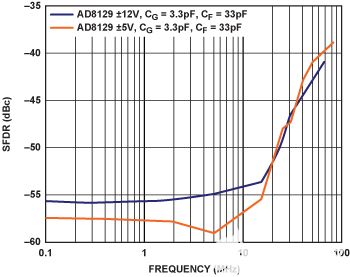

單位增益下的運算放大器:第二個電路(圖4)使用具有兩個R的高速放大器T電阻。放大器簡單地轉換互補電流,I1和我2,變成單端輸出電壓,VO通過RT.這個簡單的電路不允許使用放大器作為增益模塊進行信號放大。

圖4.采用運算放大器的簡單差分至單端轉換器

等式 3 顯示了VO和DAC輸出電流。失真數(shù)據(jù)由5 pF電容與R并聯(lián)測量T.

|

(3) |

為了演示該電路的性能,DAC與運算放大器ADA4857和ADA4817配對,R T= 125 Ω(和 CT= CF= 5 pF 與 R 并聯(lián)T用于穩(wěn)定性和低通濾波)。單通道ADA4857-1和雙通道ADA4857-2分別是單位增益穩(wěn)定的高速電壓反饋型放大器,具有低失真、低噪聲和高壓擺率等特性。該器件是超聲、ATE、有源濾波器和 ADC 驅動器等各種應用的理想解決方案,具有 850MHz 帶寬、2800V/μs 壓擺率和 10ns 建立時間(0.1%),同時采用 5mA 靜態(tài)電流工作。ADA4857-1和ADA4857-2具有寬電源電壓范圍(5 V至10 V),非常適合需要寬動態(tài)范圍、精度、高速和低功耗的系統(tǒng)。

單通道ADA4817-1和雙通道ADA4817-2快速場效應晶體管 ?放大器是單位增益穩(wěn)定的超高速電壓反饋型運算放大器,具有FET輸入。它們采用ADI專有的eXtra快速互補雙極性(XFCB)工藝開發(fā),可實現(xiàn)超低噪聲(4 nV/√Hz和2.5 fA/√Hz)和非常高的輸入阻抗。它們具有 1.3pF 輸入電容、2mV 最大失調電壓、低功耗 (19mA) 和寬 ?3dB 帶寬 (1050MHz),非常適合數(shù)據(jù)采集前端、光電二極管前置放大器和其他寬帶跨阻應用。這些器件具有 5V 至 10V 電源電壓范圍,能夠采用單電源或雙電源供電,適用于各種應用,包括有源濾波、ADC 驅動和 DAC 緩沖。

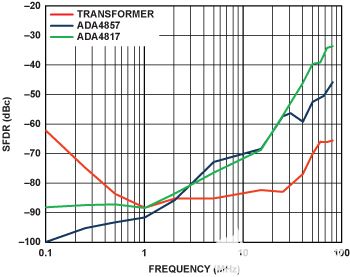

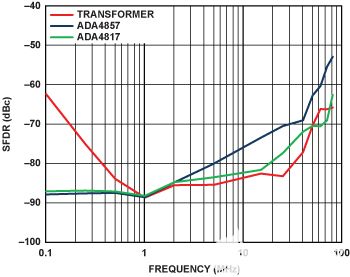

圖5比較了該電路在V時的失真與頻率O= 500 mV p-p,使用變壓器的電路。變壓器的失真比放大器小,放大器在高頻時增益降低,但在低頻時失真越來越嚴重。在這里,SFDR在有限的范圍內可實現(xiàn)接近90 dB的SFDR,優(yōu)于70 dB至10 MHz。

圖5.DAC、ADA4857和ADA4817的失真與V電壓O= 500 mV 峰峰值,RL = 1 kΩ。

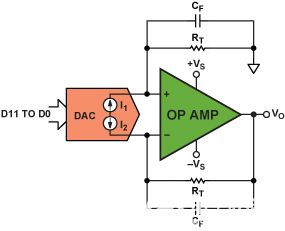

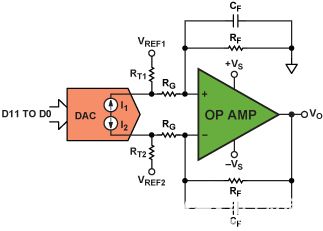

帶增益的運算放大器:第三個電路(圖6)也使用相同的高速運算放大器,但包括一個阻性網絡,該網絡使放大器與DAC保持距離,允許增益設置,并可靈活地使用兩個基準電壓中的任何一個V調整輸出偏置電壓參考文獻1和 V參考文獻2.

圖6.差分至單端,具有增益和偏置能力。

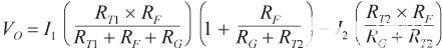

公式4定義了DAC輸出電流與放大器輸出電壓之間的關系,V時參考文獻1= V參考文獻1= 0。為了匹配放大器網絡的輸入阻抗,兩個終端電阻R T1和 RT2,必須單獨設置,同時考慮到放大器的特性。

| (4) |

圖7比較了這種配置下放大器與變壓器電路的失真。RT1= 143 Ω,RT2= 200 Ω,RF = RG= 499 Ω,CF= 5 pF—用于穩(wěn)定性和高頻濾波—和 RL= 1 kΩ。在這里,ADA4817的性能與高頻變壓器的性能相當,在高達70 MHz的頻率下保持優(yōu)于?70 dBc SFDR。與變壓器相比,兩個運算放大器都保持了出色的低頻保真度。

圖7.DAC、ADA4817和ADA4857的失真(帶V)O= 500 mV 峰峰值

本文展示了使用低失真、低噪聲、高速放大器作為DAC緩沖器的一些優(yōu)勢,比較了它們與變壓器的性能。本文還比較了使用兩種不同放大器架構的三種應用電路,同時給出了DAC和AD8129、ADA4857-1/ADA4857-2和ADA4817-1/ADA4817-2放大器的測量數(shù)據(jù)示例。數(shù)據(jù)顯示,該放大器在低于1 MHz的頻率下優(yōu)于變壓器,并且可以在高達80 MHz時與其性能非常接近。 在考慮功耗和失真方面的權衡時,放大器選擇非常重要。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8958瀏覽量

150735 -

dac

+關注

關注

43文章

2379瀏覽量

193030 -

變壓器

+關注

關注

0文章

1492瀏覽量

4010

發(fā)布評論請先 登錄

DAC及其緩沖器有助于提升系統(tǒng)性能與簡化設計

DAC3482從時鐘發(fā)生器出來的FIFO_OSTR信號連入時鐘緩沖器CDCP1803后才輸出到DA中,時鐘緩沖器起什么作用?

電阻串DAC架構原理

高性能DAQ系統(tǒng)的ADC電壓基準兩級緩沖器優(yōu)化設計

如何提高10位DAC源的線性性能?

如何使用八進制CMOS緩沖器的二象限乘法DAC?

如何提高FPGA的系統(tǒng)性能

使用Hi-Z緩沖器簡化AFE設計的教程

如何測量扇出緩沖器中的附加抖動

歐勝微電子新款DAC產品WM8912,可顯著提高音頻性能

軌至軌DAC輸出緩沖器LTC2655

高速電流輸出DAC緩沖器

現(xiàn)代DAC和DAC緩沖器有助于提升系統(tǒng)性能、簡化設計

模擬DAC38RF8x輸入/輸出緩沖器信息的快速入門方法

現(xiàn)代DAC和DAC緩沖器可提高系統(tǒng)性能和簡化設計

現(xiàn)代DAC和DAC緩沖器可提高系統(tǒng)性能和簡化設計

評論