作為使用PAL、GAL或CPLD器件實現非易失性門控功能的替代方案,這些電路使用串行接口控制的數字電位器(MAX5427或MAX5527)存儲門控信號(模塊或發送)。

下面介紹了通常由 PAL、GAL 或 CPLD 器件實現的非易失性門控功能的簡單替代方案。要“選通”邏輯信號(以阻止或傳輸它),通常使用邏輯門(如AND門),并使用門的第二個輸入來定義門是阻塞還是傳輸施加的信號(圖1)。由于邏輯門執行即時布爾運算,因此它們的運算是組合的,沒有內存。

圖1.AND 門用于門控信號。

如果需要對門進行編程,該門在系統啟動后應始終阻塞或傳輸信號,則必須將“發送/阻塞”邏輯狀態存儲在某種形式的非易失性存儲器中。有兩種基本方法可用于存儲此類邏輯狀態。第一種涉及微控制器與非易失性存儲器(如EEPROM)的組合。如果系統可以等到微控制器從存儲器讀取邏輯狀態并將其應用于硬件引腳(通常通過GPIO引腳),則此方法適用。但是,某些系統要求在啟動時存在發送/塊信號。對于這些,從內存讀取延遲是不可接受的。

第二種方法適用于沒有μC的系統,或者無法等待μC在啟動時從存儲器讀取的系統,它將邏輯狀態存儲在器件中,使其在上電時立即可用。用于此目的的典型可編程邏輯器件是PAL、GAL或CPLD,它們將門控功能與可編程非易失性存儲器相結合。然而,這些器件提供的不僅僅是存儲器門控,對于只需要幾個這樣的門的系統來說,這些器件可能過于合格。此外,它們的封裝相對較大,以適應它們提供的許多邏輯 I/O 引腳。

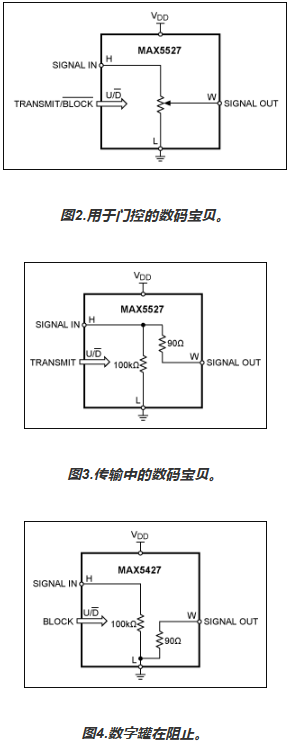

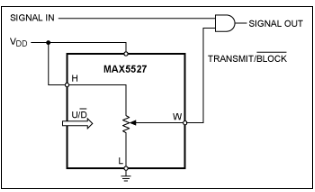

如果只需要幾個非易失性柵極,請考慮使用模擬和混合信號系統中常見的元件——數字電位計或DigiPot(圖2)。將電阻串的L端接地,并將信號路由到電阻串的H端。然后,游標輸出短路至地以進行阻塞,或連接到輸入信號進行傳輸(圖3和圖4)。這些連接僅對 DigiPot 進行編程,使其處于 N 個可能狀態中的兩種:D∈[1,N],其中 N = 抽頭次數。

您可以在電路板或系統測試期間通過其串行接口對 DigiPot 進行編程。在某些DigiPots上找到的上/下接口適用于此目的。選擇非易失性DigiPot時,應考慮以下標準:

DigiPots 通常有 32 個或更多水龍頭(至少需要兩個)。DigiPot游標具有與內部開關相關的電阻,應盡可能小,以避免開關信號失真。典型游標電阻為100Ω至1kΩ(MAX5527游標電阻測量值低至90Ω)。

由于 DigiPot 游標的電阻會隨著電源電壓的增加而減小,因此您應該為 DigiPot 選擇高電源電壓。

為了最大限度地減少信號源的負載,并且不限制DigiPot的信號帶寬,您應該選擇具有高端端到端電阻的DigiPot。100kΩ對于許多應用都是可以接受的。

如果門的狀態必須在非易失性存儲器中編程,請選擇非易失性DigiPot。一些DigiPot具有OTP(一次性編程)功能,可讓您一勞永逸地保存游標的設置。OTP 適用于您不希望以后對門控功能進行更改的情況。必須存儲狀態的門數決定了 DigiPot 的數量,每個包以 1 到 6 個(或更多)的數組形式提供。

DigiPot帶寬決定了通過DigiPot傳輸的信號的最大數據速率。如果這些外加邏輯信號的開關速率對于可用的DigiPot來說太高,則可以使用傳統的(高速)邏輯門,其發射/塊輸入由DigiPot控制(圖5)。

圖5.高速信號的非易失性選通。

審核編輯:郭婷

-

cpld

+關注

關注

32文章

1257瀏覽量

170939 -

存儲器

+關注

關注

38文章

7629瀏覽量

166318 -

電位器

+關注

關注

14文章

1016瀏覽量

67643

發布評論請先 登錄

TPL1401數字電位器易失性和非易失性的區別是什么?

非易失性MRAM的基礎知識匯總

非易失性MRAM基礎知識匯總

非易失性內存有寫入限制嗎?

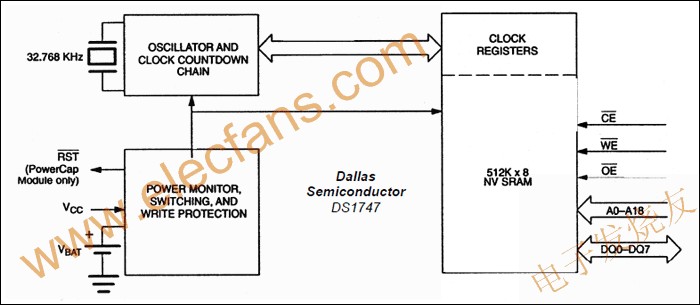

非易失性SRAM DS1747

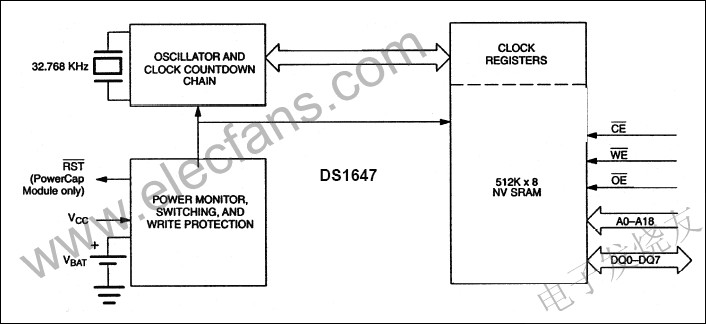

DS1647為512k x 8非易失性靜態RAM

簡單的非易失性門控

簡單的非易失性門控

評論