引言

幾十年來,FPGA產品一直是設計工程師所熟知且經常使用的電子硬件。FPGA通常使用邏輯單元 (LC)來區分邏輯密度。可以根據邏輯單元的數量將FPGA市場可以分為三類:高端、中端和小型FPGA。盡管這些描述會隨時間發生變化,但目前高端FPGA的邏輯單元普遍在500K以上,中端為100K至500K,小型FPGA則少于100K。

從架構的角度來看,許多FPGA供應商長期以來都未將中端FPGA領域視為戰略重點,令人驚訝不已。中端FPGA已成為各類嵌入式、工業、自動化和機器人等應用的最佳選擇。可以說,市場上已經將近十年沒有出現過一款真正的中端FPGA了。

供應商意識到市場對中端FPGA的需求后,經常使用“瀑布式”開發來提供這些產品。基本上就是將針對高端FPGA優化的架構應用于中端 FPGA。雖然這些產品確實能填補中端產品的空白,但并未針對中端FPGA進行特別的優化。因為這些架構本應支持高達10倍的邏輯密度。這種策略可能對FPGA供應商有利,但對于中端FPGA客戶來說,就另當別論了。

滿足各類需求

客戶真正需要的是專為中端市場而設計的中端FPGA,而不是對高端或小型FPGA架構進行一些調整。萊迪思Avant平臺專為中端FPGA設計。與中端FPGA市場上的現有FPGA相比,Avant平臺具有以下優勢:

功耗遠低于同類競品器件

封裝尺寸遠小于同類競品器件

25Gbps SERDES

支持DDR3L/DDR4/LPDDR4和DDR5

下一代安全性能

可靠性更高

萊迪思半導體長期以來專注于低功耗FPGA,服務于低密度FPGA市場。事實上,萊迪思的出貨量是所有其他傳統FPGA供應商的總和。如今該公司正憑借Avant平臺強勢打入中端FPGA市場。通過Avant平臺,設計人員除了可以一如既往地獲得萊迪思提供的低功耗、密度優化等特性外,還能獲得更高的器件密度和性能。因此該系列器件可以提供更多高端功能,但同時具有中端(和小型)器件的尺寸和低功耗。

Avant FPGA平臺的潛在應用十分廣泛。在工業領域,它可以用于網絡控制器、PLC、網絡邊緣計算、機器視覺和工業機器人。得益于其強大的DSP性能,它在汽車網絡和軟件定義無線電領域也很有價值。此外,通用無線通信、室內5G小基站和5G前傳應用也是Avant的潛在應用領域。

Avant實現了一系列高帶寬I/O標準,如PCIe Gen4、LPDDR4和DDR5,并提供強大的DSP和負載加速性能。Avant FPGA架構支持的時鐘速率高達350 MHz,嵌入式RAM模塊和DSP乘法/累加模塊支持的時鐘速率達625 MHz。這些器件是行業中提供25 Gbps SERDES功能的尺寸最小的FPGA。

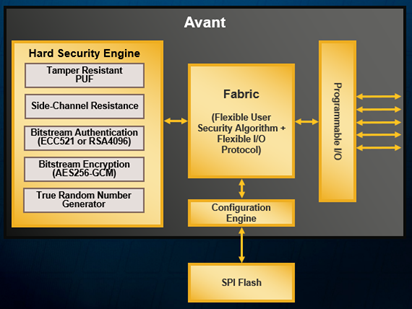

充分保障安全

所有嵌入式設計的安全性應當是首要考慮因素。為此,萊迪思工程師確保Avant平臺包含各類安全功能,如AES256-GCM、ECC、RSA、防篡改和物理不可克隆功能(PUF)。這些功能能夠加密和驗證配置和用戶數據,從而確保FPGA即便受到惡意攻擊也能安全無虞。軟失效檢測和糾正可快速檢測導致軟失效的環境因素,便于執行適當的操作。

身份驗證和加密可以保護FPGA的配置位流。用戶模式的安全功能則通過硬核加密引擎實現,這些引擎可作為FPGA架構中的嵌入式IP模塊使用。針對側信道和故障注入攻擊的防篡改功能則通過密鑰和敏感數據的歸零來實現。

除了強大的安全性能外,Avant器件還能夠抵御α粒子引起的瞬態軟失效故障。單粒子翻轉的檢測和恢復需要快速進行,從而保障系統正常運行,增強可靠性。

最小化功耗

Avant平臺降低功耗的一種策略是邏輯實現使用的是一個四輸入LUT,而不是六輸入LUT。四輸入LUT只需要16個SRAM配置位來對LUT進行編程,而六輸入LUT需要64個SRAM配置位。

功耗優化的另一個方面是減少高電容網絡。較高的扇出網絡會通過連接到高電容金屬布線的高驅動強度緩沖器產生更大的電容。Avant架構則利用小型多路復用器和低扇出網絡來降低功耗。還值得注意的是,Avant器件采用16納米FinFET工藝制造,經過優化極大降低了漏電流。

豐富的架構

充足的DSP模塊對于中端FPGA中的各種信號處理和AI功能至關重要。Avant器件提供多達1800個18 x 18乘法器,能夠以625 MHz 的頻率全流水線運行。該DSP模塊還可以作為三個9 x 9或四個8 x 8乘法器,內置一個18位預加器和48位累加器。這些配置模式大大優于傳統器件。此外,乘法器可以級聯為27 x 18、36 x 18、27 x 27或36 x 36的配置。

I/O靈活性是Avant架構的基石。FPGA提供SERDES和并行I/O標準,可滿足各種應用的需求。就SERDES標準而言,包括了PCIe Gen 4、25G以太網、DP/eDP、SLVS-EC、CoaXPress、JESD204B/C、eCPRI/CPRI、RoE和SyncE。此外,為了加速PCIe的實現,還提供了一個硬核PCIe控制器。GPIO支持多種接口,包括LVCMOS 0.9-3.3V、1.8 Gbps MIPI D-PHY、1.6 Gbps LVDS/subLVDS、I3C、SGMII和LVDS 7:1。

內部嵌入式存儲器采用36 kbit存儲塊,支持單端口、偽雙端口(1R1W)、真雙端口(2RW)和ROM配置。萊迪思Radiant軟件存儲器編譯器可以匯編和布局/布線最大64 kbit×256位(總共16 Mbit)的內部存儲器塊。存儲器提供最高36 Mbit容量。

外部存儲器接口包括DDR4、DDR5和LPDDR4(運行速度達2.4 Gbit/s)以及傳統標準的DDR3L(1.866 Gbit/s)和LPDDR2(1.066Gbit/s)。這些實現都基于帶有靈活軟控制器的硬核MEMPHY。軟核存儲器控制器支持錯誤糾正碼(ECC)。

小尺寸低功耗封裝

從封裝角度看,萊迪思設計團隊的目標是以更低成本的封裝提供更小的芯片,他們也做到了這一點。這一目標的實現得益于更低功耗的要求,從而使用更小的裸片和更低成本的封裝,200K邏輯單元的芯片尺寸小至11x9 mm,500K邏輯單元的芯片尺寸小至15x13 mm。

萊迪思Radiant和萊迪思Propel工具功能強大且直觀易用,用戶可以使用便捷的設計向導和精確的實現高效地開發FPGA應用。這包括了編譯器優化和分析,實現快速且可預測的設計收斂。可以通過統一的設計數據庫、設計約束流程和全流程的時序分析實現這一目標。

Avant提供了一整套IP來支持該平臺。有些是硬核(定制邏輯)配置,用于優化面積和性能,另一些則以軟核形式提供(通過使用邏輯單元),實現最大的靈活性。PCIe就是硬核IP的一個例子,而外部存儲器接口則使用MEMPHY和軟控制器實現了部分硬化。此外,如果不使用軟核,則不會占用任何空間。

專為中端FPGA設計

Avant平臺設計初衷就是服務于中端FPGA市場。萊迪思在這一領域的投入讓該平臺具備了領先的強大功能、小尺寸和高性能。該平臺現代化的功能集支持使用最新的接口標準進行互連,進一步增強了其領先地位。目前萊迪思Radiant和Propel設計工具已經支持Avant平臺,便于萊迪思客戶快速應用已有的軟件知識。各類IP和開發板也已支持該平臺。了解更多信息,請前往萊迪思Avant網站頁面。

審核編輯:湯梓紅

-

dsp

+關注

關注

555文章

8142瀏覽量

355160 -

FPGA

+關注

關注

1643文章

21954瀏覽量

613996 -

控制器

+關注

關注

114文章

16959瀏覽量

182870 -

萊迪思

+關注

關注

2文章

230瀏覽量

39396

原文標題:萊迪思Avant平臺:專為中端FPGA市場量身打造

文章出處:【微信號:Latticesemi,微信公眾號:Latticesemi】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

萊迪思半導體四季度財報發布,營收略高于市場預期

萊迪思推出全新Avant? 30和Avant? 50器件

羅萊迪思榮獲「工業設計界的奧斯卡」——日本G Mark國際設計獎!

萊迪思Avant平臺:專為中端FPGA市場量身打造

萊迪思Avant平臺:專為中端FPGA市場量身打造

評論