邏輯功能的門級實現受門扇入的限制。本文探討了邏輯分解、分組和電平增加,以在有限的輸入門下實現邏輯功能。

了解如何利用 組合邏輯功能 并簡化組合邏輯電路!為了理解與這些過程相關的挑戰,讓我們首先建立一個真實世界的例子來演示這個概念。

為什么柵極輸入的數量有限?

想象一下,我們正在設計一個邏輯系統,以便在六個緊急出口中的任何一個打開時啟動警報信號(S)。報警系統的輸出通常為高電平(邏輯 1),并通過變低(邏輯

0)來啟動報警。門傳感器(標記為 a 到 f)在關閉時分別輸出邏輯 0,打開時輸出邏輯 1。

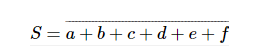

我們可以很容易地將此邏輯函數表示為:

在具有六輸入NOR門的單級邏輯功能中實現這一點非常簡單。從理論上講,我們可以擴展圖1所示的雙輸入NOR門的設計,以支持所需的6個輸入。

圖1. CMOS 2 輸入 NOR 柵極

六個并聯的NMOS晶體管不一定是問題。然而,由于電源電壓有限(V日嘎)。因此,基本邏輯門通常限制為某個最大輸入數(通常為四個)。邏輯門的輸入數量稱為扇入。

使用具有有限輸入的門進行分組設計

對于我們的報警系統問題,我們可以對輸入進行分組和因子分解,以允許我們使用門實現組合電路設計,每個門最多有三個輸入。對于低壓邏輯過程來說,這是一個更合理的扇入。

實現此目的的一種可能的分解是:

這里的結果是一個兩電平邏輯系統,如圖2所示,其中所有三個門最多有三個輸入。

圖2. 報警系統的門級邏輯限制為最多 3 個輸入門

實現具有有限扇入的復雜邏輯功能

對于更復雜的邏輯功能,可以根據需要重復分解、重新分組和增加邏輯電平數的過程,直到所有門都達到所用邏輯技術的最大扇入限制。

讓我們仔細看看一個更復雜的邏輯函數,由 卡諾地圖 圖3。

圖3. 卡諾地圖

我們可以通過對相鄰 1 的項進行分組,從 Karnaugh 映射中推導出邏輯方程。首先,我們可以對頂行進行分組,如圖 4 所示。

圖4. 卡諾地圖的術語分組

對于頂行,我們可以將部分邏輯函數導出為:

類似地,我們可以創建相鄰 1 項的四個附加分組,如圖 5 所示。

圖5. 卡諾地圖的附加術語分組

對于這四個分組,我們可以推導出邏輯函數的其余項:

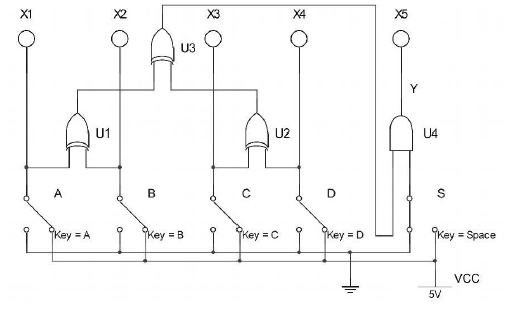

此功能現在可以通過最大扇入為三個的門來實現。由此產生的門級邏輯功能如圖6所示。

圖6. 用于邏輯功能的門級邏輯限制為最大三輸入門

門級邏輯綜合

在現代數字集成電路設計中,最常見的是,邏輯功能轉換為門級實現將通過門級邏輯合成過程執行。數字標準單元邏輯庫將具有一套邏輯門,用于在硬件中創建所需的功能。電子設計自動化(EDA)軟件將轉換以更高級語言描述的邏輯功能,例如

威瑞洛格 變成僅使用庫中可用的門的物理門級實現。

標準單元庫中可用柵極的扇入將受到目標半導體工藝以及電壓和溫度工作條件的限制。因此,EDA

軟件必須執行本文中所述邏輯電平數的分解、重新分組和增加。

門級邏輯仿真

在理想的邏輯仿真中,輸出會隨著輸入的任何變化而瞬時變化。在實際系統中,存在“傳播延遲”,因為輸入電壓變化通過電路中的晶體管傳播以引起輸出電壓的變化。輸出負載以及輸入和輸出信號的上升和下降時間也會影響整個電路信號的傳播特性。

時序圖

讓我們看一下逆變器時序圖的簡單示例,如圖7所示。當輸入 x 改變邏輯狀態時,輸出在延遲后會發生變化。

在本例中,下降輸出傳播延遲df比上升輸出傳播延遲dr更短,斜率更陡。延遲在兩個邏輯電平之間的50%電平上測量。這種類型的不對稱響應將發生在CMOS逆變器中,其中NMOS和PMOS晶體管尺寸相同。NMOS晶體管的較高驅動電流將比PMOS晶體管拉高輸出的速度更快。

圖7. 逆變器的時序圖

時序圖還可用于評估具有多個輸入和門的邏輯電路。在圖8的示例電路中,輸入端的變化 一個 通過第一個 NAND 門傳播到輸出 x 具有輸入至輸出傳播延遲

d.

圖8. 多電平邏輯電路的時序圖

值的變化 x 然后通過第二個 NAND 門傳播到輸出 y 具有額外的傳播延遲 d。因此,總傳播延遲從 一個 自 y 為 2d.

-

電路設計

+關注

關注

6700文章

2525瀏覽量

212363 -

仿真

+關注

關注

51文章

4242瀏覽量

135341 -

邏輯

+關注

關注

2文章

834瀏覽量

29710

發布評論請先 登錄

組合邏輯電路的分析與設計-邏輯代數

基于組合邏輯電路實現方法的探究

Multisim在組合邏輯電路設計中的常用元件和詳細作用分析

使用Matlab實現組合邏輯電路的設計與仿真

使用柵極的組合邏輯電路設計和仿真

使用柵極的組合邏輯電路設計和仿真

評論