無(wú)論你使用圖形化設(shè)計(jì)程序,ANSIC語(yǔ)言還是VHDL語(yǔ)言,如此復(fù)雜的合成工藝會(huì)不禁讓人去想FPGA真實(shí)的運(yùn)作情況。在這個(gè)芯片中的程序在這些可設(shè)置硅片間到底是如何工作的。本文會(huì)使非數(shù)字化設(shè)計(jì)人員明白FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)的基礎(chǔ)知識(shí)及其工作原理。此信息在使用高端設(shè)計(jì)工具時(shí)同樣十分有用,希望可以為理解這一特別技術(shù)提供一些線(xiàn)索。

1FPGA-現(xiàn)場(chǎng)可編程門(mén)陣列

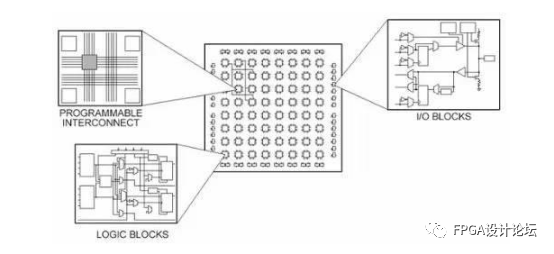

每一塊FPGA芯片都是由有限多個(gè)帶有可編程連接的預(yù)定義源組成來(lái)實(shí)現(xiàn)一種可重構(gòu)數(shù)字電路。

FPGA芯片說(shuō)明書(shū)中,包含了可編程邏輯模塊的數(shù)量、固定功能邏輯模塊(如乘法器)的數(shù)目及存儲(chǔ)器資源(如嵌入式RAM)的大小。FPGA芯片中還有很多其它的部分,但是以上指標(biāo)通常是為特定應(yīng)用選擇和比較FPGA時(shí),最重要的參考指標(biāo)。

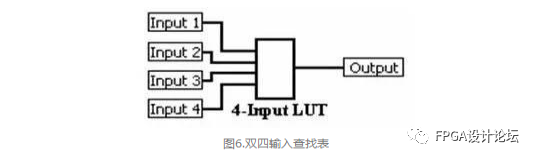

在最底層,可配置邏輯模塊(如片或邏輯單元)有著兩種最基本的部件:觸發(fā)器和查找表(LUT)。這很重要,因?yàn)楦鞣NFPGA家族之所以各不相同,就是因?yàn)橛|發(fā)器和查找表組合的方式不同。例如,Virtex-II 系列的FPGA ,它的片具有兩個(gè)查找表和兩個(gè)觸發(fā)器,而Virtex-5 FPGA的片具有4個(gè)查找表和4個(gè)觸發(fā)器。查找表本身的結(jié)構(gòu)也可能各不相同(4輸入或6輸入)。

表1中列出了在NI LabVIEW FPGA硬件目標(biāo)中使用的FPGA的指標(biāo)。邏輯門(mén)的數(shù)量是一種將FPGA芯片與ASIC技術(shù)進(jìn)行比較的傳統(tǒng)方法,但是它并不能真實(shí)地表述FPGA內(nèi)部的獨(dú)立單元的數(shù)量。這就是Xilinx公司沒(méi)有在新型Virtex-5系列中指定邏輯門(mén)數(shù)量的原因之一。

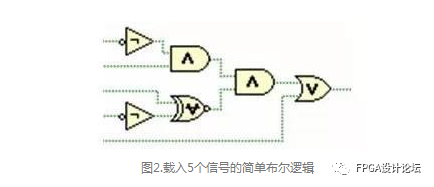

為了更好地理解這些規(guī)格的意義,將編碼考慮為合成的數(shù)字電路模式。對(duì)任何一段合成代碼,或圖形化或文本形式,都有相應(yīng)的電路圖反映邏輯組件該如何連線(xiàn)。通過(guò)一段簡(jiǎn)單布爾邏輯電路了解下相應(yīng)的示意圖。圖2表示的是傳遞5個(gè)布爾信號(hào)并且可圖形化計(jì)算所得的二進(jìn)制值的功能組。

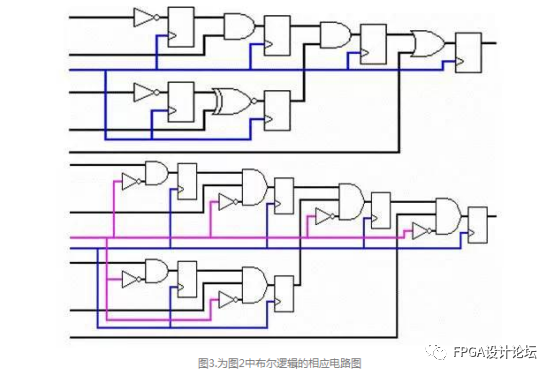

在通常情況下(除LabVIEW SCTL—單周期定時(shí)環(huán)路外),圖2所示相應(yīng)電路圖同圖3所示相近。

雖然很難明白,但是實(shí)際上這里創(chuàng)建了兩個(gè)并行分支的電路。最上面的5條黑線(xiàn)被反饋到第一個(gè)分支,它在每個(gè)布爾操作間添加了觸發(fā)器。最下面的5條黑線(xiàn)構(gòu)成了第二個(gè)邏輯鏈。其中一支路在每步操作之間增加了同步寄存器,另一條邏輯鏈?zhǔn)谴_保執(zhí)行數(shù)據(jù)流的。本電路圖正常工作時(shí)總共需要12個(gè)觸發(fā)器和12個(gè)查找表。

2觸發(fā)器

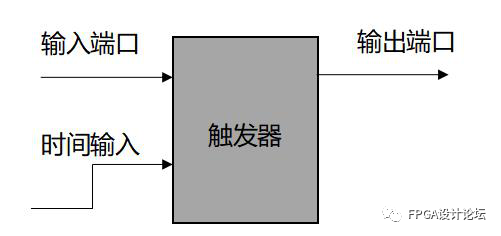

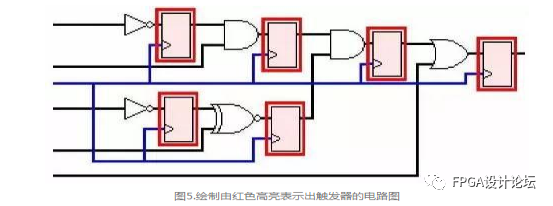

觸發(fā)器是二進(jìn)制移位寄存器,用于同步邏輯以及保存時(shí)鐘(脈沖)周期內(nèi)的邏輯狀態(tài)。在每個(gè)時(shí)間(脈沖)邊沿,觸發(fā)器在輸入時(shí)鎖定1(真)或0(假)值并且保存此值直到下次時(shí)鐘(脈沖)邊沿。在正常情況下,LabVIEW FPGA在每次操作之間都設(shè)置一個(gè)觸發(fā)器,以保證有足夠的時(shí)間來(lái)執(zhí)行每步操作。對(duì)此律的例外只發(fā)生在SCTL結(jié)構(gòu)中寫(xiě)代碼的情況。在這個(gè)特殊的環(huán)路結(jié)構(gòu)中,觸發(fā)器只放置在閉環(huán)迭代的始末段,并且由編程者考慮定時(shí)因素來(lái)決定如何放置。圖5表示的是圖3的上端分支,觸發(fā)器由紅色高亮表示。

3查找表

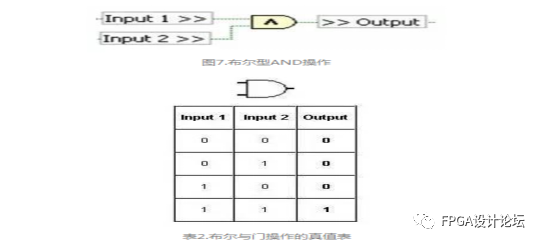

圖6所示示意圖中的其他邏輯電路通過(guò)使用少量查找表形式的隨機(jī)存取存儲(chǔ)器實(shí)現(xiàn)。我們可以簡(jiǎn)單地假定FPGA中系統(tǒng)門(mén)的數(shù)量可參考與非門(mén)(NAND)以及或非門(mén)(NOR)的數(shù)量,但實(shí)際上,所有的組合邏輯(與門(mén)、或門(mén)、與非門(mén)、異或門(mén)等)都是通過(guò)查找表存儲(chǔ)器中的真值表來(lái)實(shí)現(xiàn)。真值表是輸出對(duì)應(yīng)于每個(gè)輸入值組合的預(yù)定義表(現(xiàn)在卡諾圖的重要性在你的頭腦中可能會(huì)慢慢淡化)。以下是對(duì)數(shù)字邏輯電路課程的快速回顧:比如,圖7是布爾邏輯與門(mén)操作過(guò)程。

這是對(duì)數(shù)字邏輯課程的快速回顧:

例如,圖7中顯示了布爾型AND操作。

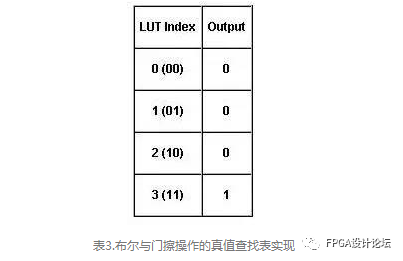

你可以認(rèn)為輸入值是所有輸出值的數(shù)字索引,如表3所示。

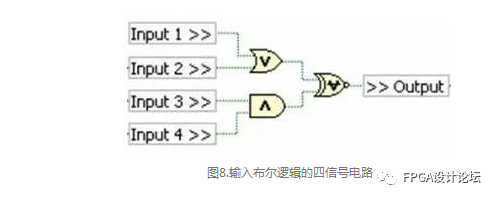

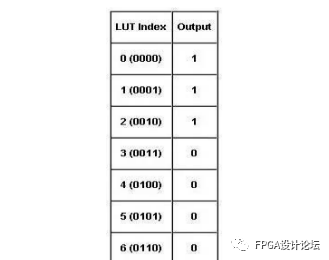

Virtex-II和Spartan-3系列FPGA芯片有著4輸入查找表來(lái)實(shí)現(xiàn)真正的4輸入信號(hào)的16種組合。圖8就是一個(gè)四輸入電路實(shí)現(xiàn)的例子。

表4所示為使用雙四輸入查找表實(shí)現(xiàn)的相應(yīng)的真值表。

Virtex-5系列的FPGA使用雙六輸入查找表,可以通過(guò)6個(gè)不同輸入信號(hào)的64種組合來(lái)實(shí)現(xiàn)真值表。因?yàn)橛|發(fā)器之間的組合邏輯十分復(fù)雜,所以在LabVIEW FPGA中使用SCTL也越來(lái)越重要。下一節(jié)將講述SCTL如何優(yōu)化利用LabVIEW中的FPGA源。

4SCTL

上幾節(jié)中使用的代碼例子假定代碼是設(shè)置在SCTL外部,并為保證執(zhí)行同步數(shù)據(jù)量也同步了附加電路。SCTL是LabVIEW FPGA中一個(gè)特殊結(jié)構(gòu),生成一個(gè)更為優(yōu)化的電路圖,以期望達(dá)到在一個(gè)時(shí)鐘(脈沖)周期內(nèi)執(zhí)行完所有邏輯電路分支。例如,若設(shè)置SCTL在40MHZ運(yùn)行,則所有邏輯電路分支將在25ns內(nèi)執(zhí)行完畢。

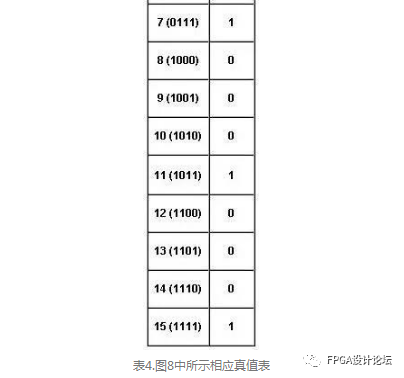

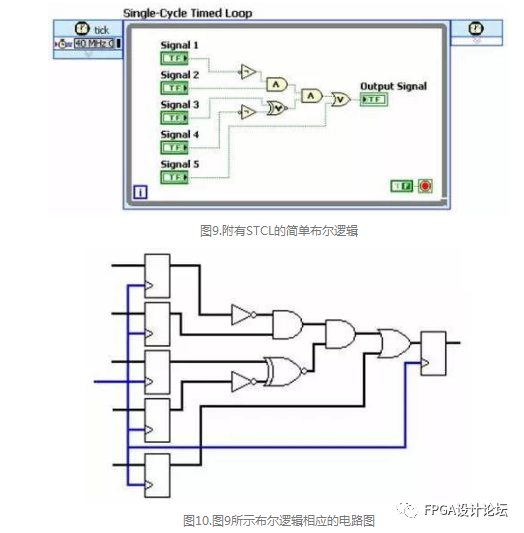

如果在SCTL中設(shè)置前例中同樣的布爾邏輯電路(如圖9所示),則生成如圖10所示的相應(yīng)電路示意圖。

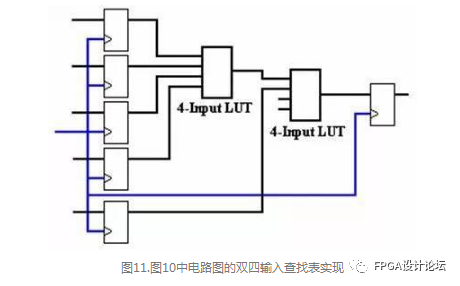

很明顯,這種實(shí)現(xiàn)方法簡(jiǎn)單多了。在Virtex-II或Spartan-3系列FPGA中,觸發(fā)器間的邏輯需要至少2個(gè)4輸入查找表,如圖11所示。

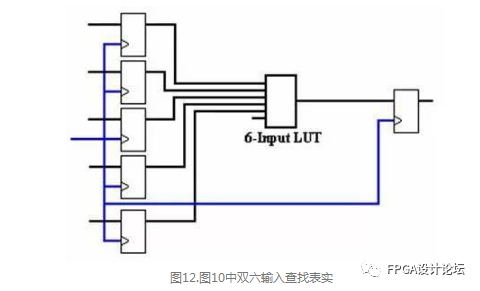

由于Virtex-5系列FPGA有著6輸入的查找表,用戶(hù)可以在一個(gè)查找表中實(shí)現(xiàn)相同數(shù)量的邏輯,如圖12所示。

本例中使用的SCTL(如圖9所示)設(shè)置在40MHZ下運(yùn)行,這意味著在任意觸發(fā)器之間邏輯電路必須在25ns內(nèi)完成執(zhí)行。電子在電路中傳播的速度決定了代碼執(zhí)行的最大速度。關(guān)鍵路線(xiàn)是有最長(zhǎng)傳播延遲的邏輯電路分支,它決定了該部分電路中理論最大時(shí)鐘速率。Virtex-5 FPGA上的雙六輸入查找表不僅減少實(shí)現(xiàn)給定邏輯電路所需要的查找表總數(shù),而且減少電子通過(guò)邏輯電路的傳播延遲(時(shí)間)。Virtex-5系列FPGA中的6輸入查找表不僅可以減少實(shí)現(xiàn)特定邏輯而需要的查找表的數(shù)量,而且可以降低邏輯中電流的傳輸延時(shí)。這意味著,您可簡(jiǎn)單地通過(guò)選擇一個(gè)基于Virtex-5的硬件指標(biāo)設(shè)置相同的SCTL,追求更快的時(shí)間速度。

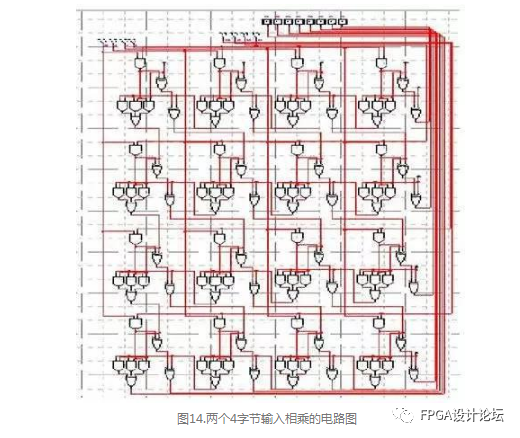

5乘法器和DSP片

看起來(lái)簡(jiǎn)單的兩數(shù)相乘運(yùn)算在數(shù)字電路中實(shí)現(xiàn)起來(lái)是十分復(fù)雜的,也是極為消耗資源的。為提供相關(guān)參考,圖14所示是一種使用組合邏輯電路實(shí)現(xiàn)4×4字節(jié)乘數(shù)器的示意圖。

試想兩個(gè)32字節(jié)的數(shù)字相乘要通過(guò)2000多步操作才能得到結(jié)果。因此,F(xiàn)PGA預(yù)設(shè)了乘數(shù)器電路,在數(shù)學(xué)和信號(hào)處理應(yīng)用中保存對(duì)查找表和觸發(fā)器使用。Virtex-II和Spartan-3 FPGA擁有18×18bit乘法器,所以?xún)蓚€(gè)32字節(jié)數(shù)字相乘的運(yùn)算需要三個(gè)乘法器來(lái)實(shí)現(xiàn)。許多信號(hào)處理算法都包括連乘運(yùn)算結(jié)果的功能,因此Virtex-5等高性能FPGA都預(yù)設(shè)被稱(chēng)為DSP片的乘數(shù)器累加電路.這些預(yù)設(shè)處理組件,也被稱(chēng)為DSP48片,包括25×18bit乘數(shù)器以及加法器電路,盡管您可單獨(dú)使用乘數(shù)器功能。表5所示為不同F(xiàn)PGA系列DSP決策。

6塊隨機(jī)存取存儲(chǔ)器

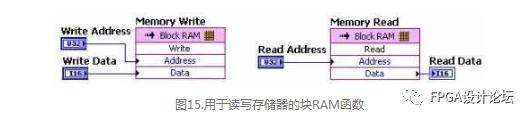

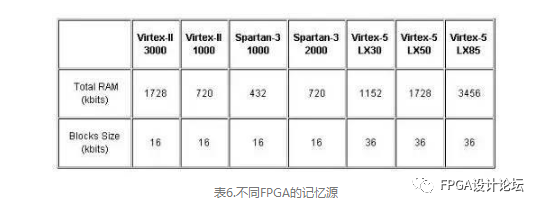

選擇FPGA時(shí),記憶源是另一個(gè)需要考慮的關(guān)鍵因素。嵌入FPGA芯片中的用戶(hù)自定義隨機(jī)存取存儲(chǔ)器(RAM),對(duì)儲(chǔ)存數(shù)據(jù)設(shè)置或平行環(huán)路之間傳送數(shù)值很有幫助。基于FPGA系列,您可在16或36kb組件中設(shè)置板載RAM,或者使用觸發(fā)器以數(shù)組來(lái)執(zhí)行數(shù)據(jù)設(shè)置;然而,對(duì)于FPGA邏輯源來(lái)說(shuō),大型數(shù)組很快就變得十分“奢侈”。由100個(gè)32字節(jié)元素?cái)?shù)組可消耗Virtex-II 1000 FPGA中超過(guò)30%的觸發(fā)器,或者占用少于1%的嵌入式塊RAM。DSP算法通常需要追蹤整個(gè)數(shù)據(jù)塊或是復(fù)雜等式的系數(shù),而在沒(méi)有板載存儲(chǔ)器情況下,許多處理功能在FPGA芯片的硬件邏輯電路中都不適用。圖16所示為使用塊RAM讀寫(xiě)存儲(chǔ)器的圖形化功能。

同樣,你也可以使用內(nèi)存塊,將一段完整周期存儲(chǔ)為數(shù)值和索引的順序表,為板載信號(hào)發(fā)生器存儲(chǔ)周期性波形數(shù)據(jù)。輸出信號(hào)的最終頻率由檢索數(shù)值的速度決定,這樣您就可用此方法動(dòng)態(tài)改變輸出頻率,而不需要輸入波形中的急劇變化。

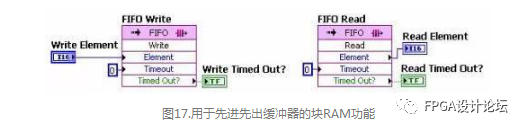

FPGA固有的并行執(zhí)行要求邏輯電路獨(dú)立元件可在不用時(shí)間脈沖下驅(qū)動(dòng)。在不同運(yùn)行速度下的邏輯電路之間傳遞數(shù)據(jù)是很棘手的。使用先進(jìn)先出(FIFO)緩沖器時(shí),板載存儲(chǔ)器可用來(lái)是傳輸更加平穩(wěn)。如圖16所示,用戶(hù)可以將FIFO緩沖器配置成不同大小以確保數(shù)據(jù)在FPGA芯片的非同步部件間不會(huì)丟失。表6所示為嵌入不同F(xiàn)PGA系列的用戶(hù)可設(shè)置快RAM。

7總結(jié)

隨著高端技術(shù)的發(fā)展以及新概念的深入概括,F(xiàn)PGA技術(shù)地采用將不斷增加。然而探究FPGA其中奧秘,感嘆這硅片中在方框圖間匯編出的變化,也是十分重要的。在發(fā)展階段,如果您懂得如何利用和優(yōu)化資源,比較和選擇觸發(fā)器、查找表、乘數(shù)器和塊RAM等硬件指標(biāo)是十分有幫助的。這些基本的功能塊并不是包含所有資源的完整清單,而且這篇白皮書(shū)并沒(méi)有包含對(duì)所有FPGA部件的討論。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1645文章

22042瀏覽量

618245 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7649瀏覽量

167339

發(fā)布評(píng)論請(qǐng)先 登錄

5CEBA4F23C8NQS現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)芯片

Microchip發(fā)布PolarFire Core FPGA和SoC產(chǎn)品

FPGA的定義和基本結(jié)構(gòu)

FPGA芯片的概念和結(jié)構(gòu)

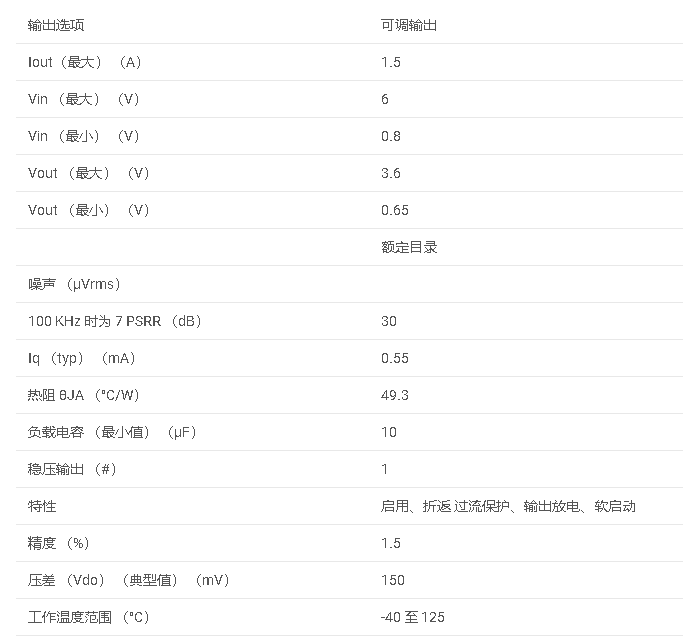

數(shù)據(jù)手冊(cè)#TPS7A74 具有可編程軟啟動(dòng)功能的 1.5A 低壓差 (LDO) 線(xiàn)性穩(wěn)壓器

fpga和cpu的區(qū)別 芯片是gpu還是CPU

MCU與FPGA的區(qū)別和聯(lián)動(dòng)

FPGA與ASIC的優(yōu)缺點(diǎn)比較

FPGA編程語(yǔ)言的入門(mén)教程

萊迪思分析不斷變化的網(wǎng)絡(luò)安全形勢(shì)下FPGA何去何從

FPGA如何消除時(shí)鐘抖動(dòng)

FPGA高速收發(fā)器的特點(diǎn)和應(yīng)用

基于FPGA的人臉識(shí)別技術(shù)

揭秘FPGA與差分晶振的神奇聯(lián)動(dòng),你的設(shè)備為何如此高效?

FPGA-現(xiàn)場(chǎng)可編程門(mén)陣列

FPGA-現(xiàn)場(chǎng)可編程門(mén)陣列

評(píng)論