芯片剪切強度試驗是評價芯片黏結可靠性的主要手段之一。芯片的高度集成小型化的發展對芯片剪切設備的施力范圍、靈敏度等能力的要求也是逐漸提高的。其中芯片剪切設備是目前最先進的芯片剪切儀,該設備擁有創立的模塊設計理念讓配置更靈活,從而使之成為單一或多功能應用都具很高性價比的推拉力測試系統,達到高精度、高重復性、高再現性。今天__【科準測控】__小編就來分享一下半導體集成電路芯片剪切強度測試目的、設備要求、技術參數、試驗方法以及失效判據,一起往下看吧!

試驗目的

本試驗的目的是確定將半導體芯片或表面安裝的無源器件安裝在管座或其他基板上所使用的材料和工藝步驟的完整性。通過測量對芯片所加力的大小、觀察在該力作用下產生的失效類型(如果出現失效)以及殘留的芯片附著材料和基板/管座金屬層的外形來判定器件是否接收。

設備要求

本試驗所需設備是一臺能施加負載的儀器,要求其準確度達到滿刻度的±5%或0.5N(取其較大者);一臺用來施加本試驗所需力的帶有杠桿臂的圓形測力計或線性運動加力儀。試驗設備應具有下述能力∶

a) 芯片接觸工具,能把力均勻地加到芯片的一條棱邊(見圖 1)。可使用合適的輔助器材(如光滑的爪狀物、線帶等),以確保芯片接觸工具能將應力均勻地施加到芯片的一條棱邊。

b) 保證芯片接觸工具與管座或基板上安放芯片的平面垂直。

c) 芯片接觸工具與管座/基板夾具具有相對旋轉能力,這有利于與芯片邊沿線接觸,即對芯片加力的工具應從一端到另一端接觸芯片的整個邊沿(見圖2)。

d) 一臺放大倍數至少為10倍的雙目顯微鏡,其照明應有利于在試驗過程中對芯片與芯片接觸工具的界面進行觀察。

科準測控推拉力測試機符合以上測試要求:

技術參數

1、測試精度:±0.25%;

2、X軸有效行程:200mm(標準機型)可按需定制

3、Y軸有效行程:160mm(標準機型)可按需定制

4、Z軸有效行程:60mm(標準機型)可按需定制

5、平臺夾具:平臺可共用各種夾具,按客戶產品訂制

6、雙搖桿控制機器四軸運動,操作簡單快捷

7、外形尺寸: L660W355H590(mm)

8、凈重:70KG

9、電源:220V 50/60HZ.≤2KW

10、氣壓:0.4-0.6Mpa

剪切強度試驗方法

采用上述設備對芯片施加力,該力應足以能把芯片從固定位置上剪切下來或等于規定的最小剪切強度(見圖4)的兩倍(取其第一個出現的值)。

注意∶對于無源元件,僅元件末端焊接區與基板焊接,因此用于確定應施加推力的大小只計算元件末端焊接區面積之和。芯片剪切力應施加在無源元件垂直于最長軸線上的方向上。粘接面積應通過測量實際可能的元件粘接區域確定。例如,典型的陶瓷片式電容器是通過其端金屬化區域粘接。粘結面積應從一個入射視角,通過測量兩端的金屬區域來決定。在進行剪切試驗之前應將此測量值乘以2得到粘結面積。電容體下的非導電性底架材料的面積,不屬測量范圍,因為此類材料通常用來對器件提供足夠的機械支撐,一般不起電連接作用。如果任何元件的底部表面存在以提高粘接強度為目的的粘接,對于本評定,此區域面積視為粘接面積。

- 當采用線性運動加力儀時,加力方向應與管座或基板平面平行,并與被試驗的芯片垂直。

b) 當采用帶有杠桿臂的圓形測力計施加試驗所需要的作用力時,它應能圍繞杠桿臂軸轉動。其運動方向與管座或基板平面平行,并與被試驗的芯片邊沿垂直。與杠桿臂相連的接觸工具應位于適當距離上,以保證外加力的準確數值。

c) 芯片接觸工具應在與固定芯片的管座或基板基座近似成90°的芯片邊沿由 ON 到規定值逐漸施加應力(見圖3)。對長方形芯片,應從與芯片長邊垂直的方向施加應力。當試驗受到封裝外形結構限制時,如果上述規定不適用,則可選擇適用的邊進行試驗。

d) 在與芯片邊沿開始接觸之后以及在加力期間,接觸工具的相對位置不得垂直移動,以保證與管座/基板或芯片附著材料一直保持接觸。如果芯片接觸工具位于芯片上面,可換用一個新的芯片或重新對準芯片,只要3.1c)的要求得到滿足。

失效判據

符合以下任一條判據的器件均應視為失效。

a) 達不到圖4中1.0倍曲線所表示的芯片強度要求。

b) 使芯片與底座脫離時施加的力小于圖4中標有1.0倍的曲線所表示的最小強度的1.25倍,同時

芯片在附著材料上的殘留小于附著區面積的50%。

c) 使芯片與底座脫離時施加的力小于圖4中標有1.0倍的曲線所表示的最小強度的2.0倍,同時芯片在附著材料上的殘留小于附著區面積的10%。

注∶對共晶焊料的芯片,殘留在芯片附著區中的不連續碎硅片應看作此種附著材料;對金屬玻璃粘接劑粘接

的芯片,在芯片上或在基座上的芯片附著材料應作為可接收的附著材料。

3.3 芯片脫離的類別

當有規定時,應記錄使芯片從底座上脫離時所加力的大小和脫離的類別。a) 芯片被剪切掉,底座上殘留有硅碎片;b) 芯片與芯片附著材料間脫離c) 芯片與芯片附著材料一起脫離底座。

說明

有關的訂購文件應規定以下內容∶

a))最小芯片粘結強度要求(若不同于圖4的規定);

b)應接受試驗的器件數和接收判據;

c)適用時數據記錄的要求(見3.3)。

本文就是小編分享的關于半導體集成電路芯片剪切強度測試原理、技術參數、試驗方法及失效判據介紹了!希望能給大家帶來幫助。科準專注于推拉力測試機研發、生產、銷售。廣泛用于與LED封裝測試、IC半導體封裝測試、TO封裝測試、IGBT功率模塊封裝測試、光電子元器件封裝測試、大尺寸PCB測試、MINI面板測試、大尺寸樣品測試、汽車領域、航天航空領域、軍工產品測試、研究機構的測試及各類院校的測試研究等應用。如果您有遇到任何有關推拉力機、半導體集成電路等問題,歡迎給我們私信或留言,科準的技術團隊也會為您免費解答!

審核編輯 黃昊宇

-

芯片

+關注

關注

459文章

52505瀏覽量

440755 -

測試機

+關注

關注

1文章

249瀏覽量

13172

發布評論請先 登錄

現代集成電路半導體器件

【展會預告】2025 中國西部半導體展重磅來襲,華秋邀您 7 月 25-27 日西安共探集成電路新未來!

越芯半導體集成電路先進測試基地一期工程喜封金頂

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

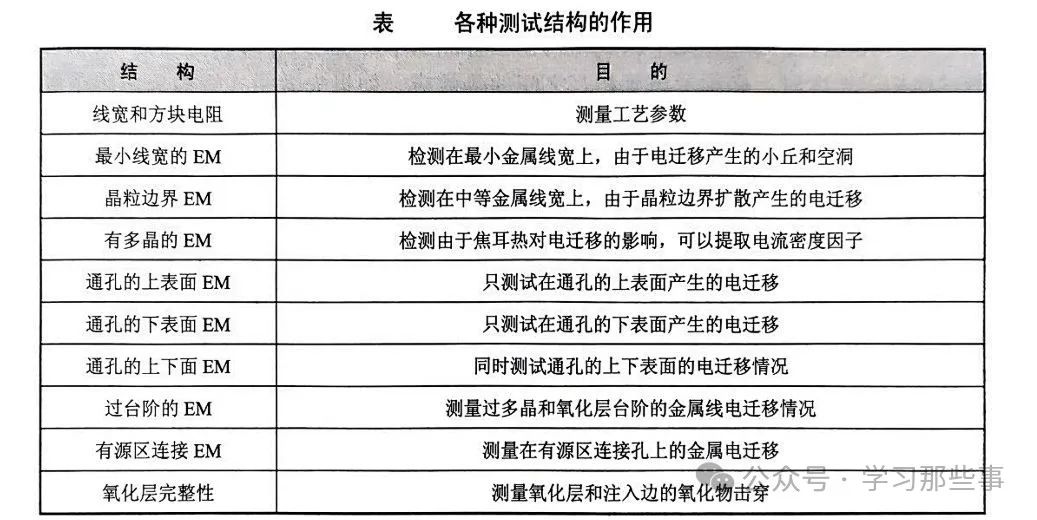

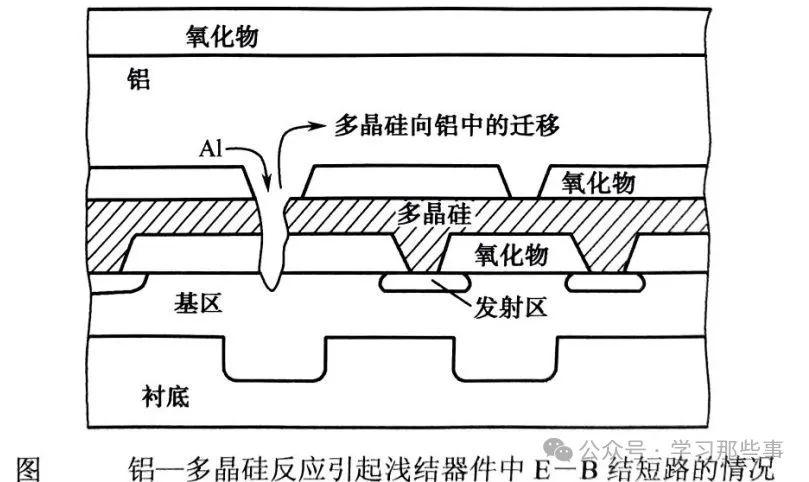

半導體集成電路的可靠性評價

芯和半導體將參加2024集成電路特色工藝與先進封裝測試產業技術論壇

單片集成電路和混合集成電路的區別

總投資約30億元 高可靠性高功率半導體器件集成電路IDM項目簽約宜興

半導體集成電路芯片剪切強度測試全面解析

半導體集成電路芯片剪切強度測試全面解析

評論