作者:Hugh Yu, Gina Kelso, and Ashraf Saad

隨著醫(yī)療超聲在醫(yī)療診斷領域的廣泛應用,醫(yī)生對超聲圖像系統(tǒng)圖像質量的要求越來越高,而提高圖像質量的關鍵技術之一是提高接收通道的信噪比。隨著系統(tǒng)中接收通道數(shù)量的增加一倍,信噪比理論上應該提高3 dB。因此,增加系統(tǒng)通道數(shù)量已成為加強信噪比的最簡單有效的方法。目前,128通道已成功成為中高級醫(yī)療超聲設備的主流配置,192通道或更多通道將成為高端系統(tǒng)的下一個趨勢。隨著通道數(shù)量的增加,模擬前端和后端數(shù)字處理以及物理連接之間的數(shù)據速率急劇增加。它們還會導致數(shù)字電路器件接口的數(shù)量、處理能力、成本、整個接收器電路的設計復雜性以及相應的功耗增加。目前,超聲系統(tǒng)使用射頻(RF)波束成形。輸出數(shù)據速率完全取決于模數(shù)轉換器(ADC)的分辨率、采樣速率和通道數(shù)。同時,模擬前端(AFE)通常使用低壓差分信號(LVDS)輸出接口。八通道AFE需要八對LVDS數(shù)據線以及一對數(shù)據時鐘和幀時鐘。對于擁有超過 128 個通道的系統(tǒng),有大量的數(shù)據和物理連接。

本文介紹了一種基于八通道AFE的數(shù)字解調器和JESD204B接口的超聲接收通道設計方案,有效解決了上述系統(tǒng)數(shù)據速率大、物理連接復雜帶來的設計難題。

系統(tǒng)架構

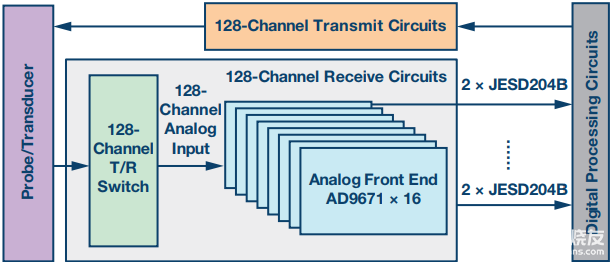

超聲系統(tǒng)由探頭(換能器)、發(fā)射電路、接收電路、后端數(shù)字處理電路、控制電路、顯示模塊等組成。圖1是帶有JESD204B接口的128通道超聲系統(tǒng)發(fā)送/接收路徑框圖。數(shù)字處理模塊通常包括現(xiàn)場可編程門陣列(FPGA),根據系統(tǒng)的當前配置和控制參數(shù)生成相應的波形。然后,發(fā)射電路的驅動器和高壓電路產生高電壓以激勵超聲換能器。超聲換能器通常由壓電陶瓷換能器(PZT)制成。它將電壓信號轉換為超聲波,進入人體,同時接收組織產生的回波。然后將回波轉換為電壓信號并傳輸?shù)桨l(fā)送/接收(T/R)開關電路。T/R開關電路的主要目的是防止高壓發(fā)射信號損壞低壓接收模擬前端。經過信號調理、增益和濾波后的模擬電壓信號被傳遞到AFE的集成ADC,然后轉換為數(shù)字數(shù)據,然后通過JESD204B接口傳輸?shù)胶蠖藬?shù)字部分進行相應的處理,最終創(chuàng)建超聲圖像。接收通道由一個128通道T/R開關電路、一個帶數(shù)字解調器和JESD204B接口的16八通道超聲AFE器件以及一個帶JESD204B接口的FPGA組成。

圖1.128通道超聲系統(tǒng)框圖。

AD9671: 八通道超聲AFE,內置數(shù)字解調器和JESD204B接口

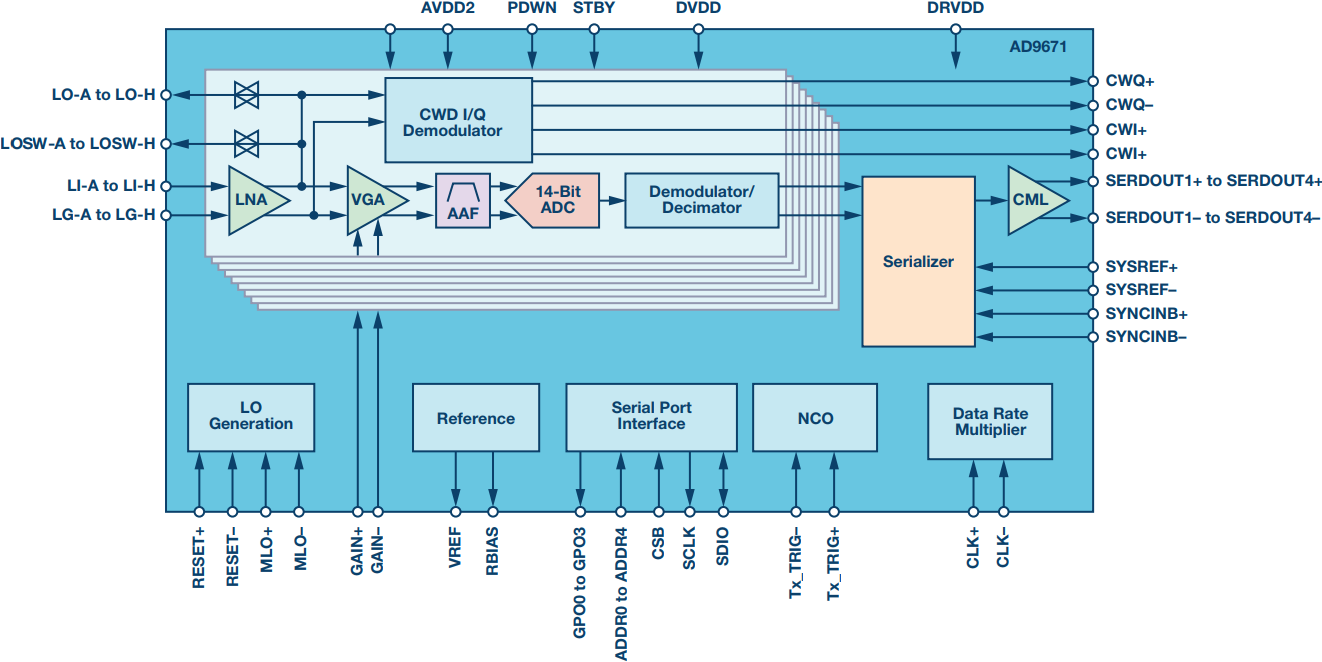

AD9671是八通道超聲AFE,內置ADI公司(ADI)的數(shù)字解調器和JESD204B接口,被選用于該超聲系統(tǒng)接收電路。它包含八個通道,包括一個帶低噪聲放大器(LNA)的可變增益放大器(VGA)、一個具有可編程相位旋轉功能的連續(xù)波(CW)諧波抑制I/Q解調器、一個抗混疊濾波器(AAF)、一個14位ADC、一個用于數(shù)據處理和帶寬降低的數(shù)字解調器和抽取器,以及JESD204B接口。圖2是AD9671的功能框圖。

圖2.AD9671功能框圖

數(shù)字解調器

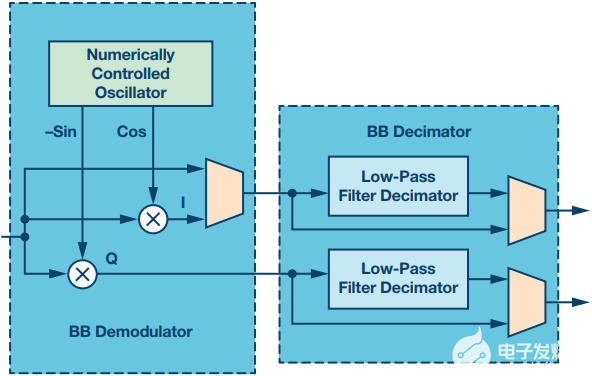

數(shù)字解調器由基帶解調器和基帶抽取器組成。解調器將RF信號下變頻為基帶正交信號。抽取器減少了多余的過采樣。圖3是數(shù)字解調器的框圖。

圖3.數(shù)字解調器框圖。

JESD204B接口

AD9671數(shù)字輸出符合JEDEC標準JESD204B,數(shù)據轉換器串行接口。AD9671支持單通道、雙通道或四通道接口。它可以連接到最大數(shù)據輸出速率為 5.0 Gbps 的 FPGA。

系統(tǒng)設計與應用

本節(jié)介紹了AD9671多通道超聲系統(tǒng)的接收電路設計,并進一步分析了使用數(shù)字解調器和JESD204B接口的優(yōu)勢。

接收電路設計

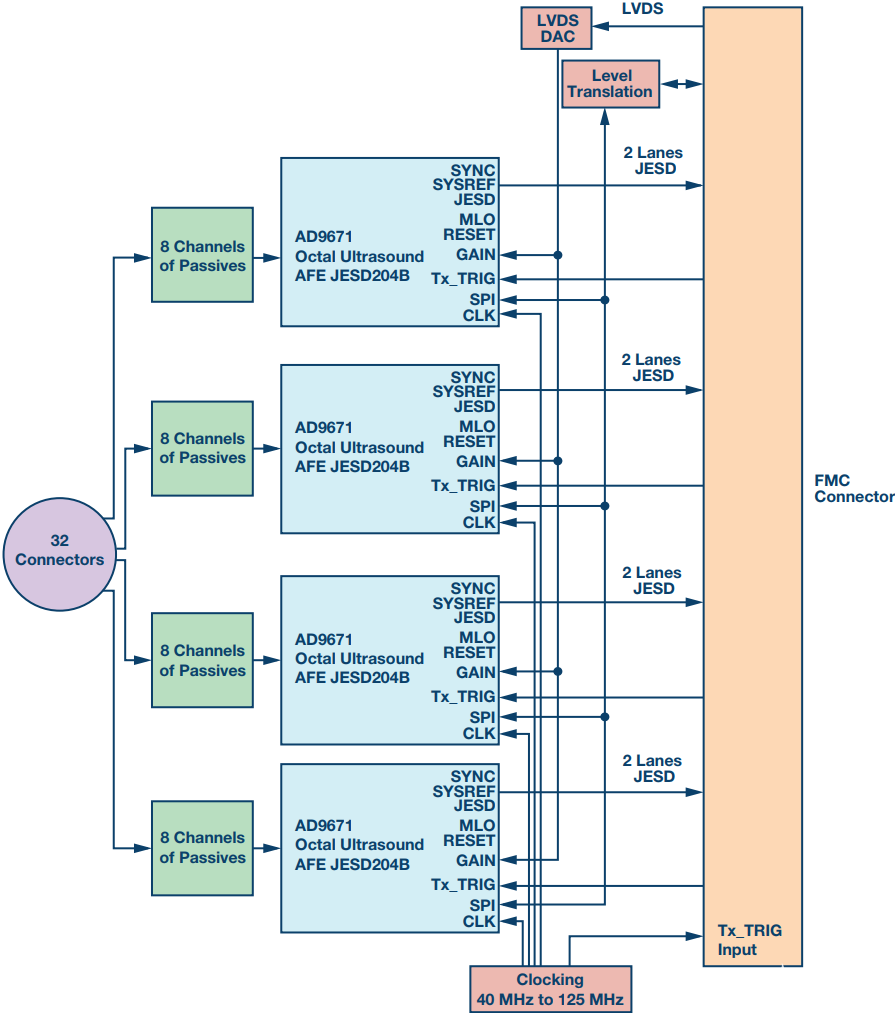

圖4所示為32通道接收電路模塊原理圖,可用于驗證基于AD9671的系統(tǒng)可行性。通過四個這樣的模塊,可以配置超聲系統(tǒng)的128通道接收電路。該模塊可用于執(zhí)行數(shù)據采集和處理,并通過專用FMC連接器連接到FPGA來實現(xiàn)超聲波信號處理和圖像生成。

圖4.接收電路的頂層原理圖。

數(shù)字解調器應用分析

對于 128 通道超聲系統(tǒng),如果使用采樣率為 40 MSPS 的 14 位 ADC,并且使用 RF 波束成形算法,則 ADC 輸出和波束成形 FPGA 之間的數(shù)據速率為 14 × 40 × 128 = 71.68 Gbps。

下面分析了使用數(shù)字解調器的好處。

RF信號的基帶解調器執(zhí)行正交解調。這可以通過將ADC輸出的數(shù)字化RF信號乘以復正弦信號

來實現(xiàn),其中fd是可以接近超聲換能器中心頻率的解調頻率,以將中心頻率下變頻至0 Hz左右。輸出信號是一個復數(shù)信號,由其I(同相)和Q(正交相位)表示。探頭的中心頻率和所有感興趣的頻段信號被降檔到大約0 Hz,用濾波器和抽取器濾除不需要的頻率分量,以保留對生成超聲圖像有用的頻段信息。

對于中心頻率為3.5 MHz的探頭換能器,經過基帶解調和抽取后,具有16位格式I和Q數(shù)據輸出,數(shù)據速率現(xiàn)在為2(I&Q)×16位×3.5 MHz×128通道= 14.336 Gbps。 與原來的71.68 Gbps相比,即使I和Q通道同時輸出,數(shù)據速率也降低了80%。

JESD204B接口應用分析

就當前多通道超聲系統(tǒng)應用中的AFE和ADC而言,LVDS已經取代了并行輸出接口。然而,對于128通道或更高的超聲系統(tǒng),ADC輸出的大量LVDS線連接仍然是設計工程師頭疼的問題。對于LVDS,當前超聲系統(tǒng)中有一個八進制AFE有10對電線。對于 128 通道超聲系統(tǒng),需要將 128/8 × 10 = 160 對 LVDS 數(shù)據和時鐘線連接到 FPGA。

下面分析了使用JESD204B接口的好處。

由于JESD204B使用16位數(shù)字輸出格式并使用8B/10B編碼,因此具有14位分辨率、40 MSPS ADC的八通道AFE的輸出數(shù)據速率為20 ×40 × 8 = 6.4 Gbps。AD9671 JESD204B接口每通道的最大數(shù)據速率為5.0 Gbps,因此只需兩對數(shù)據通道即可實現(xiàn)8通道AFE數(shù)據輸出。因此,對于 128 通道超聲系統(tǒng),與 160 對 LVDS 線相比,只需要 128/8 × 2 = 32 對輸出數(shù)據通道;消除了 80% 的物理接口路由。

結論

本文介紹了一種基于AD9671(具有數(shù)字解調器和JESD204B接口的八通道AFE)的多通道超聲系統(tǒng)設計。本文分別有效分析了在超聲系統(tǒng)中使用這種帶有數(shù)字解調器和JESD204B接口的AFE的應用優(yōu)勢和優(yōu)勢。與目前大多數(shù)RF波束成形和LVDS接口設計相比,模擬前端和數(shù)字處理部分之間的數(shù)據速率和接口路由都降低了80%。如果在分析中將這兩種方法組合在一起,物理連接將進一步減少。因此,本文介紹的系統(tǒng)設計可以通過減少數(shù)據接口布線所需的電路板面積、計算復雜性要求以及系統(tǒng)設計成本,有效地簡化電路設計和軟件處理復雜性。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

9053瀏覽量

151804 -

adc

+關注

關注

99文章

6708瀏覽量

549210 -

lvds

+關注

關注

2文章

1127瀏覽量

67476

發(fā)布評論請先 登錄

JESD204B的常見疑問解答

JESD204B的系統(tǒng)級優(yōu)勢

串行LVDS和JESD204B的對比

JESD204B串行接口時鐘的優(yōu)勢

FPGA高速數(shù)據采集設計之JESD204B接口應用場景

FPGA高速數(shù)據采集設計之JESD204B接口應用場景

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

寬帶數(shù)據轉換器應用的JESD204B與串行LVDS接口考量

JESD204B協(xié)議介紹

JESD204B的優(yōu)勢

JESD204B標準及演進歷程

AD9671:帶數(shù)字解調器的八進制超聲波AFE,JESD204B數(shù)據表

JESD204B使用說明

基于數(shù)字解調器和JESD204B接口的多通道超聲接收系統(tǒng)設計

基于數(shù)字解調器和JESD204B接口的多通道超聲接收系統(tǒng)設計

評論