Xilinx的Zynq ? UltraScale+ ? RFSoC系列器件是真正具有開創性的一類設備,它將射頻數據轉換器與信號設備中的高性能處理系統和可編程邏輯融合在一起。值得注意的是,射頻數據轉換器包括模數轉換器 (ADC) 和數模轉換器 (DAC) 以及生成和處理射頻信號所需的所有元件。因此,RF 數據轉換器提供數字上變頻器和下變頻器、混頻器和數控振蕩器。射頻片上系統 (RFSoC) 還具有軟決策、低密度奇偶校驗前向糾錯塊,支持最新的前向糾錯 (FEC) 編碼方案,有助于最大限度地提高信道容量。

這種單芯片解決方案為系統開發人員提供了多項優勢,包括緊密集成的解決方案,可顯著減小電路板的尺寸和復雜性,并降低整體功耗。Zynq UltraScale+ RFSoC 還為開發人員提供直接采樣解決方案。得益于 RF 數據轉換器中使用的 ADC 和 DAC,直接采樣成為可能。它們提供高采樣頻率(第三代設備中為 10GSPS)和寬模擬輸入帶寬(第三代設備中為 6GHz)。使用直接采樣方法消除了對提供向上或向下轉換的模擬前端的需要。這提供了顯著的系統級優勢,因為這些模擬前端不可編程或容易適應支持許可或地理限制,

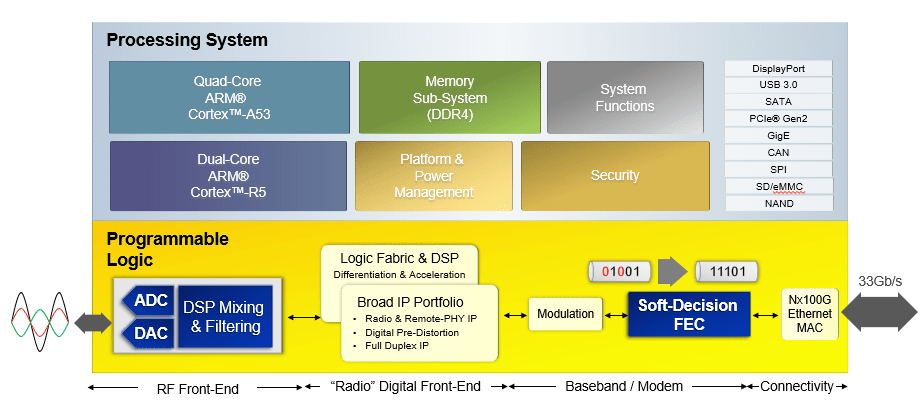

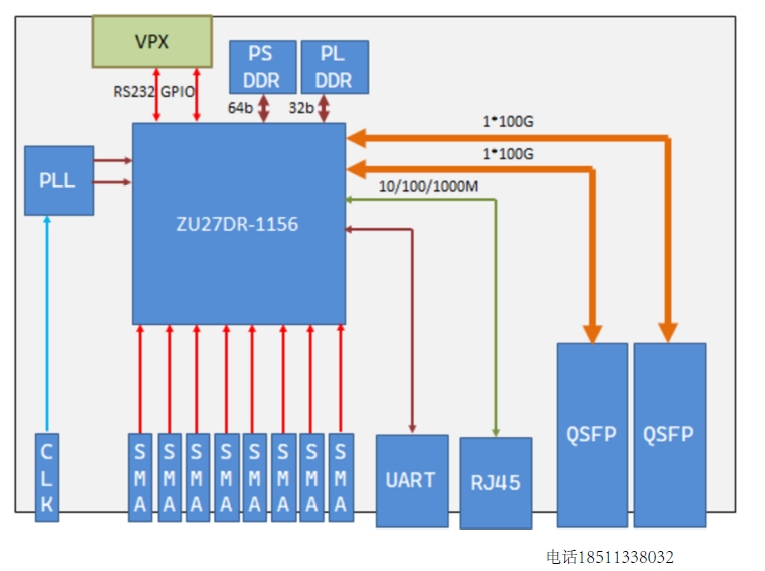

Zynq UltraScale+ RFSoC 還包含一個 64 位四核 Arm ? Cortex-A53 應用處理單元和一個 32 位雙核 Arm Cortex-R5 實時處理單元(圖 1)。

圖 1:Zynq UltraScale+ RFSoC 框圖概述了解決方案結構。(來源賽靈思)

實時控制和安全應用以及高性能應用可以在 Zynq UltraScale+ RFSoC 處理系統 (PS) 中實現。為支持接口,Zynq UltraScale+ RFSoC PS 還支持多種行業標準接口,例如 GigE、SATA、USB3、PCIe、CAN、I 2 C、SPI 等。同時,可編程邏輯與 GTY 串行器/解串器 (SERDES) 相結合,提供了支持所有通用公共無線電接口 (CPRI) 線路速率和高達 100GE 的能力。

RFSoC 解決方案的開發將努力利用可編程邏輯,以便從其并行結構提供的吞吐量、確定性和響應性中獲益。當然,使用 Zynq UltraScale+ RFSoC 實施的解決方案會很復雜。軟件無線電、雷達和測試設備就是很好的例子。純粹在寄存器傳輸級 (RTL) 開發和實施這些算法可能非常耗時,并且會影響上市時間。

實現最佳上市時間同時仍允許開發人員利用可編程邏輯的并行特性的一種方法是使用 Xilinx 的 Vitis ?統一軟件平臺。Vitis 使用戶能夠將算法從處理系統加速到可編程邏輯。當與 Xilinx 異構片上系統設備或加速卡一起使用時,由于高級綜合和 OpenCL ? ,這種加速成為可能。

使用 Vitis 和 OpenCL 加速

Vitis 使用戶能夠利用 OpenCL 框架在可編程邏輯中實現加速內核。這些加速內核是使用比傳統 RTL 更高級的語言定義的。

OpenCL 是一個行業標準框架,支持異構系統上的并行計算。OpenCL 背后的核心原則之一是無需更改代碼即可啟用跨平臺功能。這允許相同的代碼可以跨 CPU、GPU、FPGA、DSP 等移植,性能擴展取決于平臺的功能。

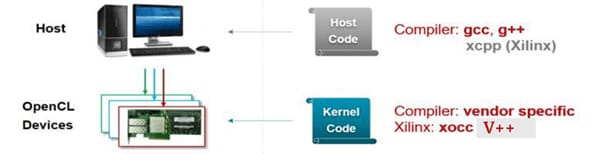

OpenCL 使用主機和內核模型(圖 2)。每個系統都有一個主機(通常是基于 x86 的)和幾個提供加速的內核,通常是基于 GPU、DSP 或 FPGA 的。為支持 OpenCL 流程,主機應用程序通常使用 C/C++ 開發并使用 OpenCL API。這些 OpenCL API 允許主機管理加載、配置和執行內核的整個應用程序生命周期。在支持跨平臺移植的同時,內核使用OpenCL C語言開發,基于C語言,但在支持跨平臺移植方面存在局限性。

該模型允許使用 GCC 或 G++ 等標準編譯器編譯主機程序,而內核編譯器是特定于供應商的。

圖 2:該圖顯示了 Open CL 結構如何使主機程序能夠使用標準編譯器,而內核使用特定于供應商的編譯器。(來源:賽靈思)

使用 Xilinx 異構片上系統設備時,Arm 應用程序處理單元是主機,而可編程邏輯實例化內核。Vitis 為開發人員提供了在針對 Xilinx 異構 SoC 或加速卡時生成、調試和分析主機和內核元素所需的一切。

Vitis 平臺

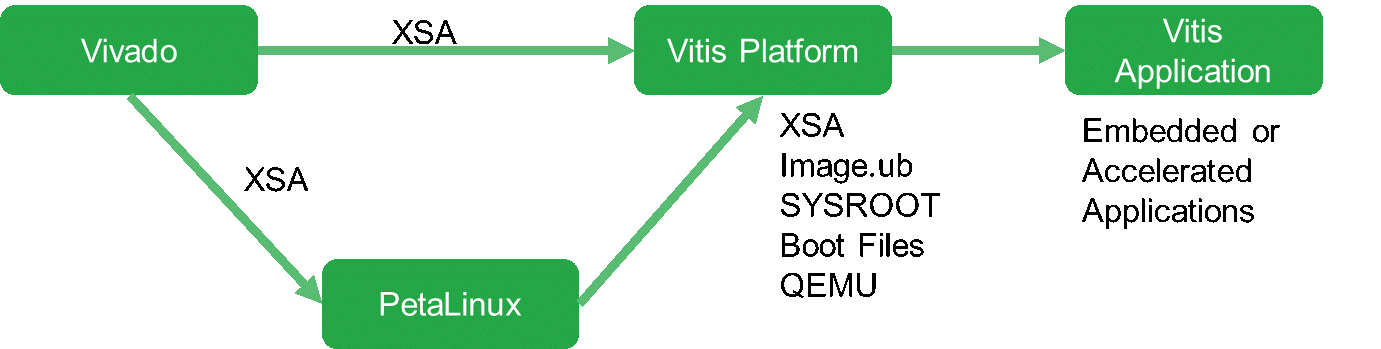

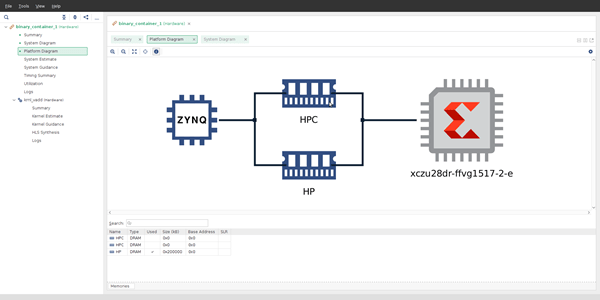

為了能夠利用 Vitis OpenCL 功能,需要一個基礎平臺。該基礎平臺定義了底層硬件的硬件和軟件配置。硬件平臺使用 Vivado ? Design Suite 創建,提供可用時鐘、高級可擴展接口處理系統/可編程邏輯 (AXI PS/PL) 接口,并中斷 Vitis 編譯器。使用這些接口,Vitis 編譯器可以將加速內核連接到處理系統內存映射中。這允許使用直接內存訪問 (DMA) 和內核控制進行高效的數據傳輸。該平臺的軟件元素由 PetaLinux 提供,并提供支持賽靈思運行時 (XRT) 的嵌入式 Linux 操作系統(圖 3)。

圖 3:該圖說明了 Vitis 平臺開發流程。(來源:作者)

當然,在 Vivado 中開發的基礎平臺也可以包含設計元素和 Vitis 可用的掛鉤。在 Zynq UltraScale+ RFSoC 的情況下,基礎設計可以包括必要的基礎設施,以使用 GTY 收發器將 RF 數據轉換器連接到外部接口或在處理器內存空間之間傳輸數據。

葡萄加速

一旦加速平臺可用,開發人員就可以開始使用 Vitis 開發他們的解決方案。使用 Vitis,他們可以實現 RF 數據轉換器和附加 IP 的控制和配置。然后,開發人員還可以使用 C/C++ 和 OpenCL C 實施所需的 RF 數據處理算法,以加速解決瓶頸并提高整體系統性能。

為了幫助開發算法,Vitis 提供了幾個開源加速就緒庫(圖 4)。這些庫包括對數學、線性代數、DSP、數據壓縮,當然還有 AI 的支持。

圖 4:Vitis 開發環境提供開源加速就緒庫來幫助設計解決方案。(來源:作者)

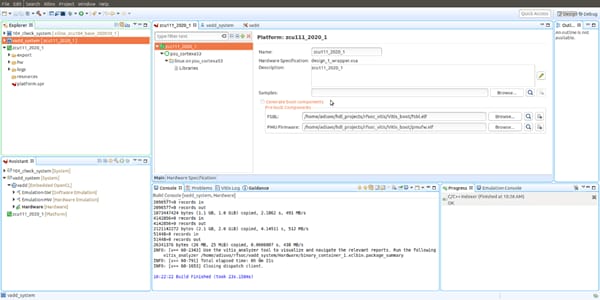

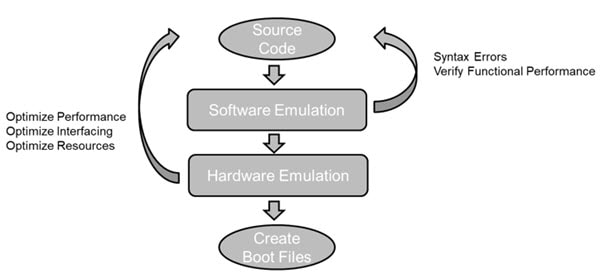

實現軟件算法后,開發人員可以使用 Vitis 提供的軟件和硬件仿真流程來優化算法,以便在生成最終引導映像之前在可編程邏輯中實現(圖 5)。

圖 5:Vitis 應用開發流程在創建最終引導映像之前使用可編程邏輯中的軟件和硬件仿真優化算法。(來源:作者)

為了利用可編程邏輯的并行特性,開發人員可能希望在內核中流水線化或展開循環、組織內存和 AXI 接口結構。這些優化是使用源代碼中的編譯指示實現的。可以使用 Vitis Analyzer 和 Vitis HLS 分析視圖來識別優化內核代碼的潛在區域(圖 6)。

圖 6: Vitis Analyzer 平臺視圖可幫助開發人員確定優化內核代碼的潛在區域。(來源:作者)

優化完成后,開發人員可以構建最終的引導文件并部署系統以進行下一階段的測試和驗證。

包起來

RFSoC 與 Vitis 的 OpenCL 功能相結合,為開發人員提供了突破性的緊密耦合解決方案。該解決方案可以通過利用高級語言、庫和框架來提供最具響應性和確定性的解決方案。這種開發方法支持采用更高級別的系統驅動方法來實施解決方案,從而縮短上市時間。

審核編輯:湯梓紅

-

ARM

+關注

關注

134文章

9306瀏覽量

374995 -

Xilinx

+關注

關注

73文章

2182瀏覽量

124340 -

RFSoC

+關注

關注

0文章

35瀏覽量

2868 -

Vitis

+關注

關注

0文章

147瀏覽量

7826

發布評論請先 登錄

瑞蘇盈科雙Andromeda XRU50 RFSoC模塊架構:構建先進實時頻譜監測解決方案

ZU+RFSoC之RFDC API介紹和使用

小型加速器中子源監測系統解決方案

是德科技亮相DesignCon 2025,展示AI創新加速解決方案

是德科技將在DesignCon 2025展示智能網絡加速解決方案

Altera推出解決方案合作伙伴加速計劃

使用AMD Vitis進行嵌入式設計開發用戶指南

AMD Vitis Unified Software Platform 2024.2發布

推薦一款極具性價比的RFSoC開發平臺

適用于數據中心應用中的硬件加速器的直流/直流轉換器解決方案

使用Vitis加速RFSoC解決方案

使用Vitis加速RFSoC解決方案

評論