作者:David Brown and Peter Delos

電子戰(zhàn) (EW) 接收器(特別是信號情報 (SIGINT) 應(yīng)用)對更高帶寬和更小尺寸、重量和功耗 (SWaP) 的需求一直存在,這促使電子戰(zhàn)系統(tǒng)設(shè)計人員不斷尋找高速模數(shù)轉(zhuǎn)換器 (ADC) 技術(shù)的新發(fā)展和改進。雖然65 nm ADC接近其固有的工藝相關(guān)性能和帶寬限制,但新的28 nm RF ADC超越了這些界限,為下一代寬帶接收器系統(tǒng)奠定了新的基礎(chǔ)。28 nm工藝節(jié)點的晶體管寬度更小,寄生效應(yīng)更低,可實現(xiàn)更快的采樣速率、更寬的模擬輸入帶寬、集成的數(shù)字功能和新的接收器架構(gòu),同時降低功耗和整體尺寸。

28 nm 模數(shù)轉(zhuǎn)換器的優(yōu)勢

隨著寬帶電子戰(zhàn)系統(tǒng)在現(xiàn)代戰(zhàn)場上變得越來越普遍,系統(tǒng)設(shè)計人員面臨著許多挑戰(zhàn),即如何實現(xiàn)下一代電子戰(zhàn)接收器所需的更高性能和更低的SWaP。高速ADC是所有寬帶電子戰(zhàn)接收器的主要設(shè)計考慮因素之一,在很大程度上決定了系統(tǒng)架構(gòu)以及整體檢測和觀察能力。高速ADC的許多性能特征,包括采樣速率、帶寬和分辨率,是決定接收器其余部分設(shè)計的因素——從模擬RF域到DSP要求。隨著電子戰(zhàn)系統(tǒng)設(shè)計人員不斷開發(fā)下一代電子戰(zhàn)接收器,對更高ADC帶寬和更高分辨率的需求仍然是永恒的行業(yè)趨勢。更高的采樣速率和帶寬允許一次數(shù)字化更多頻譜,從而緩解RF領(lǐng)域的設(shè)計挑戰(zhàn)并減少掃描時間,同時更大的位深度可提高性能并減少誤報和檢測。這種對更高采樣速率和更好分辨率的永不滿足的需求促使高速ADC制造商轉(zhuǎn)向越來越小的晶體管光刻節(jié)點(目前為28 nm和16 nm),以便在不增加器件功耗的情況下實現(xiàn)這些要求。

28 nm ADC的基本優(yōu)勢是實現(xiàn)下一代寬帶電子戰(zhàn)接收器不可或缺的一部分,并為構(gòu)建未來系統(tǒng)奠定了新的基礎(chǔ)。28 nm晶體管降低了寄生柵極電容,由于驅(qū)動開關(guān)所需的能量較低,因此可實現(xiàn)更快的開關(guān)。正因為如此,以及28 nm工藝的物理晶體管尺寸更小,ADC不僅可以實現(xiàn)更快的采樣速率,而且每平方毫米可以容納更多數(shù)量的晶體管,從而有可能實現(xiàn)更大的數(shù)字處理能力。考慮到固有的低功耗,采用28 nm工藝的ADC是下一代電子戰(zhàn)系統(tǒng)中的關(guān)鍵推動因素,其性能和能力要求以前在≥65 nm工藝上被認為是不切實際的。對于大多數(shù)電子戰(zhàn)系統(tǒng)設(shè)計人員來說,28 nm ADC可實現(xiàn)更高的采樣速率(幾GSPS及以上),這是最具吸引力的ADC特性之一,特別是對于SIGINT、電子保護(EP)和電子支持(ES)應(yīng)用。與ADC帶寬同樣重要的是分辨率,它允許更高的SNR/SFDR以及隨后檢測、觀察和處理目標信號的能力。低于 1 的欠采樣圣由于更高的模擬輸入帶寬,奈奎斯特也是可能的。

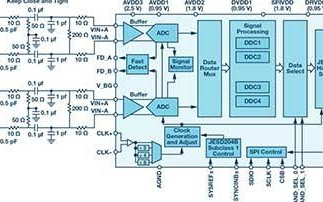

轉(zhuǎn)向28 nm工藝還允許混合信號半導(dǎo)體制造商將越來越多的數(shù)字信號處理和功能集成到其高速ADC中,而無需增加(甚至減少)系統(tǒng)SWaP。集成 NCO(數(shù)控振蕩器)和 DDC(數(shù)字下變頻器)等數(shù)字特性突破了轉(zhuǎn)換器性能極限,緩解了與更高轉(zhuǎn)換器數(shù)據(jù)速率和高數(shù)字接口功耗相關(guān)的系統(tǒng)設(shè)計挑戰(zhàn)。利用更小的28 nm工藝和提高ADC的片內(nèi)DSP功能,還可以減輕處理器的大部分處理負載和功耗,使電子戰(zhàn)系統(tǒng)設(shè)計人員能夠降低系統(tǒng)SWaP。

雖然更快的28 nm ADC可以捕獲和觀察更大的RF頻譜,但與ADC奈奎斯特帶寬相比,目標信號的帶寬可能仍然相對較小。此外,GSPS ADC的大量數(shù)據(jù)吞吐量可能導(dǎo)致尋找合適的處理器并將其與ADC物理接口的挑戰(zhàn)。目前市場上的許多28 nm轉(zhuǎn)換器在10 Gbps以上的通道速率下使用JESD204B接口標準,這可能會帶來與路由Gbps SERDES(串行器/解串器)JESD通道相關(guān)的電路板布局和信號完整性挑戰(zhàn)。幸運的是,通過集成NCO/DDC和片上DSP,ADC可以將目標信號轉(zhuǎn)換為較低的頻率或基帶,應(yīng)用數(shù)字濾波,并抽取數(shù)字數(shù)據(jù)輸出速率,以便對捕獲頻譜的部分執(zhí)行更密集的處理。可調(diào)諧NCO允許DDC掃描數(shù)字化頻譜,以便仍然可以分析整個頻譜,但具有處理增益和較低數(shù)字數(shù)據(jù)輸出速率的額外好處。并行添加多個 NCO 和 DDC 允許用戶在 DDC 之間預(yù)配置并快速切換和快速跳躍,從而進一步縮短掃描時間,因為從等式中刪除了 NCO 調(diào)諧。集成的DDC還可以顯著節(jié)省數(shù)字JESD204B接口的功耗。以如此高的速率運行的JESD SERDES可能會增加一瓦特或更多的系統(tǒng)功耗,因此將數(shù)據(jù)速率降低到較低的速度在這方面非常有益。隨著高速ADC不斷向更高的采樣速率、位深度和帶寬邁進,集成DDC和ADC對寬帶電子戰(zhàn)接收器系統(tǒng)設(shè)計人員更具吸引力,因為低SWaP處理器可能難以處理來自ADC的大量數(shù)字數(shù)據(jù)。有關(guān)DDC的更多信息和一些實際示例,請參閱Jonathan Harris的“數(shù)字下變頻器怎么了”第1部分和第2部分。

實現(xiàn)新的接收器架構(gòu)

外差接收器架構(gòu)已廣為人知,并已經(jīng)過多年的驗證。從歷史上看,許多微波接收器都采用雙下變頻架構(gòu)實現(xiàn)。對于前幾代ADC而言,工作頻段頻率與ADC輸入頻率的較大比率使得使用單個下變頻接收器架構(gòu)無法進行鏡像濾波。采樣速率和模擬輸入帶寬均增加的新型ADC現(xiàn)在使高性能寬帶單下變頻架構(gòu)變得實用且易于實現(xiàn)。

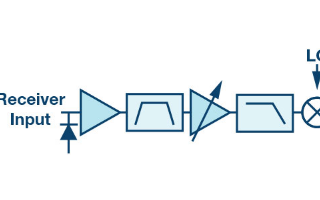

單個下變頻接收器架構(gòu)示例如圖1所示。選擇前端LNA是為了提高噪聲系數(shù)性能。如果需要,在LNA前面添加一個限幅器,以提高前端的生存功率能力。工作帶濾波器用于衰減帶外干擾。接下來,可以根據(jù)需要添加額外的增益和/或增益控制。在混頻器之前,低通濾波器可以減少RF諧波,這些諧波會增加混頻雜散輸出。混頻器是一個關(guān)鍵的構(gòu)建模塊,選擇混頻器是為了優(yōu)化目標頻帶的性能。混頻器之后的另一個低通濾波器在放大前對上邊帶進行濾波。根據(jù)需要增加額外的中頻增益。抗混疊濾波器通常是ADC之前的最后一個元件,可抑制采樣過程中可能折疊在帶內(nèi)的任何頻率。ADC是下一個,雖然它是鏈中的最后一個,但通常是第一個選擇的組件,而接收器的其余部分則圍繞ADC構(gòu)建。

圖1.單下變頻接收器架構(gòu)示例。

接下來,我們將回顧選擇頻率計劃選項時的一些注意事項。頻率規(guī)劃是選擇頻率轉(zhuǎn)換方法的過程,當使用可用組件實施時,通過合理的濾波器設(shè)計產(chǎn)生最低的雜散性能。當RF工程師第一次做出這個決定時,次優(yōu)頻率計劃有許多選擇和影響,可能會使這成為一項艱巨的任務(wù)。幸運的是,CAD工具和可用組件的現(xiàn)代進步使頻率規(guī)劃成為一項更易于管理的任務(wù)。

一般來說,較高的IF頻率在2德·或 3RD從雜散角度來看,ADC奈奎斯特區(qū)是首選。我們將首先展示將 10 GHz 工作頻段轉(zhuǎn)換為 1 的頻率計劃來概述其優(yōu)勢圣3 GHz ADC的奈奎斯特,然后顯示工作在2 GHz ADC中時的優(yōu)勢德·奈奎斯特區(qū)。

圖 2 顯示了 1 GHz 工作頻段在 10 GHz 下到 1 的頻率轉(zhuǎn)換圣3 GSPS ADC 的奈奎斯特區(qū)。說明了兩個主要問題。首先,RF鏡像頻率與工作頻段的距離非常近,需要一個非常困難的濾波器來進行鏡像抑制。其次,從IF放大級創(chuàng)建的任何IF都是帶內(nèi),無法被抗混疊濾波器濾波。

圖2.頻率規(guī)劃有問題:中頻諧波在中頻頻帶內(nèi),這使得鏡像濾波變得困難。

圖3顯示了在2德·奈奎斯特區(qū)。較高的IF頻率導(dǎo)致鏡像頻率遠離工作頻段,RF鏡像濾波器明顯更容易實現(xiàn)。此外,中頻放大器中產(chǎn)生的任何諧波都可以通過抗混疊濾波器濾除,并且將產(chǎn)生的唯一中頻諧波是ADC本身內(nèi)部的諧波。

圖3.改進的頻率規(guī)劃:IF諧波在IF頻段之外,這意味著可以實現(xiàn)鏡像濾波。

使用是德科技 Genesys 工具進行雜散分析可以快速得出相同的結(jié)論。圖4來自WhatIF頻率規(guī)劃工具。圖4顯示了WhatIF頻率規(guī)劃工具,該工具設(shè)置為10 GHz工作頻段、1 GHz瞬時帶寬、高端LO選擇以及搜索高達五階雜散。無支線區(qū)以綠色表示,在本例中,落在 2德·3 GSPS ADC 的奈奎斯特區(qū)。

圖4.使用是德科技 Genesys WhatIF 頻率規(guī)劃工具進行雜散分析。

組件啟用程序

作為任何頻率規(guī)劃分析的后續(xù)工作,應(yīng)在接收器的預(yù)期工作條件下評估混頻器和ADC,以驗證雜散和噪聲性能。

最近發(fā)布的高性能3 GHz至20 GHz混頻器包括LTC5552和LTC5553。圖 5 顯示了這些器件的主要特性。這些是同類最佳的高線性度寬帶混頻器,可直接裝入寬帶接收器架構(gòu)。主要區(qū)別在于 LTC5552 具有一個差分 IF 輸出,而 LTC5553 在所有端口上均為單端。差分IF輸出允許整個IF鏈保持差分,從而消除了通常添加到ADC輸入的巴倫。差分中頻放大器可通過實現(xiàn)完全差分中頻部分而輕松獲得,唯一的設(shè)計調(diào)整是在中頻信號鏈中引入差分濾波器。

圖5.寬帶、高性能、高線性度混頻器。

最近發(fā)布的28 nm ADC是AD9208,這是一款14位、3 GSPS雙通道ADC,具有本文前面提到的許多特性集和特性。高輸入帶寬和采樣分辨率以及四個集成DDC和NCO等數(shù)字特性使AD9208非常適合許多電子戰(zhàn)接收器系統(tǒng)和應(yīng)用。此外,9 GHz的高模擬輸入帶寬允許AD9208直接采樣至2德·和 3RD奈奎斯特頻率。甚至 4千奈奎斯特采樣可通過干凈的低抖動參考時鐘實現(xiàn),以最大限度地減少較高輸入頻率下的SNR下降。

RF接收器設(shè)計人員面臨的一個持續(xù)挑戰(zhàn)是,每個關(guān)鍵的ADC指標都會隨著輸入頻率而降低。對于噪聲和無雜散動態(tài)范圍都是如此。除了硅的限制之外,還需要仔細的封裝設(shè)計,以適應(yīng)從硅到封裝層壓板以及從封裝到PWB的RF發(fā)射,以保持GHz轉(zhuǎn)換器的輸入帶寬。

設(shè)計良好的RF I/O結(jié)構(gòu)會隨著輸入頻率的降低而逐漸下降。在設(shè)計中不考慮這些因素,通常會有一個輸入頻率,性能會急劇下降。圖 7 從概念上對此進行了說明。在為應(yīng)用篩選轉(zhuǎn)換器時,在提交設(shè)計之前需要花費大量精力來驗證性能。對于工作在GHz頻率下的RF采樣ADC,這一點變得越來越重要,在為應(yīng)用選擇ADC之前,應(yīng)充分了解性能響應(yīng)與頻率的關(guān)系。

結(jié)論

本文回顧了幾種寬帶應(yīng)用和接收器設(shè)計考慮因素。電子戰(zhàn)應(yīng)用尤其具有挑戰(zhàn)性,因為接收器具有寬工作頻段和盡可能多的瞬時帶寬。這些挑戰(zhàn)表明,對于單下變頻接收器架構(gòu),在較高的ADC奈奎斯特區(qū)工作將產(chǎn)生更好的雜散性能。該目標對ADC的輸入帶寬和混頻級的性能參數(shù)提出了挑戰(zhàn)。幸運的是,使能組件,包括具有擴展輸入頻率范圍的高速28 nm ADC和寬帶高線性度混頻器,現(xiàn)在可用于為下一代接收器奠定基礎(chǔ)。圖 6 顯示了一個完整的保護解決方案。

圖6.AD9208: 28 nm 3 GSPS、高性能、寬輸入帶寬ADC。

圖7.模擬性能:SNR、SFDR和信號功率都會隨輸入頻率而降低。針對中頻采樣的設(shè)計需要驗證所選ADC不會隨著所需輸入頻率而顯著降低。此外,在PWB設(shè)計中實現(xiàn)時,需要謹慎的RF布局技術(shù)。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9053瀏覽量

151800 -

接收器

+關(guān)注

關(guān)注

15文章

2571瀏覽量

73931 -

adc

+關(guān)注

關(guān)注

99文章

6708瀏覽量

549207

發(fā)布評論請先 登錄

EV10AS940單芯片通道模數(shù)轉(zhuǎn)換器有哪些應(yīng)用場景?

LTM9003CV-AA#PBF模數(shù)轉(zhuǎn)換器

AD9689BBPZ-2000模數(shù)轉(zhuǎn)換器現(xiàn)貨

AD9689BBPZ-2600模數(shù)轉(zhuǎn)換器現(xiàn)貨

AD9689BBPZ-2600模數(shù)轉(zhuǎn)換器銷售

AD9689BBPZ-2000模數(shù)轉(zhuǎn)換器銷售

AD9689BBPZ-2000模數(shù)轉(zhuǎn)換器

AD9208BBPZRL-3000模數(shù)轉(zhuǎn)換器

5962-9581501HXA高端AD模數(shù)轉(zhuǎn)換器

AD7878SQ高端AD模數(shù)轉(zhuǎn)換器IC 訂貨***

AD574ASE/883B高端AD模數(shù)轉(zhuǎn)換器IC

模數(shù)轉(zhuǎn)換器ADC簡介

下一代電子戰(zhàn)接收器系統(tǒng)可由28納米模數(shù)轉(zhuǎn)換器支持

利用ADI RF轉(zhuǎn)換器打造一個帶DPD接收機的直接RF發(fā)射機

28nm模數(shù)轉(zhuǎn)換器支持下一代電子戰(zhàn)接收器系統(tǒng)

28nm模數(shù)轉(zhuǎn)換器支持下一代電子戰(zhàn)接收器系統(tǒng)

評論