本文介紹了在低功耗系統(tǒng)中降低功耗同時(shí)保持測(cè)量和監(jiān)控應(yīng)用所需的精度的時(shí)序因素和解決方案。它解釋了當(dāng)所選ADC是逐次逼近寄存器(SAR)ADC時(shí)影響時(shí)序的因素。對(duì)于Σ-Δ(∑-Δ)架構(gòu),時(shí)序考慮因素有所不同(請(qǐng)參閱本系列文章的第1部分)。本文探討了模擬前端時(shí)序、ADC時(shí)序和數(shù)字接口時(shí)序中的信號(hào)鏈考慮因素。

模擬前端時(shí)序注意事項(xiàng)

圖1中的這三個(gè)模塊可以從模擬前端(AFE)開(kāi)始獨(dú)立查看。信號(hào)鏈的類(lèi)型會(huì)改變AFE,但有一些常見(jiàn)的方面可以適用于大多數(shù)電路。

圖1.多路復(fù)用SAR ADC的AFE時(shí)序考慮因素

圖2顯示了構(gòu)成AFE的AD4696 SAR ADC、外部放大器和低通濾波器。AD4696是一款16位、1 MSPS多路復(fù)用SAR ADC,具有輕松驅(qū)動(dòng)?功能。雖然需要外部放大器和電路與外部傳感器連接,但 Easy Drive 模擬輸入高阻模式和參考輸入高阻模式等功能降低了模擬輸入和參考驅(qū)動(dòng)要求。在高功率應(yīng)用中,SAR ADC的抗混疊濾波器設(shè)計(jì)需要具有侵略性,但對(duì)于低帶寬信號(hào)采樣(典型的低功耗應(yīng)用),濾波器設(shè)計(jì)要求較低。Σ-Δ架構(gòu)的好處是,我們可以依靠數(shù)字濾波器來(lái)確定頻率響應(yīng),并使用外部抗混疊濾波器在調(diào)制器頻率下進(jìn)行濾波。在沒(méi)有過(guò)采樣和固有濾波特性的情況下,需要一個(gè)外部模擬低通濾波器,以防止采樣速率以上存在的任何高頻信號(hào)混疊到通帶中。低通濾波器還用于降低來(lái)自模擬前端電路的寬帶噪聲,減少模擬輸入端發(fā)生的非線(xiàn)性電壓反沖,并保護(hù)模擬輸入免受過(guò)壓事件的影響。同樣的原則也適用于時(shí)間考慮。請(qǐng)參閱文章“低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素是什么?第 1 部分。

SAR ADC在采樣時(shí)集成了采樣保持機(jī)制,該機(jī)制是一個(gè)開(kāi)關(guān)和一個(gè)電容,用于捕獲輸入信號(hào),直到收集到轉(zhuǎn)換。

圖2.AD4696 SAR ADC,內(nèi)置外部反沖RC濾波器和驅(qū)動(dòng)器放大器。

放大器級(jí)的設(shè)計(jì)是一個(gè)兩步過(guò)程。第一步是選擇信號(hào)調(diào)理放大器和外部抗混疊級(jí),類(lèi)似于本系列文章第1部分中討論的內(nèi)容。下一步是選擇一個(gè)外部驅(qū)動(dòng)放大器(其帶寬由增益決定;請(qǐng)記住,存在功率與帶寬的權(quán)衡),該放大器將緩沖信號(hào)調(diào)理抗混疊濾波器輸出并驅(qū)動(dòng)ADC輸入。下一步是設(shè)計(jì)采用總電容C的反沖濾波器內(nèi)線(xiàn)+ C代數(shù)轉(zhuǎn)換器作為我們?yōu)V波器的總電容。

多路復(fù)用SAR ADC在模擬輸入通道之間切換時(shí)存在反沖問(wèn)題。每次閉合開(kāi)關(guān)時(shí),電容內(nèi)部電壓(C代數(shù)轉(zhuǎn)換器) 可能與先前存儲(chǔ)在采樣電容器上的電壓不同 (C內(nèi)線(xiàn)).當(dāng)這些開(kāi)關(guān)由于差異而閉合時(shí),會(huì)發(fā)生電壓毛刺。能量將在它們之間共享,電容器端子之間測(cè)量的電壓將減半。該 C內(nèi)線(xiàn)和 C代數(shù)轉(zhuǎn)換器值會(huì)影響濾波器設(shè)計(jì),在設(shè)計(jì)電路時(shí)需要考慮這些值。AD4696數(shù)據(jù)手冊(cè)詳細(xì)介紹了反沖和ADC驅(qū)動(dòng)器的選擇。此外,還提供ADC驅(qū)動(dòng)器工具以及有用的培訓(xùn)視頻。

圖3.高阻模式對(duì)反沖的影響。

AD4696內(nèi)置模擬輸入高阻態(tài)模式。這顯著降低了電壓反沖幅度,如圖3所示。模擬輸入高阻態(tài)模式還降低了前端放大器和AD4696模擬輸入之間的串聯(lián)電阻引起的性能下降,與傳統(tǒng)的多路復(fù)用SAR ADC相比,允許外部RC濾波器中的電阻更大。使用較大的 R內(nèi)線(xiàn)使用較小的 C內(nèi)線(xiàn)減輕了放大器穩(wěn)定性問(wèn)題,而不會(huì)顯著影響失真性能,盡管C內(nèi)線(xiàn)如果使能內(nèi)部過(guò)壓保護(hù)箝位以避免穩(wěn)定性問(wèn)題,則建議最小值為 500 pF。圖3顯示,我們可以更快地對(duì)所需信號(hào)進(jìn)行采樣,從而加快系統(tǒng)時(shí)序。

ADC 時(shí)序考慮因素

選擇的ADC將取決于系統(tǒng)中的重要內(nèi)容。有許多文章觸及了在性能方面更適合的主題,并比較了 SAR 和 Σ-deltas 技術(shù)。在低功耗領(lǐng)域,SAR和Σ-Δ測(cè)量相似信號(hào)之間存在大量重疊。有一點(diǎn)很清楚,SAR時(shí)間更易于理解。

圖4.AFE SAR 時(shí)間考慮因素。

SAR ADC在某個(gè)時(shí)間點(diǎn)對(duì)輸入進(jìn)行采樣,由采集階段和轉(zhuǎn)換階段組成。在采集階段,采樣保持網(wǎng)絡(luò)或內(nèi)部電容網(wǎng)絡(luò)正在充電(圖 2)。在轉(zhuǎn)換階段,電容陣列切換到比較器網(wǎng)絡(luò),并修改DAC上的權(quán)重,直到達(dá)到與模擬輸入對(duì)應(yīng)的代碼。

圖5.典型的SAR ADC時(shí)序。

數(shù)據(jù)手冊(cè)中規(guī)定了最大轉(zhuǎn)換時(shí)間,AD4696的最大轉(zhuǎn)換時(shí)間為415 ns。采集信號(hào)的最短轉(zhuǎn)換時(shí)間為1715 ns,這是AD4696在500 kSPS下工作的采集時(shí)間。轉(zhuǎn)換之間的時(shí)間是吞吐率。

就時(shí)序而言,與SAR ADC相關(guān)的主要權(quán)衡是功耗與ADC采樣速率的關(guān)系。SAR ADC的優(yōu)點(diǎn)是采樣速率和電源電流之間存在直接線(xiàn)性關(guān)系,這意味著它可以根據(jù)目標(biāo)信號(hào)的帶寬進(jìn)行擴(kuò)展。內(nèi)部ADC內(nèi)核在兩次轉(zhuǎn)換之間關(guān)斷,因此在較低采樣速率(例如10 kSPS)下工作時(shí),AD4696的典型功耗為0.17 mW,而1 MSPS時(shí)功耗為8 mW,因此該器件適合采樣速率較低的電池供電應(yīng)用。

圖6.VDD電流與采樣率。

圖 6 顯示了 VDD當(dāng)前。如果我們將AD4696的采樣速率降低到低于100 kSPS的范圍內(nèi),而不是在500 kSPS范圍內(nèi)工作,則我們的DD電流從近 2.5 mA 降至 0.5 mA。如果我們將電流進(jìn)一步降低到10 kSPS,我們的典型IDD電流將降低到42 μA。電流的增加速率是線(xiàn)性的。所有數(shù)字和模擬電源電流均以類(lèi)似的線(xiàn)性方式縮放,這使得SAR ADC成為使用同一器件測(cè)量DC-AC信號(hào)的有吸引力的提議。

數(shù)字接口時(shí)序注意事項(xiàng)

AD4696有幾個(gè)傳統(tǒng)上與SAR ADC相關(guān)的特性,可以幫助低功耗信號(hào)鏈設(shè)計(jì)人員實(shí)現(xiàn)額外的節(jié)能,但具有時(shí)序影響。

圖7.SAR 數(shù)字接口時(shí)序注意事項(xiàng)。

與Σ-Δ架構(gòu)相比,SAR ADC的吞吐速率更容易 計(jì)算為過(guò)濾器延遲不需要考慮:

CHs = 啟用的通道數(shù)。

周期時(shí)間是CNV上升沿轉(zhuǎn)換之間的時(shí)間,由采集和轉(zhuǎn)換階段的組合組成,但可能存在重疊。ADC可以在轉(zhuǎn)換階段仍在進(jìn)行時(shí)開(kāi)始采集信號(hào)。SAR ADC上的采樣間隔時(shí)間可以描述為周期時(shí)間t中青或采樣率時(shí)間 t鍶.

t轉(zhuǎn)換= 轉(zhuǎn)換時(shí)間 tACQ= 采集時(shí)間

t中青= t鍶= 采樣頻率的倒數(shù),采樣間隔時(shí)間

轉(zhuǎn)換發(fā)生的采樣時(shí)刻由CNV信號(hào)上升沿控制。在大多數(shù)模式下,這是由外部信號(hào)提供的。AD4696還具有片內(nèi)自動(dòng)循環(huán)模式,可在內(nèi)部生成轉(zhuǎn)換開(kāi)始信號(hào)。此信號(hào)啟動(dòng)轉(zhuǎn)換。AD4696提供多種時(shí)序控制器模式,允許用戶(hù)以預(yù)定義的方式選擇轉(zhuǎn)換的順序和配置,或者在不中斷轉(zhuǎn)換的情況下即時(shí)控制序列中的下一個(gè)通道。

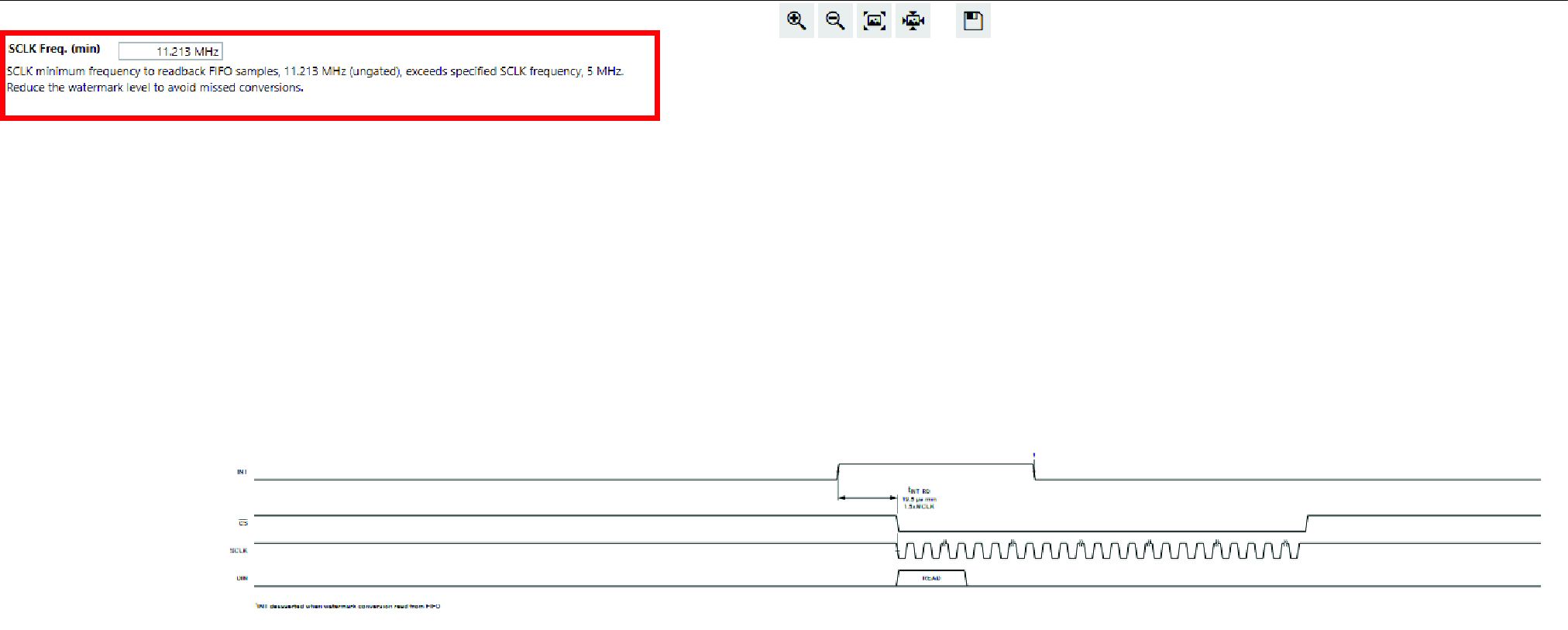

數(shù)字主機(jī)必須在下一次轉(zhuǎn)換開(kāi)始之前讀回?cái)?shù)據(jù)。因此,對(duì)于高速信號(hào),SCK頻率必須足夠快,以便在下一個(gè)CNV上升沿之前從AD4696 SPI讀回?cái)?shù)據(jù)(或在自動(dòng)循環(huán)模式下進(jìn)行內(nèi)部轉(zhuǎn)換啟動(dòng)信號(hào))。更快的采樣率需要更快的SCK頻率,因?yàn)檗D(zhuǎn)換之間的時(shí)間更短。

所需的最小SCK頻率是采樣速率、SPI幀長(zhǎng)度(以位為單位)和所用串行數(shù)據(jù)輸出模式的函數(shù)。給定樣本的轉(zhuǎn)換結(jié)果在下一個(gè)轉(zhuǎn)換階段開(kāi)始之前可用。因此,SCK頻率必須足夠快,以便在下一個(gè)CNV上升沿(或啟用自動(dòng)循環(huán)模式時(shí)的內(nèi)部轉(zhuǎn)換啟動(dòng)信號(hào))之前從AD4696 SPI讀取數(shù)據(jù)。

多個(gè)SDO數(shù)字輸出

AD4696系列還包括雙通道SDO和四通道SDO模式。在這些模式下,ADC結(jié)果在SDO和額外的GPIO引腳上并聯(lián)。這些模式通過(guò)將每個(gè)SCK周期SPI上輸出的位數(shù)增加一倍或四倍,顯著降低給定采樣速率所需的SCK頻率。這降低了對(duì)微控制器的要求,當(dāng)以1 MSPS進(jìn)行轉(zhuǎn)換時(shí),將所需的時(shí)鐘從32 MHz SPI時(shí)鐘降低到16 MHz SPI時(shí)鐘。

每個(gè)轉(zhuǎn)換模式幀所需的 SCK 周期數(shù) (NSCK) 是每幀位數(shù) (N ) 的函數(shù)位) 和串行數(shù)據(jù)輸出的數(shù)量 (N性別歧視條例):

其中 N性別歧視條例單 SDO 模式為 1,雙 SDO 模式為 2,四 SDO 模式為 4。

轉(zhuǎn)換模式 SPI 幀的開(kāi)始不得發(fā)生在 t 之前轉(zhuǎn)換時(shí)間已過(guò),必須盡早完成以遵守最低要求南科華網(wǎng)規(guī)范。在轉(zhuǎn)換模式下完成SPI幀的時(shí)間量(t框架) 的計(jì)算方法如下:

t框架= t中青– 噸CONVERT_max– 噸南科華網(wǎng)

其中 t中青是采樣周期,tCONVERT_max是最大值,t轉(zhuǎn)換是規(guī)范,并且南科華網(wǎng)是 SCK 至 CNV 上升沿延遲規(guī)范。

該 fSCK是 T 的函數(shù)框架和 NSCK.

AD4696數(shù)據(jù)手冊(cè)附表,其中給出了最小SCLK頻率與幾種采樣速率的關(guān)系示例。

自動(dòng)循環(huán)模式

傳統(tǒng)上,對(duì)于電壓或電流電平監(jiān)控應(yīng)用,SAR ADC需要主機(jī)控制器連續(xù)發(fā)出轉(zhuǎn)換信號(hào)以進(jìn)行轉(zhuǎn)換。系統(tǒng)需要檢查數(shù)據(jù)的閾值,并根據(jù)這些級(jí)別做出決策。這不節(jié)能,因?yàn)檫@意味著主機(jī)需要不斷轉(zhuǎn)換。AD4696可配置為根據(jù)用戶(hù)編程的通道序列進(jìn)行自主轉(zhuǎn)換。

自動(dòng)循環(huán)模式是用于監(jiān)視模擬輸入的絕佳模式。轉(zhuǎn)換周期有多種選擇,范圍從10 μs(100 kSPS采樣率)到800 μs(1.25 kSPS采樣率)。此模式可與閾值和滯后檢測(cè)警報(bào)結(jié)合使用,這些警報(bào)可基于每個(gè)通道進(jìn)行配置,以減少數(shù)字主機(jī)系統(tǒng)的開(kāi)銷(xiāo)。在這種情況下,主機(jī)控制器可以進(jìn)入低功耗狀態(tài),只有在觸發(fā)電平時(shí)收到AD4696的中斷時(shí)才會(huì)上電。

過(guò)采樣

過(guò)采樣和抽取是Σ-Δ架構(gòu)固有的,如本系列文章的第1部分所示。AD4696 SAR ADC內(nèi)置過(guò)采樣和抽取引擎,可進(jìn)一步降低噪聲。它有效地對(duì)連續(xù)的ADC樣本求平均值,以產(chǎn)生具有更高有效分辨率和更低噪聲的過(guò)采樣結(jié)果。AD4696的過(guò)采樣比(OSR)每增加4倍,有效位數(shù)就會(huì)增加1位。

這在測(cè)量需要更高精度的低功率信號(hào)鏈應(yīng)用中的較慢移動(dòng)信號(hào)(例如溫度)時(shí)特別有用。

其中 t樣本= 采樣周期,t中青= 周期時(shí)間(1/采樣率),OSR = 過(guò)采樣率(可編程值介于 4 和 64 之間)。

與Σ-Δ型ADC類(lèi)似,需要在性能和速度之間進(jìn)行權(quán)衡。

| 主題 | 時(shí)序注意事項(xiàng) | 低功耗信號(hào)鏈影響 |

| 抗混疊濾波器 | 可能存在影響首次轉(zhuǎn)化結(jié)果的延遲 | 與高速信號(hào)鏈相比,所需的強(qiáng)濾波更少 |

| 高阻態(tài)模式 | 切換通道時(shí)減少反沖時(shí)間 | 功率隨采樣率縮放;更少的外部電路 |

| 電流與采樣率 | 降低功耗會(huì)降低采樣率 | 降低采樣率會(huì)降低功耗 |

| 自動(dòng)循環(huán)模式 | 軟件可配置的內(nèi)部轉(zhuǎn)換啟動(dòng) | 主機(jī)控制器可以進(jìn)入低功耗狀態(tài) |

| 雙SDO和四SDOSDO | 在更高的采樣率下,回讀單個(gè)SDO無(wú)法實(shí)現(xiàn)的所有數(shù)據(jù) | 額外電路和數(shù)據(jù)速度之間的權(quán)衡 |

| 過(guò)采樣 | 樣本之間的間隔隨著過(guò)采樣的增加而增加 | 提高OSR可提高噪聲和分辨率性能 |

低功耗精密平臺(tái)

隨著全球能源成本趨勢(shì)的增加,我們了解了能源使用對(duì)自然界的影響,系統(tǒng)設(shè)計(jì)人員正在努力以降低功率預(yù)算實(shí)現(xiàn)精度。研究和找到可用的最低功耗組件可能很困難。ADI公司采用我們功耗最低的精密元件,并提供一站式信號(hào)鏈和電路,為系統(tǒng)設(shè)計(jì)人員提供最新的產(chǎn)品,從而簡(jiǎn)化設(shè)計(jì)過(guò)程。

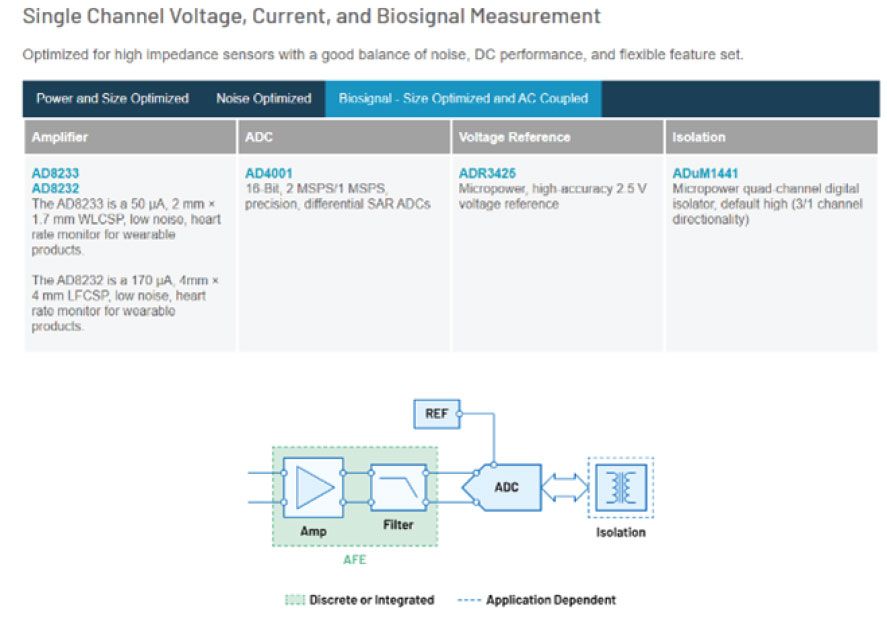

圖8.精密低功耗信號(hào)鏈網(wǎng)頁(yè)。

示例:低功耗SAR信號(hào)鏈

許多應(yīng)用需要在大直流失調(diào)或共模電壓之上測(cè)量小信號(hào)。如果系統(tǒng)的目的是監(jiān)測(cè)工業(yè)環(huán)境中的流量或進(jìn)行生物電勢(shì)測(cè)量,則該方法存在重疊。這些信號(hào)通常需要交流耦合來(lái)消除較大的失調(diào)以及偏置和增益,以最大化ADC的動(dòng)態(tài)范圍。

我們的低功耗精密信號(hào)鏈包括為此類(lèi)應(yīng)用選擇哪些器件的建議。

圖9.信號(hào)鏈?zhǔn)纠?/strong>

此外,集成知識(shí)專(zhuān)有技術(shù) (KWIK) 電路提供更深入的電路分析以及有關(guān)最新組件選擇的最新建議。

流量信號(hào)鏈?zhǔn)纠?/strong>

舉個(gè)例子,我們想設(shè)計(jì)一個(gè)大型多重測(cè)量系統(tǒng),其中包括使用圖10所示的KWIK電路進(jìn)行流量測(cè)量。

(A) 我想以 1 kSPS 的速度運(yùn)行 10 個(gè)流量傳感器。SAR 還是 sigma-delta 是更好的選擇?

(B) AFE的時(shí)間考慮是什么?

圖 10.流量測(cè)量信號(hào)鏈KWIK電路。

一個(gè)。SAR(AD4696)與信號(hào)調(diào)理所需的AD8235和ADA4505-2放大器是最佳選擇,因?yàn)槲覀兛梢允褂猛獠哭D(zhuǎn)換信號(hào)或自動(dòng)循環(huán)模式以10 kSPS運(yùn)行10個(gè)通道。

B.在這種情況下,AD4505-2放大器的響應(yīng)與增益的關(guān)系將決定被測(cè)信號(hào)的帶寬,而不是抗混疊濾波器的響應(yīng)。高阻態(tài)模式將減輕輸入放大器性能的壓力,使設(shè)計(jì)人員能夠選擇低功耗放大器。選擇圖10中的元件是因?yàn)槠涑凸男阅堋?/p>

結(jié)論

在設(shè)計(jì)高分辨率低功耗數(shù)據(jù)采集系統(tǒng)時(shí),可能很難找到功耗最低的元件,而ADI公司的精密低功耗信號(hào)鏈?zhǔn)堑凸脑O(shè)計(jì)的起點(diǎn)。在形成采用Σ-Δ和SAR架構(gòu)作為其核心ADC的信號(hào)鏈時(shí),必須謹(jǐn)慎理解時(shí)序上的權(quán)衡和差異。

與傳感器或目標(biāo)信號(hào)接口時(shí),模擬前端時(shí)序需要考慮芯片級(jí)啟動(dòng)、傳感器偏置、外部濾波和元件選擇。抗混疊濾波器對(duì)SAR ADC的要求更高,因?yàn)棣?Δ型ADC具有與其設(shè)計(jì)相關(guān)的固有采樣。在AFE上,Σ-Δ型ADC集成了PGA,而高阻態(tài)模式等SAR技術(shù)正在放寬對(duì)外部放大器電路的驅(qū)動(dòng)要求。

當(dāng)我們考慮Σ-Δ型ADC架構(gòu)時(shí),過(guò)采樣和抽取以及濾波器延遲會(huì)影響吞吐速率,尤其是在多個(gè)通道上轉(zhuǎn)換時(shí)。另一方面,由于采用逐次逼近方法,SAR吞吐量的計(jì)算更加簡(jiǎn)單,其附加好處是采樣速度越慢,轉(zhuǎn)換時(shí)消耗的電流越低。

Σ-Δ AD4130-8數(shù)字時(shí)序的復(fù)雜性促使ACE軟件時(shí)序工具的開(kāi)發(fā)。這些可用于簡(jiǎn)化理解并幫助計(jì)算通道吞吐率。同一器件具有占空比、FIFO和待機(jī)模式等定時(shí)功能,以幫助延長(zhǎng)電池壽命,但在針對(duì)特定吞吐速率時(shí),在考慮可實(shí)現(xiàn)的有效分辨率時(shí)必須小心。

當(dāng)我們檢查像AD4696這樣的SAR ADC時(shí),我們可以在更高的采樣頻率下進(jìn)行采樣。這有其優(yōu)勢(shì),但這意味著數(shù)字時(shí)間框架,t框架,其中您需要回讀的較小,這意味著需要更快的SPI時(shí)鐘速度。

-

放大器

+關(guān)注

關(guān)注

145文章

14096瀏覽量

216225 -

濾波器

+關(guān)注

關(guān)注

162文章

8065瀏覽量

180993 -

SAR

+關(guān)注

關(guān)注

3文章

424瀏覽量

46716 -

adc

+關(guān)注

關(guān)注

99文章

6635瀏覽量

548226

發(fā)布評(píng)論請(qǐng)先 登錄

優(yōu)化高速接口的時(shí)序裕量

同步電路設(shè)計(jì)中靜態(tài)時(shí)序分析的時(shí)序約束和時(shí)序路徑

模擬時(shí)序控制解決方案:可靠的上電和關(guān)斷時(shí)序

時(shí)序約束與時(shí)序分析 ppt教程

FPGA設(shè)計(jì)中的時(shí)序管理問(wèn)題

FPGA時(shí)序約束簡(jiǎn)介

使用SAR ADC構(gòu)建低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素有哪些?

靜態(tài)時(shí)序分析的基本概念和方法

時(shí)序仿真與功能仿真的區(qū)別有哪些?

數(shù)字電源時(shí)序器的內(nèi)部結(jié)構(gòu)與數(shù)字電源時(shí)序器的常見(jiàn)故障

時(shí)序電路的分類(lèi) 時(shí)序電路的基本單元電路有哪些

高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時(shí)序誤差的設(shè)計(jì)考慮

模擬前端時(shí)序、ADC時(shí)序和數(shù)字接口時(shí)序中的信號(hào)鏈考慮因素

模擬前端時(shí)序、ADC時(shí)序和數(shù)字接口時(shí)序中的信號(hào)鏈考慮因素

評(píng)論