基于憶阻器的存算一體變革性技術正成為學術界和產業界關注的前沿熱點。

在今日舉辦的創新智能芯片,共筑未來航天學術會議當中,清華大學集成電路學院院長吳華強教授做了題為《基于憶阻器存算一體芯片的研究進展》的報告。

吳華強院長以計算驅動集成電路技術的發展、基于憶阻器存算一體芯片研究進展、總結與展望三個角度展開。

計算驅動集成電路技術的發展

吳華強院長提出集成電路有兩個核心特征:信息元和信息元的超大規模集成,同時提出在集成電路的發展中有“三座大山”難以翻越,分別為“存儲墻”、“功耗墻”、“面積墻”。存算分離的傳統架構的問題帶來了“存儲墻”;“存儲墻” 導致延遲長、大量晶體管發熱的問題,引來“功耗墻”;“功耗墻”功耗高、供電和散熱復雜、曝光場大小限制芯片面積的問題,導致“面積墻”;最后“面積墻”的問題導致良率急劇降低。另外伴隨著人工智能的算法模型變得越來越復雜,模型參數量急劇增長,對計算芯片提出了巨大挑戰。美國半導體行業協會SIA在《半導體十年計劃》中指出當前計算耗能的增長速度遠超全球總能量的增長速度極大限制了算力的持續增長,未來亟需新的計算范式。

未來集成電路將通過計算范式、芯片架構和集成方法等創新,突破高算力發展瓶頸。具體創新方法為:Chiplet異質集成提高晶體管數量、存算一體技術提高每單位器件的算力、可重構異構計算架構提高算力擴展性。

計算新范式

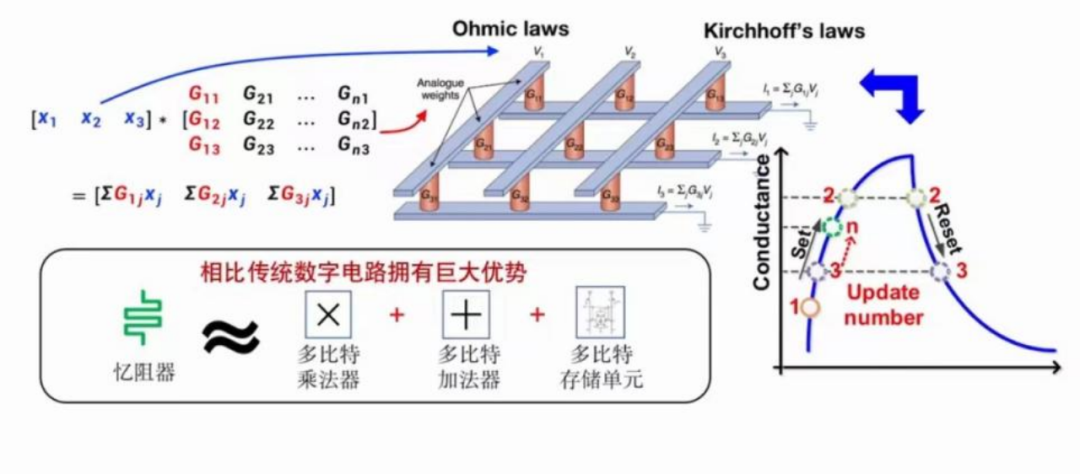

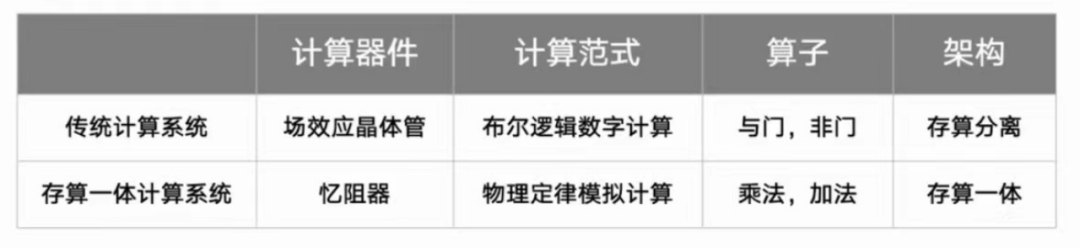

憶阻器開啟高性能計算新范式—存算一體 + 模擬計算。

憶阻器存算一體芯片由馮諾依曼架構轉向存算一體架構。

AI算力需求驅動下的模擬計算發展

AI算法對算力的需求呈爆炸式增長,數字芯片的算力已不能滿足需求。

對于AI算法,“存儲墻”成為主要的計算瓶頸,需要把大量參數配置在計算本地,不能頻繁的從DRAM搬運數據。

AI算法的算子比較集中,與憶阻器陣列的契合度很好。

AI算法中,比特精確≠系統精確,為憶阻器模擬計算提供了重要的契機。

近十年來,憶阻器存算一體技術研究已從器件與陣列演示發展到原型芯片與系統,國際競爭激烈,備受學術界與產業界關注。

基于憶阻器存算一體芯片研究進展

憶阻器的特點:電阻連續、可逆轉變,是一種新型納米器件;具有生物可信性,可作為“神經形態器件”模擬神經元、突觸功能;具備存算一體特性,可大幅提升算力和能效。

憶阻器存算一體芯片的新挑戰及解決思路

如何真正克服比特誤差對系統誤差的影響?

混合訓練框架。

如何高效、低成本的設計并制造出憶阻器存算一體芯片?

如何提升存算一體架構的通用性,使其適配更多的神經網絡算法?

發展面向存算一體芯片的軟件工具鏈。

混合訓練框架

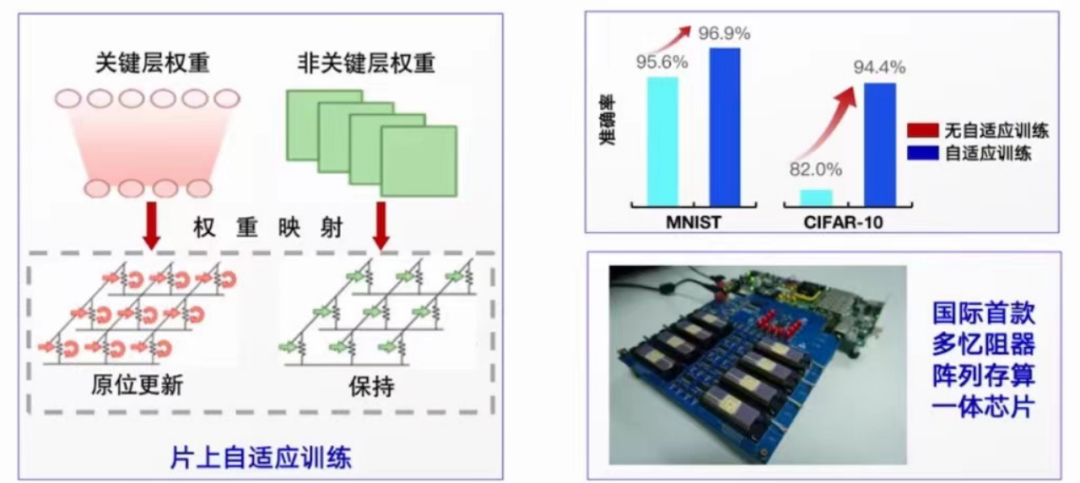

由片外壓力訓練和片上自適應訓練組成的混合訓練框架。在片外壓力訓練中引入系統誤差模型,構建具有誤差耐受性的網絡模型,提升實際硬件系統中的精度。在權重映射到芯片后,通過原位更新關鍵層權重進行自適應訓練,進一步提升精度。

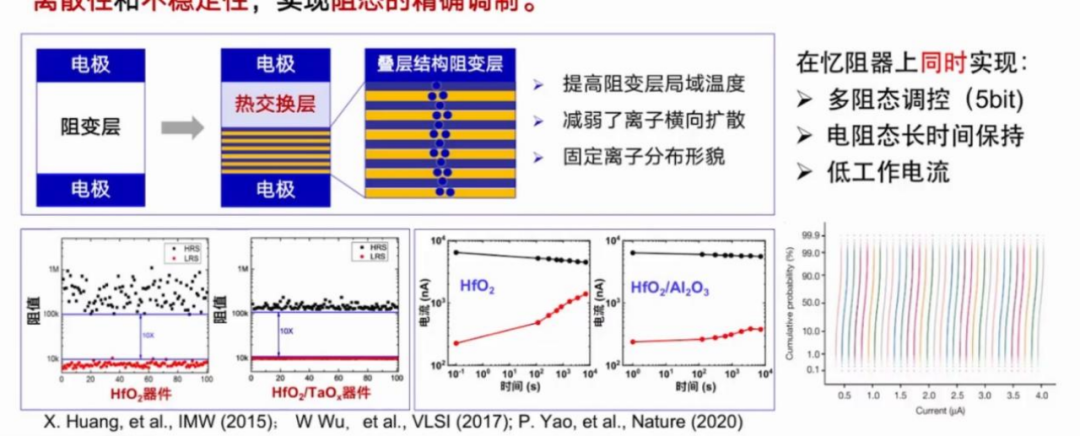

高性能憶阻器件

基于主流HfO2阻變材料,設計熱交換層和疊層結構的新器件結構,有效抑制了憶阻器離散性和不穩定性,實現阻態的精確調制。

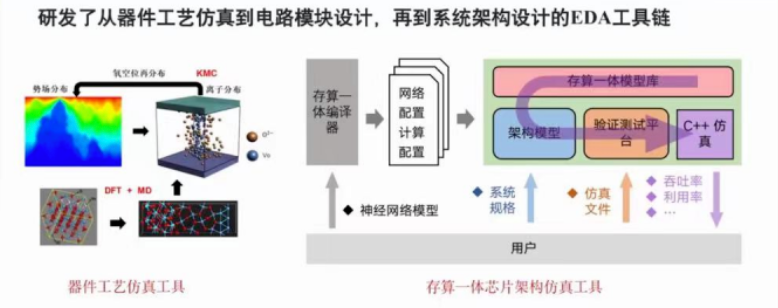

EDA工具鏈

研發從器件工藝仿真到電路模塊設計,再到系統架構設計的EDA工具鏈。

存算一體芯片軟件工具鏈

編譯器:對接算法層,實現向存算一體計算單元上高效部署神經網絡算法以及生成可執行程序的功能。

軟件模擬:對接編譯器/算法層,集成底層硬件模型,考慮真實器件的非理想因素,實現對真實硬件功能與性能的評估與探索。

硬件模擬器:對接編譯器,功能完整的計算單元模塊,模擬存算一體SoC工作過程中的數據信號與控制信號變化情況。

研究進展

吳華強教授分享了清華大學在憶阻器存算一體方面的諸多進展:

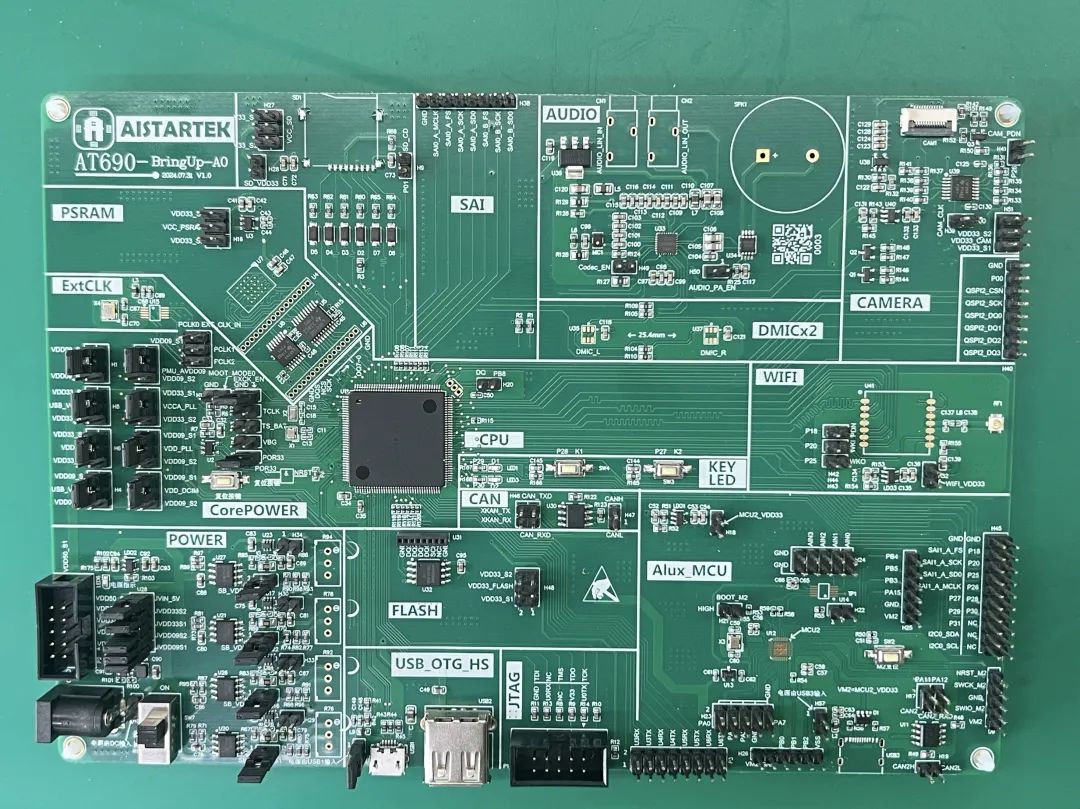

1.國際首顆全系統集成的憶阻器存算一體芯片:清華大學與華為合作研發存算一體邊緣智能芯片,是國際第一個全集成芯片。芯片的成功測試和演示有力地證明了基于憶阻器存算一體架構的可行性,130nm工藝存算一體芯片的能效相比14nm節點CPU提升了一個數量級,未來還有很大的提升潛力。

2.國際首款多陣列憶阻器存算一體系統:清華大學提出了提高系統精度的混合訓練框架,完成多層卷積神經網絡,能效比英偉達GPU高110倍,證明多陣列存算一體技術的可行性和能效、算力優勢。

3.多核、可重構的憶阻器存算一體芯片:清華大學與斯坦福大學等合作,通過軟硬件跨層次協同優化,實現通用、高能效存算一體芯片。

總結與展望

最后,吳華強教授提到,基于憶阻器的存算一體變革性技術將帶來很多變化:其一,從底層器件到編譯器等層面的改變,實現新計算機系統,但不改變現有編程語言;其二,新計算系統能效將提高102-103倍以上,達到1POPs/W;其三,單芯片算力可以得到有效提升,達到500TOPs或者1POPs。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52169瀏覽量

436104 -

集成電路

+關注

關注

5420文章

11947瀏覽量

367134 -

憶阻器

+關注

關注

8文章

75瀏覽量

20296

原文標題:清華大學集成電路學院院長吳華強教授:基于憶阻器存算一體芯片的研究進展

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

蘋芯科技 N300 存算一體 NPU,開啟端側 AI 新征程

濟南市中區存算一體化智算中心上線DeepSeek

梯度科技推出DeepSeek智算一體機

存算一體行業2024年回顧與2025年展望

自旋憶阻器:最像大腦的存儲器

開源芯片系列講座第24期:基于SRAM存算的高效計算架構

直播預約 |開源芯片系列講座第24期:SRAM存算一體:賦能高能效RISC-V計算

存算一體化與邊緣計算:重新定義智能計算的未來

存算一體架構創新助力國產大算力AI芯片騰飛

科技新突破:首款支持多模態存算一體AI芯片成功問世

后摩智能首款存算一體智駕芯片獲評突出創新產品獎

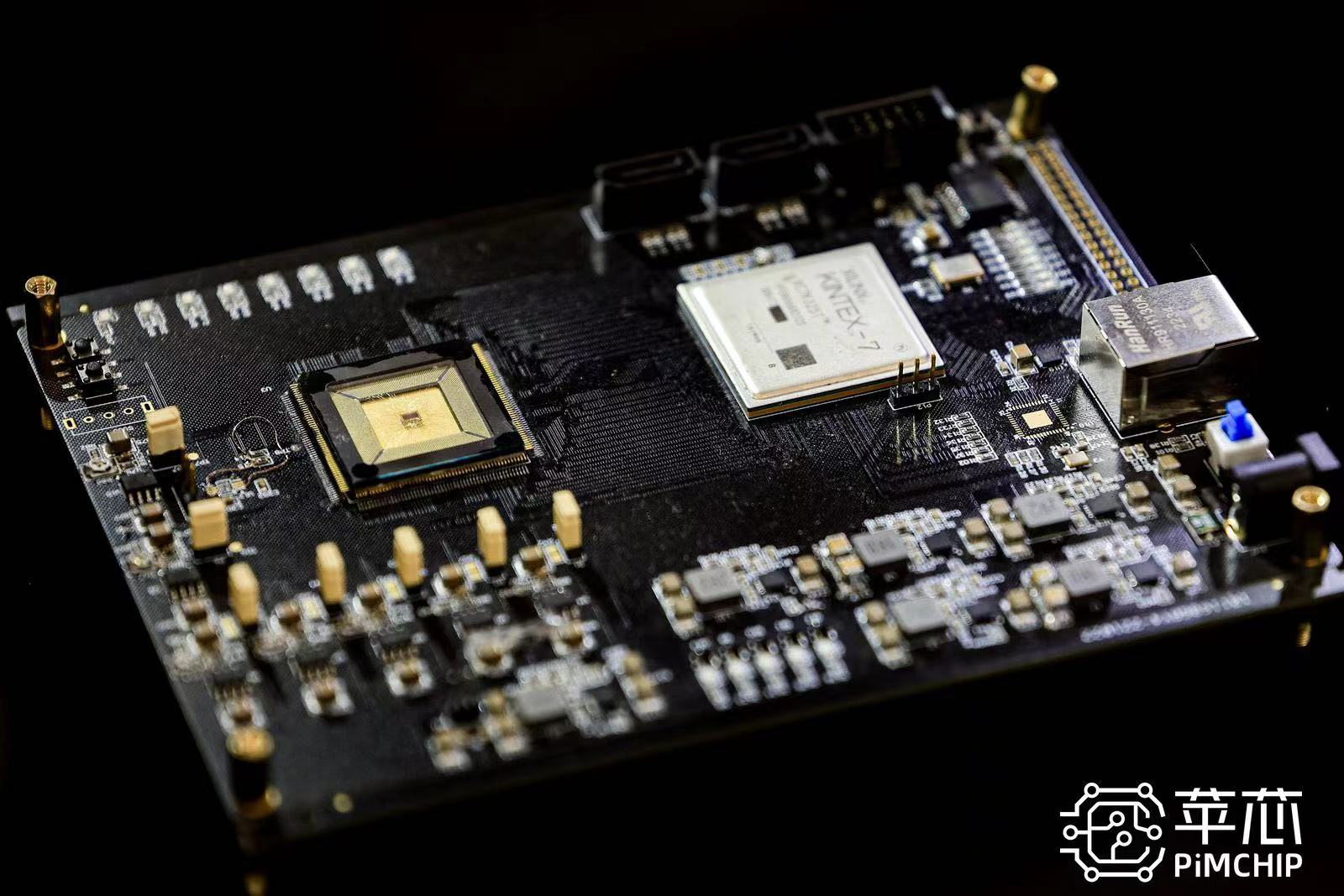

蘋芯科技引領存算一體技術革新 PIMCHIP系列芯片重塑AI計算新格局

基于憶阻器存算一體芯片的研究進展

基于憶阻器存算一體芯片的研究進展

評論