1. 驗(yàn)證的主流語言為什么是System Verilog語言?

一個掌握Verilog語言的工程師初次看SystemVerilog都會有這樣的感受,這就是Verilog啊,很容易啊,So easy啊。沒錯,確實(shí)是這樣,System Verilog的產(chǎn)生就是因?yàn)樾酒O(shè)計(jì)規(guī)模不斷增長,功能日趨復(fù)雜,單純的用Verilog和VHDL等硬件語言已經(jīng)無法滿足驗(yàn)證的需求,結(jié)合C,C++等軟件語言,又顯得難度太大,不容易掌握,因此產(chǎn)生了SystemVerilog,當(dāng)然也產(chǎn)生了其他驗(yàn)證語言,比如Vera和e語言,但因?yàn)镾ystemVerilog結(jié)合了來自 Verilog、VHDL、C++的概念,還有驗(yàn)證平臺語言(OpenVera和e語言)和斷言語言(OVA和PSL),使得SystemVerilog在驗(yàn)證界坐穩(wěn)了第一的寶座。它將硬件描述語言(HDL)與現(xiàn)代的高層級驗(yàn)證語言(HVL)結(jié)合了起來。使其對于進(jìn)行當(dāng)今高度復(fù)雜的設(shè)計(jì)驗(yàn)證的驗(yàn)證工程師具有相當(dāng)大的吸引力。這些都使得SystemVerilog在一個更高的抽象層次上提高了設(shè)計(jì)建模的能力。隨著不斷地發(fā)展,System Verilog擁有芯片設(shè)計(jì)及驗(yàn)證工程師所需的全部結(jié)構(gòu),它集成了面向?qū)ο?a target="_blank">編程、動態(tài)線程和線程間通信等特性,作為一種工業(yè)標(biāo)準(zhǔn)語言,SV全面綜合了RTL設(shè)計(jì)、測試平臺、斷言和覆蓋率,為系統(tǒng)級的設(shè)計(jì)及驗(yàn)證提供強(qiáng)大的支持作用。另一方面,驗(yàn)證方法學(xué)(VMM、OVM、AVM和UVM等)的推動也功不可沒,System Verilog能夠和芯片驗(yàn)證方法學(xué)結(jié)合在一起,即作為實(shí)現(xiàn)方法學(xué)的一種語言工具。使用驗(yàn)證方法學(xué)可以大大增強(qiáng)模塊復(fù)用性、提高芯片開發(fā)效率,縮短開發(fā)周期。

2.出鏡率較高的數(shù)據(jù)類型

邏輯(logic)類型。

四狀態(tài)類型:interger,reg,logic,time,wire,tri

雙狀態(tài)數(shù)據(jù)類型(更好的性能,更低的內(nèi)存消耗)。

二狀態(tài)類型:bit,int,byte,shortint,longint

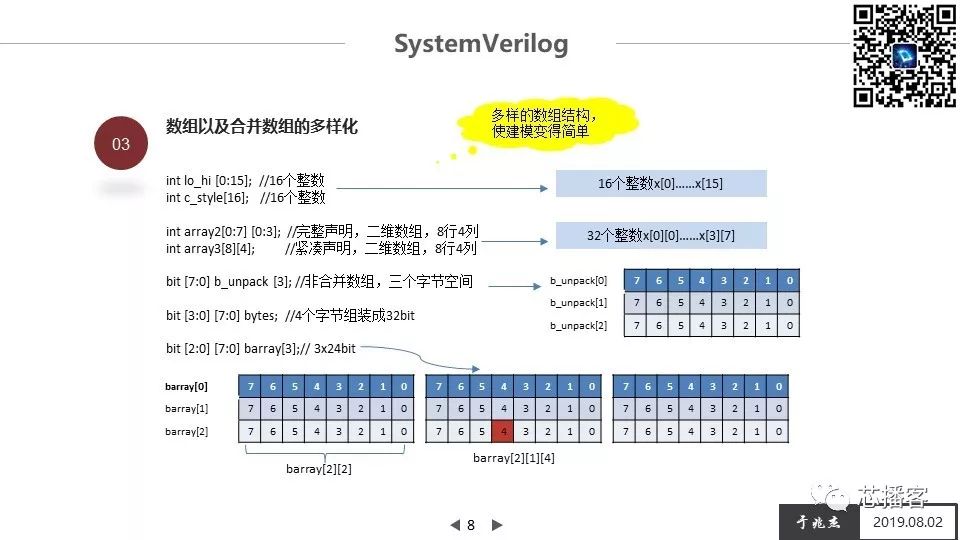

隊(duì)列,動態(tài)和關(guān)聯(lián)數(shù)組(自帶搜索和分類功能)

隊(duì)列和數(shù)組的操作,常常用在reference model建模或者checker的數(shù)據(jù)比對過程中。隊(duì)列的操作包括常用函數(shù):insert,delete,push_back, pop_back, push_front, push_back等;數(shù)組的操作(min最小值,max最大值,unique排除重復(fù),find索引相關(guān),sum求和,sort升序,rsort降序,reverse倒序,shuffle亂序等。

關(guān)聯(lián)數(shù)組(對于非常大的尋址空間存儲建模,我們只需要訪問邊界值,以及中間個別一些空間進(jìn)行驗(yàn)證,關(guān)聯(lián)數(shù)組提供保存稀疏矩陣的元素)。

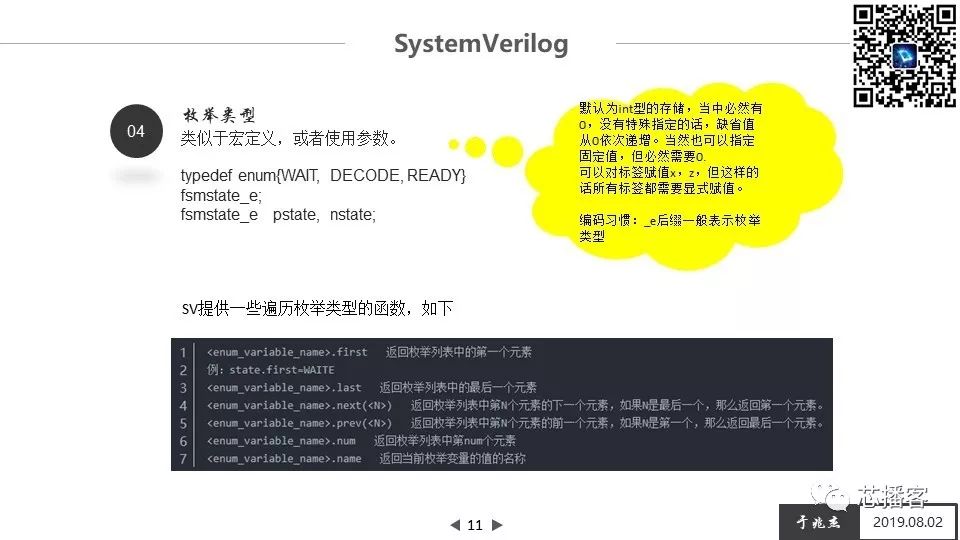

枚舉類型

類似于宏定義,或者使用參數(shù)。

typedef enum{WAIT, DECODE, READY}fsmstate_e;

fsmstate_e pstate,nstate;

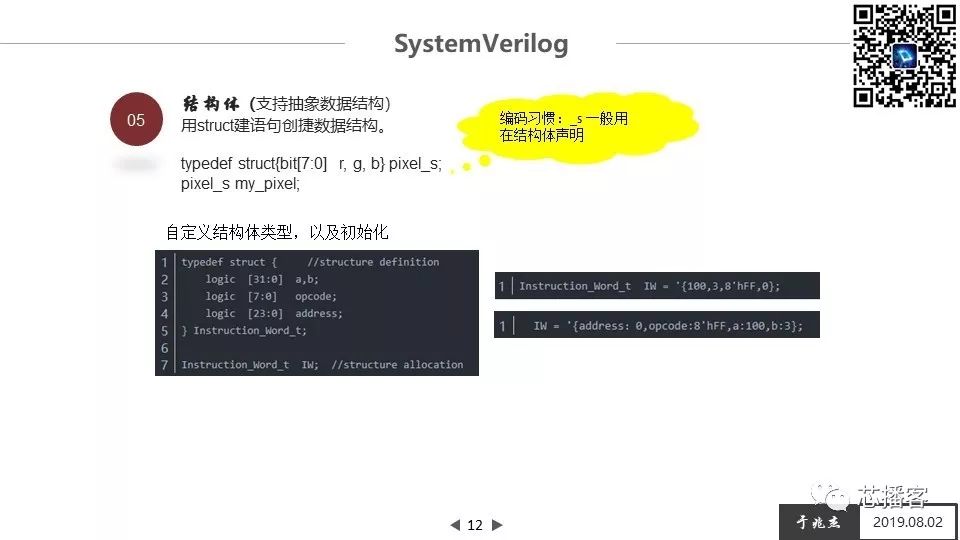

結(jié)構(gòu)體(支持抽象數(shù)據(jù)結(jié)構(gòu))用struct建語句創(chuàng)建數(shù)據(jù)結(jié)構(gòu)。

typedef struct{bit[7:0] r, g, b} pixel_s;

pixel_s my_pixel;

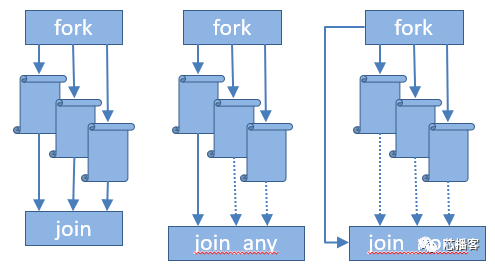

fork...join塊可以指定一條或多條語句,每一條語句都應(yīng)該作為并發(fā)進(jìn)程執(zhí)行。

| 選項(xiàng) | 描述 |

| join | 父進(jìn)程會阻塞直到這個分支產(chǎn)生的所有進(jìn)程結(jié)束。 |

| join_any | 父進(jìn)程會阻塞直到這個分支產(chǎn)生的任意一個進(jìn)程結(jié)束。 |

| join_none | 父進(jìn)程會繼續(xù)與這個分支產(chǎn)生的所有進(jìn)程并發(fā)執(zhí)行。在父線程執(zhí)行一條阻塞語句之前,產(chǎn)生的進(jìn)程不會啟動執(zhí)行。 |

Function和Task

function執(zhí)行不消耗時間,帶時間的操作如#100ns,@,wait等都不能出現(xiàn)在function。所以一般而言,function是不能調(diào)用task的,但是在fork……join_none中例外。函數(shù)可以有返回值。

消耗時間的操作用task,比如driver里面對信號的驅(qū)動過程,一般來講是在task中完成,但是具體的算法是由function完成的,所以,task中調(diào)用function。task沒有返回值。

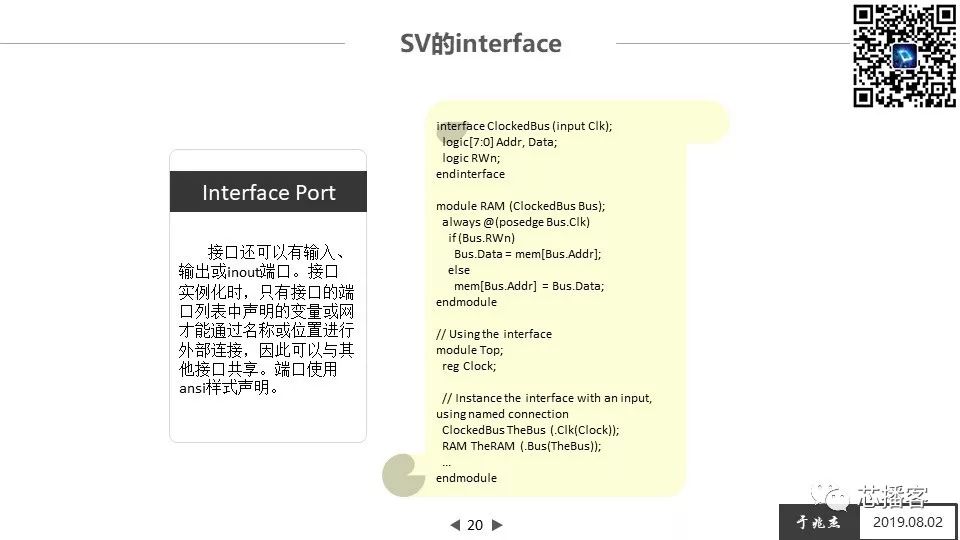

3. System Verilog的Interface

這是一個比較新的概念,Interface封裝了連接性:接口可以作為單個項(xiàng)目通過端口傳遞,從而用單個名稱替換一組名稱。這減少了建模端口連接所需的代碼量,并提高了端口連接的可維護(hù)性和可讀性。封裝功能,與通過接口連接的模塊隔離。因此,通信協(xié)議的抽象級別和粒度可以完全獨(dú)立于模塊進(jìn)行細(xì)化。

可以包含參數(shù)、常量、變量、函數(shù)和任務(wù)、流程和連續(xù)分配,這對于系統(tǒng)級建模和測試應(yīng)用程序都很有用。

可以幫助構(gòu)建功能覆蓋記錄和報(bào)告、協(xié)議檢查和斷言等應(yīng)用程序。

可以用于無端口訪問:接口可以作為模塊中的靜態(tài)數(shù)據(jù)對象直接實(shí)例化。因此,可以從設(shè)計(jì)中的不同點(diǎn)調(diào)用用于訪問接口內(nèi)部狀態(tài)信息的方法來共享信息。

靈活性:接口可以像模塊一樣參數(shù)化。此外,可以使用未指定的接口實(shí)例化(稱為泛型接口)創(chuàng)建模塊頭。這個接口可以在稍后實(shí)例化模塊時指定。

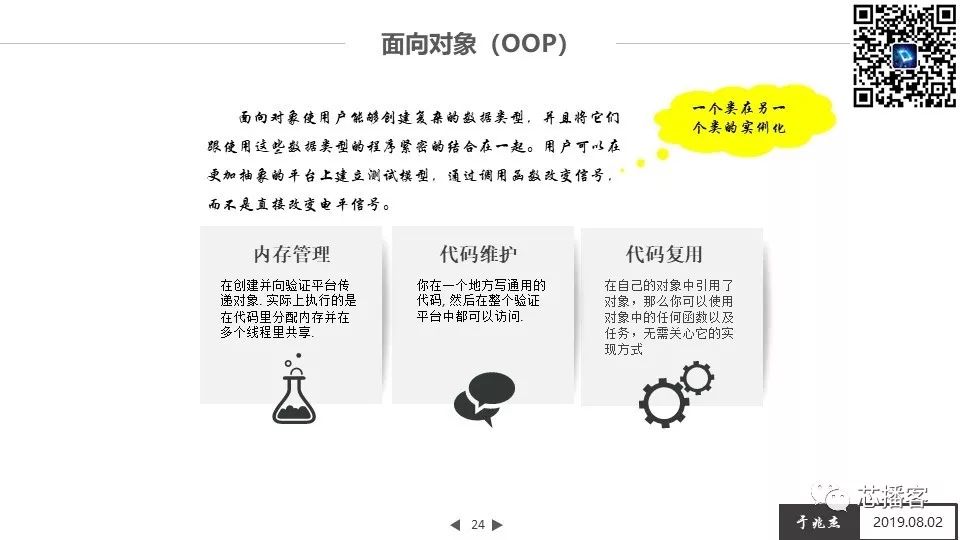

4. System Verilog的面向?qū)ο螅∣OP)

面向?qū)ο笫褂脩裟軌騽?chuàng)建復(fù)雜的數(shù)據(jù)類型,并且將它們跟使用這些數(shù)據(jù)類型的程序緊密的結(jié)合在一起。用戶可以在更加抽象的平臺上建立測試模型,通過調(diào)用函數(shù)改變信號,而不是直接改變電平信號。

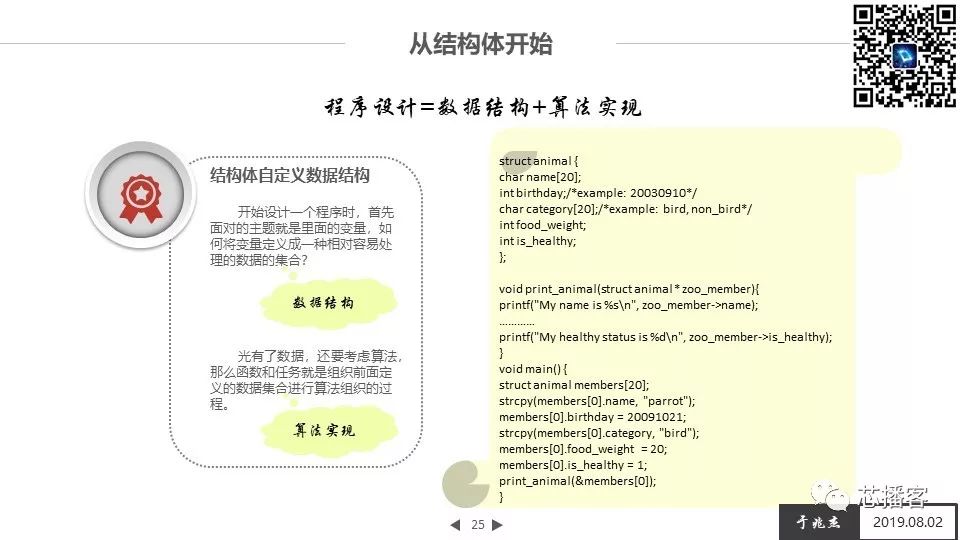

從結(jié)構(gòu)體開始:程序設(shè)計(jì)=數(shù)據(jù)結(jié)構(gòu)+算法實(shí)現(xiàn)

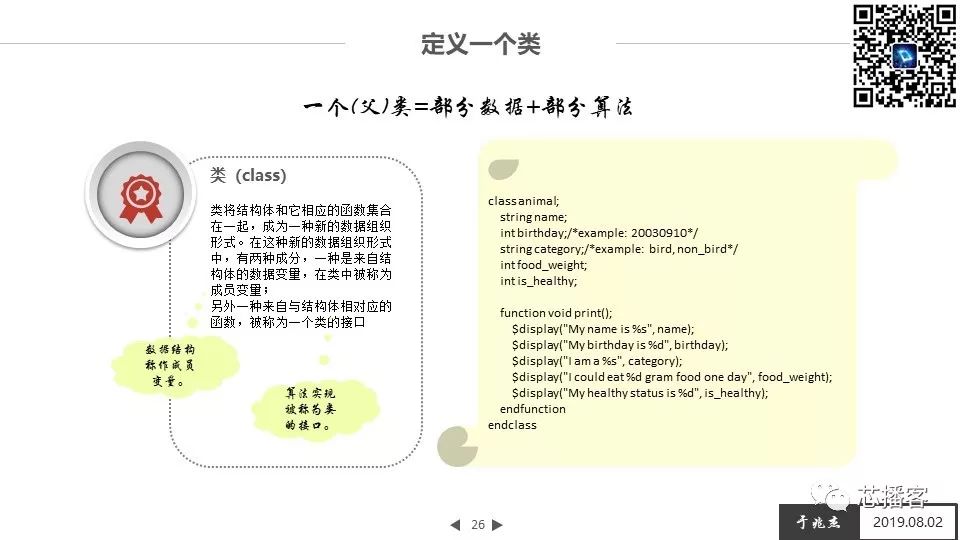

定義一個類

類將結(jié)構(gòu)體和它相應(yīng)的函數(shù)集合在一起,成為一種新的數(shù)據(jù)組織形式。在這種新的數(shù)據(jù)組織形式中,有兩種成分,一種是來自結(jié)構(gòu)體的數(shù)據(jù)變量,在類中被稱為成員變量;另外一種來自與結(jié)構(gòu)體相對應(yīng)的函數(shù),被稱為一個類的接口。

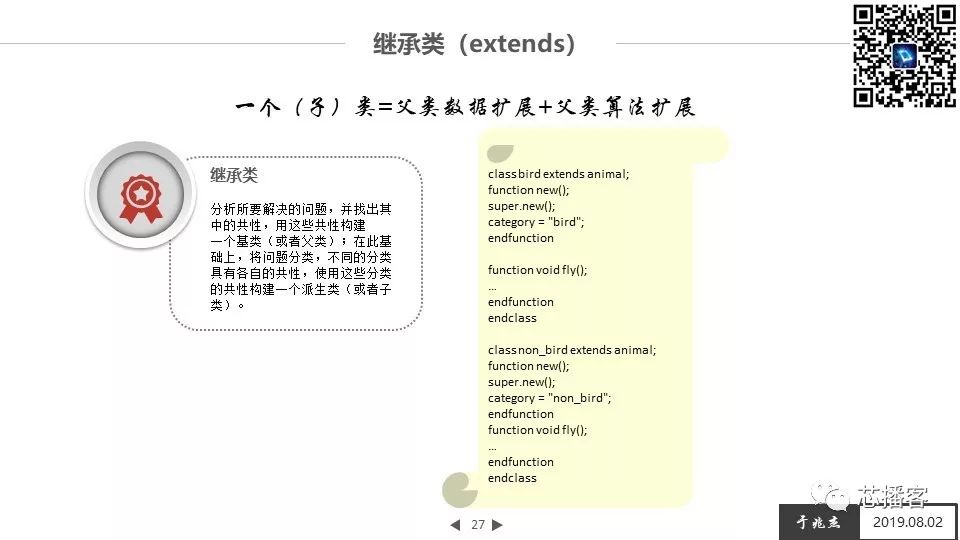

繼承一個類

分析所要解決的問題,并找出其中的共性,用這些共性構(gòu)建一個基類(或者父類);在此基礎(chǔ)上,將問題分類,不同的分類具有各自的共性,使用這些分類的共性構(gòu)建一個派生類(或者子類)。

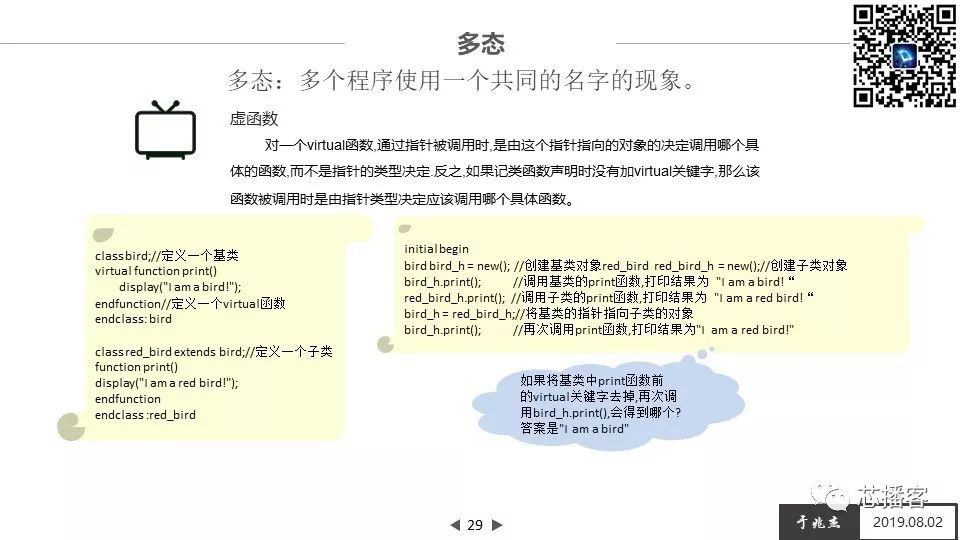

多態(tài):多個程序使用一個共同的名字的現(xiàn)象。

靜態(tài)變量和方法

一個類的所有實(shí)例都共享變量的一個版本,也就是說所有實(shí)例都共享同一個copy,該變量對所有實(shí)例都是可見并相同的。使用關(guān)鍵字static產(chǎn)生。

類的參數(shù)化定義

審核編輯 :李倩

-

Verilog

+關(guān)注

關(guān)注

28文章

1366瀏覽量

111624 -

C++

+關(guān)注

關(guān)注

22文章

2116瀏覽量

74671 -

芯片驗(yàn)證

+關(guān)注

關(guān)注

5文章

35瀏覽量

47497

原文標(biāo)題:學(xué)會這些System Verilog方法,芯片驗(yàn)證入門沒問題

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

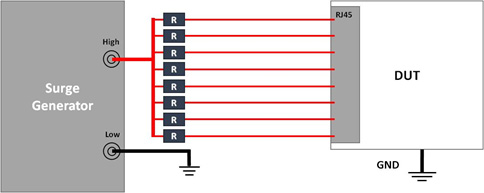

“System Level EOS Testing Method”可以翻譯為: “系統(tǒng)級電性過應(yīng)力測試方法”

新思科技推出基于AMD芯片的新一代原型驗(yàn)證系統(tǒng)

淺談Verilog和VHDL的區(qū)別

Verilog 電路仿真常見問題 Verilog 在芯片設(shè)計(jì)中的應(yīng)用

Verilog 與 ASIC 設(shè)計(jì)的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設(shè)計(jì)方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

FPGA編程語言的入門教程

如何利用Verilog-A開發(fā)器件模型

【「數(shù)字IC設(shè)計(jì)入門」閱讀體驗(yàn)】+ 概觀

十天學(xué)會單片機(jī)可能嗎?單片機(jī)入門需要多久?

學(xué)會這些System Verilog方法,芯片驗(yàn)證入門沒問題

學(xué)會這些System Verilog方法,芯片驗(yàn)證入門沒問題

評論