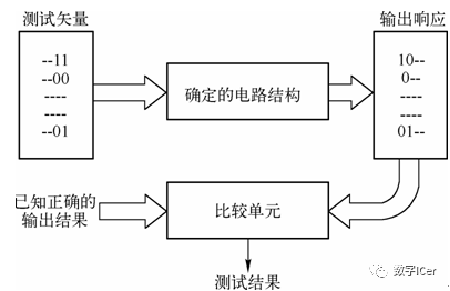

1.測試概念和原理

測試包含了三方面的內(nèi)容:

已知的測試矢量

確定的電路結(jié)構(gòu)

已知正確的輸出結(jié)果

試方式的分類

測試矢量

窮舉測試矢量是指所有可能的輸入矢量。

測試矢量

功能測試矢量主要應(yīng)用于驗證測試中,目的是驗證各個器件的功能是否正確。

測試矢量

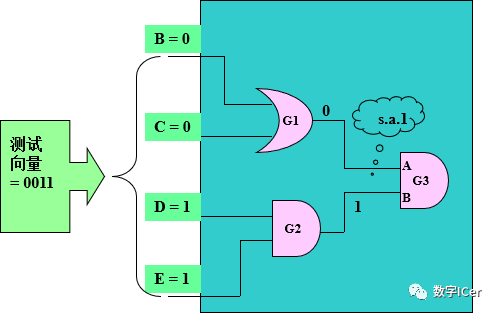

這是一種基于故障模型的測試矢量,它的最大好處是可以利用電子設(shè)計自動化(EDA)工具自動對電路產(chǎn)生測試向量,并且能夠有效地評估測試效果。

向量舉例說明

例如,如果要測試74181ALU,其有14個輸入端口

窮舉測試向量,就需要214=16384個測試矢量,對于一個有38個輸入端口的16位的ALU來說,以10 MHz的速度運(yùn)行完所有的測試矢量需要7.64個小時.

功能測試向量,要448個測試矢量,但是目前沒有算法去計算矢量是否覆蓋了芯片的所有功能。

結(jié)構(gòu)測試向量,要47個測試矢量。這類測試矢量的缺點(diǎn)是有時候工具無法檢測所有的故障類型。

測試的目的

尋找最小的測試向量集去覆蓋更多的芯片以及板級的故障

衡量標(biāo)準(zhǔn):故障覆蓋率

2.可測性設(shè)計

可測性設(shè)計基礎(chǔ)

所謂可測性設(shè)計是指設(shè)計人員在設(shè)計系統(tǒng)和電路的同時,考慮到測試的要求,通過增加一定的硬件開銷,獲得最大可測性的設(shè)計過程。

目前,主要的可測性設(shè)計方法有:

掃描通路測試(Scan)

內(nèi)建自測試(BIST)

邊界掃描測試(Boundary Scan)

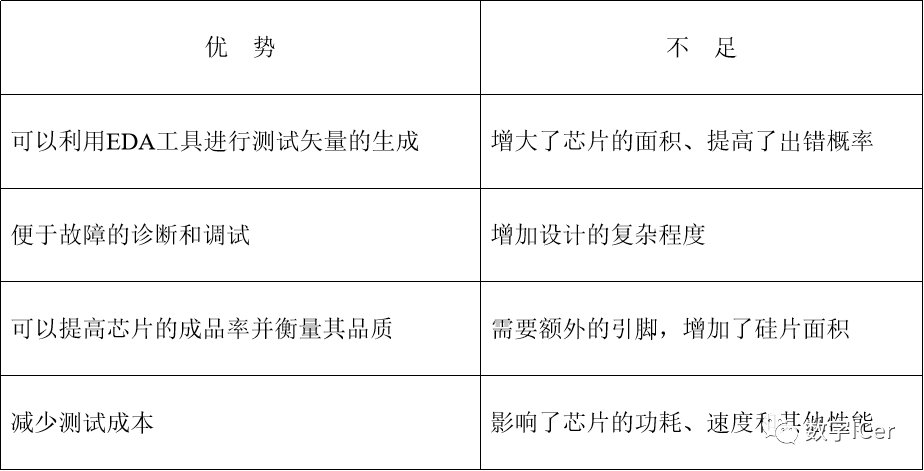

可測性設(shè)計的優(yōu)勢和不足

3.可測性方法(SCAN、BIST、 Boundary SCAN)

掃描通路測試 Scan

可測試性

Scan的基本概念

掃描測試設(shè)計規(guī)則

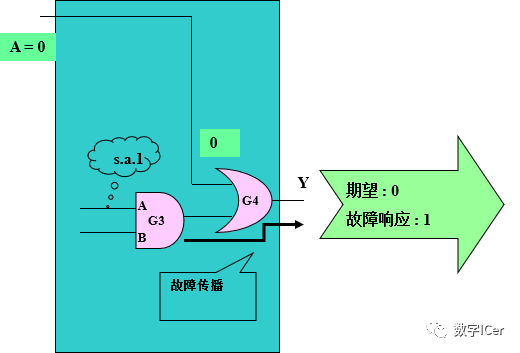

可控制性:把激勵施加到被測單元的能力

可觀察性:故障傳播到原始輸出端的能力

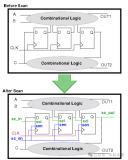

掃描測試的基本概念

掃描測試是目前數(shù)字集成電路設(shè)計中最常用的可測性設(shè)計技術(shù),這里說的是內(nèi)部掃描,不同于邊界掃描。

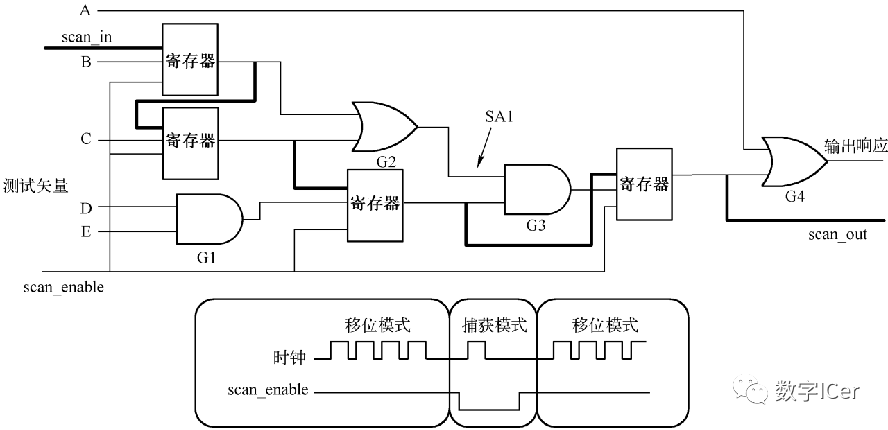

掃描時序分成時序和組合兩部分,從而使內(nèi)部節(jié)點(diǎn)可以控制并且可以觀察。

測試矢量的施加及傳輸是通過將寄存器用特殊設(shè)計的帶有掃描功能的寄存器代替,使其連接成一個或幾個長的移位寄存器鏈來實現(xiàn)的。

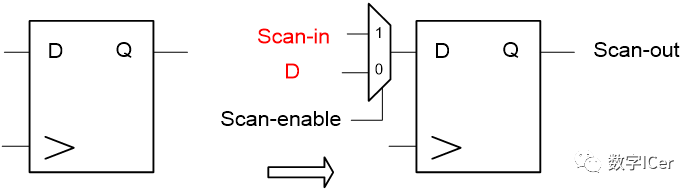

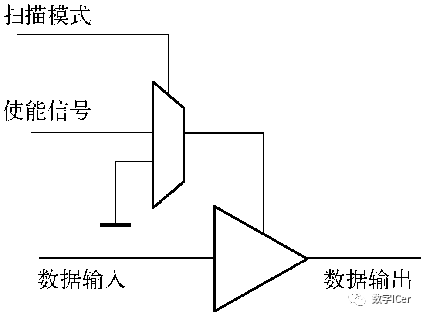

帶多路選擇器的D型觸發(fā)器

正常工作模式:scan_enable為0,此時數(shù)據(jù)從D端輸入,從Q端輸出。

掃描移位模式:scan_enable為1,此時數(shù)據(jù)從scan_in輸入,從scan_out端輸出。

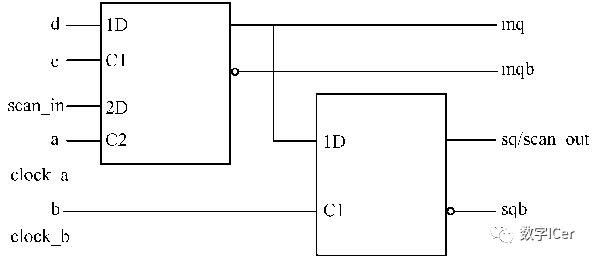

帶掃描端的鎖存器

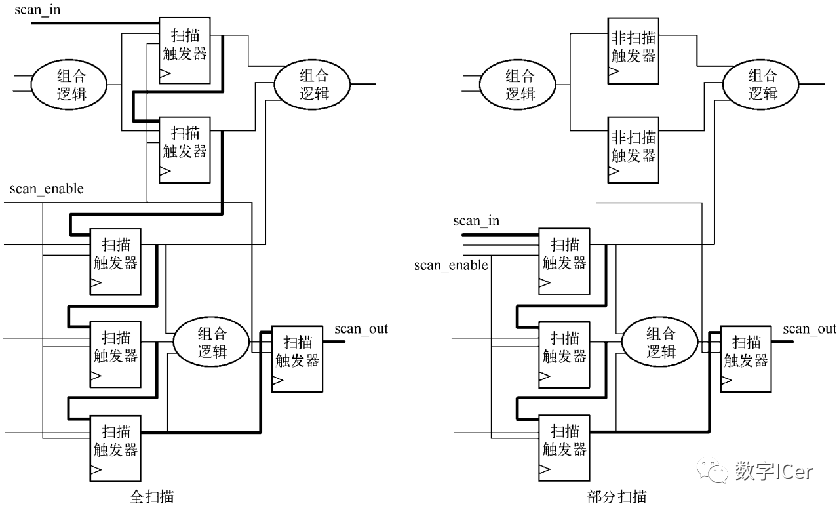

全掃描和部分掃描

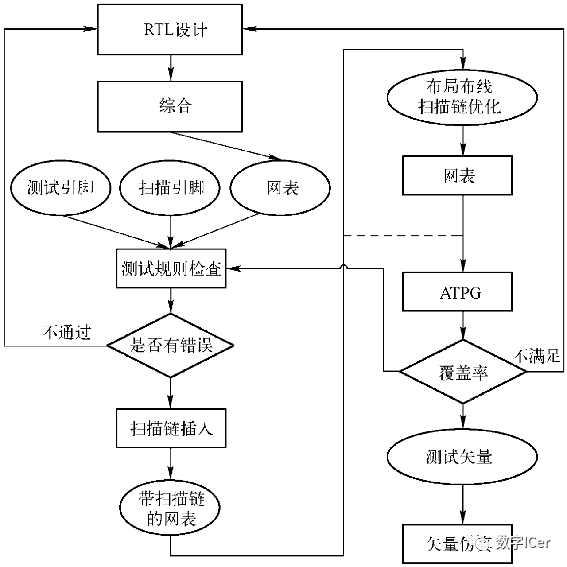

掃描測試原理

掃描設(shè)計規(guī)則

掃描測試要求電路中每個節(jié)點(diǎn)處于可控制和可觀測的狀態(tài),只有這樣才能保證其可替換為相應(yīng)的掃描單元,并且保證故障覆蓋率。

為了保證電路中的每個節(jié)點(diǎn)都符合設(shè)計需求,在掃描鏈插入之前會進(jìn)行掃描設(shè)計規(guī)則的檢查。

基本掃描規(guī)則

使用同種類掃描單元進(jìn)行替換,通常選擇帶多路選擇器的掃描觸發(fā)器;

在原始輸入端必須能夠?qū)λ杏|發(fā)器的時鐘端和異步復(fù)位端進(jìn)行控制;

時鐘信號不能作為觸發(fā)器的輸入信號;

三態(tài)總線在掃描測試模式必須處于非活躍狀態(tài);

ATPG無法識別的邏輯應(yīng)加以屏蔽和旁路。

三態(tài)總線

為了避免掃描模式(scan_mode)下的總線競爭,必須控制其控制端,通常的做法是在控制端加入多路選擇器,使其固定在邏輯0或者邏輯1

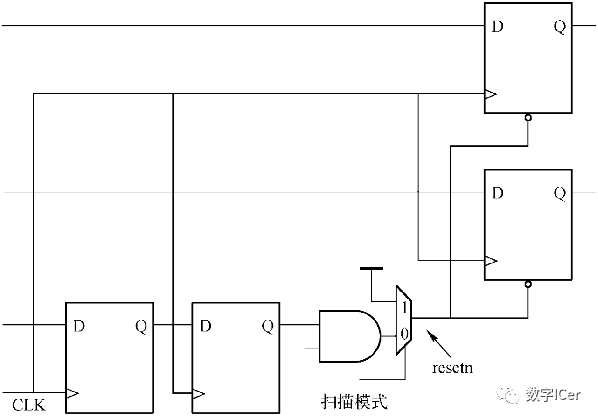

門控時鐘或者門控異步輸入端

為了避免掃描模式下resetn不可控制,處理方法和三態(tài)總線一樣,加入額外邏輯,讓異步輸入端處于非有效狀態(tài)

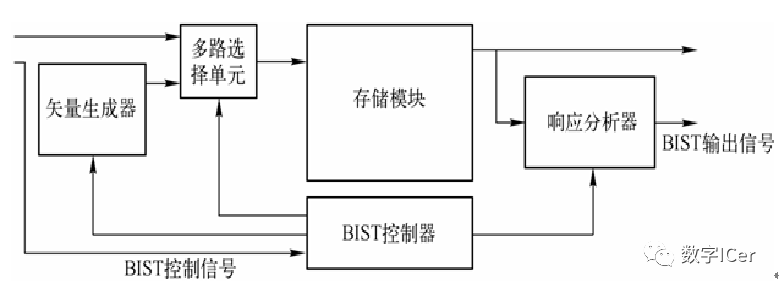

內(nèi)建自測試BIST

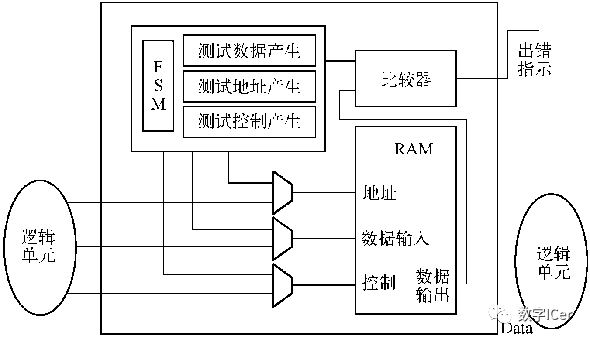

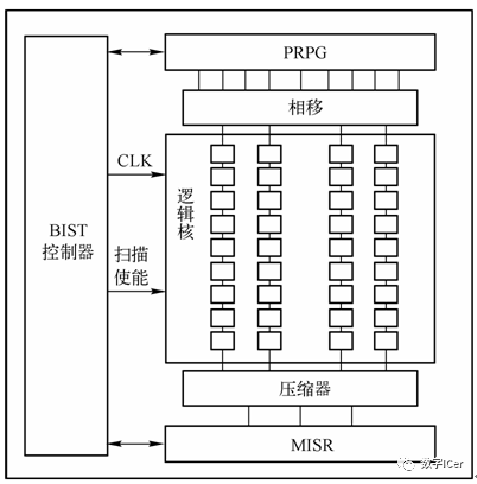

內(nèi)建自測必須附加額外的電路,包括向量生成器、BIST控制器和響應(yīng)分析器

BIST測試引腳:

BIST_MODE:測試模式選擇信號,控制電路進(jìn)入BIST狀態(tài)。

BIST_RESET:初始化BIST控制單元。

BIST_CLK:BIST測試時鐘。

BIST_DONE:輸出信號,標(biāo)志自測結(jié)束。

BIST_FAIL:輸出信號,標(biāo)志自測失敗,說明存儲器有制造故障。

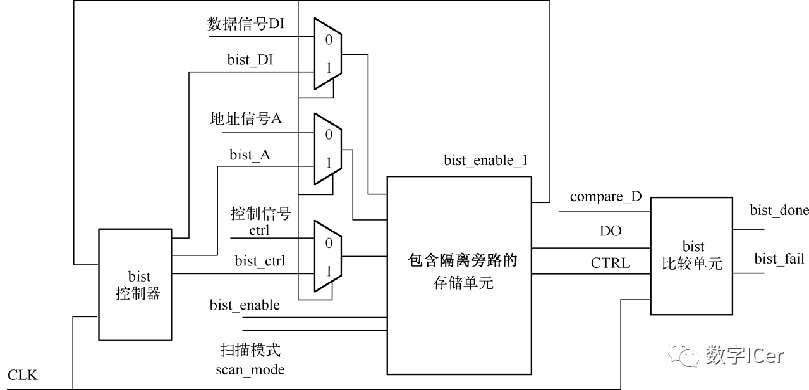

BIST模塊在設(shè)計中的集成

BIST電路作為邏輯電路的一部分通常在RTL級插入,并且需要與其他邏輯一起進(jìn)行綜合。數(shù)據(jù)、地址和一些控制信號在進(jìn)入存儲器之前需要經(jīng)過多路選擇器。

許多EDA工具可以在RTL級自動生成BIST電路并集成到設(shè)計中,其中最常用的是Mentor的mBISTArchitect和Synopsys的SoCBIST

邊界掃描測試

IEEE 1149.1標(biāo)準(zhǔn)

邊界掃描是歐美一些大公司聯(lián)合成立的一個組織——聯(lián)合測試行動小組(JTAG),為了解決印制電路板(PCB)上芯片與芯片之間互連測試而提出的一種解決方案。由于該方案的合理性,它于1990年被IEEE采納而成為一個標(biāo)準(zhǔn),即IEEE 1149.1。

該標(biāo)準(zhǔn)規(guī)定了邊界掃描的測試端口、測試結(jié)構(gòu)和操作指令。

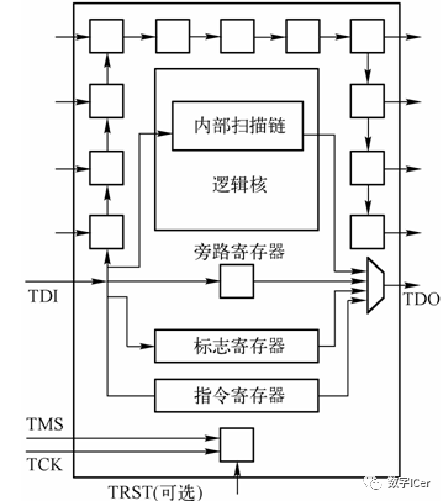

IEEE 1149.1結(jié)構(gòu)

主要包括TAP控制器和寄存器組。

寄存器組包括邊界掃描寄存器、旁路寄存器、標(biāo)志寄存器和指令寄存器

JTAG的基本原理

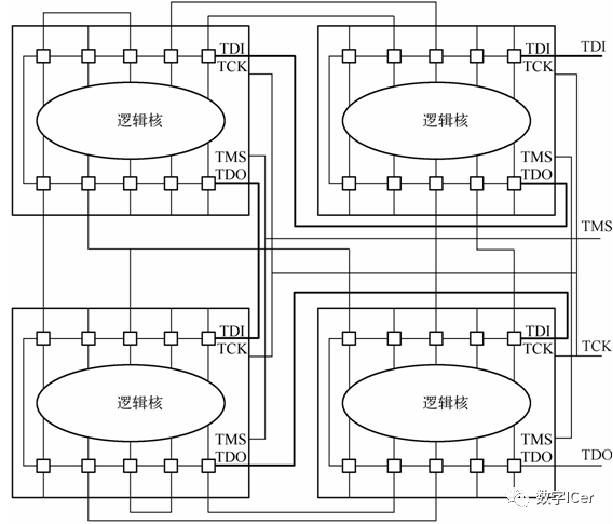

是在器件內(nèi)部定義一個TAP(Test Access Port,測試訪問口)通過專用的JTAG測試工具對內(nèi)部節(jié)點(diǎn)進(jìn)行測試。JTAG測試允許多個器件通過JTAG接口串聯(lián)在一起,形成一個JTAG鏈,能實現(xiàn)對各個器件分別測試。

端口定義

TCK:Test Clock邊界掃描設(shè)計中的測試時鐘是獨(dú)立的,因此與原來IC或PCB上的時鐘是無關(guān)的,也可以復(fù)用原來的時鐘。

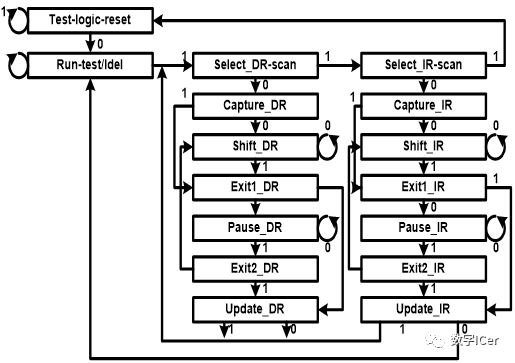

TMS:Test Mode Select由于在測試過程中,需要有數(shù)據(jù)捕獲、移位、暫停等不同的工作模式,因此需要有一個信號來控制。在IEEE 1149.1中,僅有這樣一根控制信號,通過特定的輸入序列來確定工作模式,采用有限狀態(tài)機(jī)來實現(xiàn)。該信號在測試時鐘TCK的上升沿采樣。

TDI:Test Data In以串行方式輸入的數(shù)據(jù)TDI有兩種。一種是指令信號,送入指令寄存器;另一種是測試數(shù)據(jù)(激勵、輸出響應(yīng)和其他信號),它輸入到相應(yīng)的邊界掃描寄存器中去。

TDO:Test Data Out以串行輸出的數(shù)據(jù)也有兩種,一種是從指令寄存器移位出來的指令,另一種是從邊界掃描寄存器移位出來的數(shù)據(jù)。

除此之外,還有一個可選端口TRST,為測試系統(tǒng)復(fù)位信號,作用是強(qiáng)制復(fù)位。

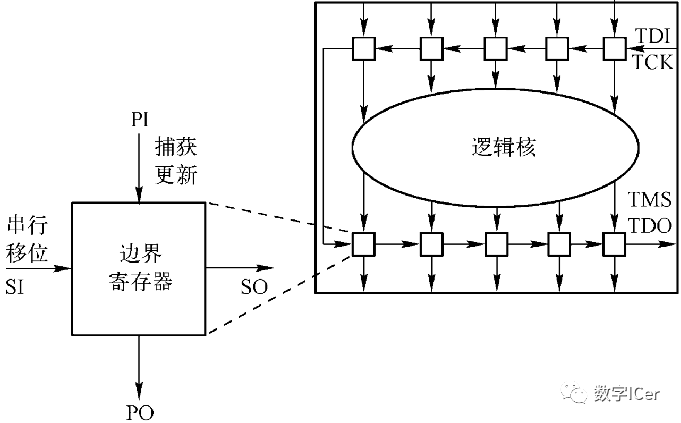

邊界掃描的原理

在核心邏輯電路的輸入和輸出端口都增加一個寄存器,通過將這些I/O上的寄存器連接起來,可以將數(shù)據(jù)串行輸入被測單元,并且從相應(yīng)端口串行讀出。

首先是芯片級測試,即可以對芯片本身進(jìn)行測試和調(diào)試,使芯片工作在正常功能模式,通過輸入端輸入測試矢量,并通過觀察串行移位的輸出響應(yīng)進(jìn)行調(diào)試。

其次是板級測試,檢測集成電路和PCB之間的互連。實現(xiàn)原理是將一塊PCB上所有具有邊界掃描的IC中的掃描寄存器連接在一起,通過一定的測試矢量,可以發(fā)現(xiàn)元件是否丟失或者擺放錯誤,同時可以檢測引腳的開路和短路故障。

最后是系統(tǒng)級測試,在板級集成后,可以通過對板上CPLD或者Flash的在線編程,實現(xiàn)系統(tǒng)級測試。

板級芯片的互連測試

TAP控制器

TAP控制器的作用是將串行輸入的TMS信號進(jìn)行譯碼,使邊界掃描系統(tǒng)進(jìn)入相應(yīng)的測試模式,并且產(chǎn)生該模式下所需的各個控制信號。

邊界掃描寄存器

邊界掃描寄存器

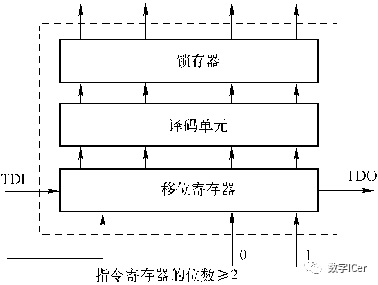

指令寄存器

指令寄存器由移位寄存器和鎖存器組成,長度等于指令的長度。IR可以連接在TDI和TDO的兩端,經(jīng)TDI串行輸入指令,并且送入鎖存器,保存當(dāng)前指令。

在這兩部分中有個譯碼單元,負(fù)責(zé)識別當(dāng)前指令。由于JTAG有3個強(qiáng)制指令,所以該寄存器的寬度至少為2位。

邊界掃描測試策略

利用邊界掃描IEEE 1149.1進(jìn)行板級測試的策略分以下3步。

根據(jù)IEEE 1149.1標(biāo)準(zhǔn)建立邊界掃描的測試結(jié)構(gòu)

利用邊界掃描測試結(jié)構(gòu),對被測部分之間的連接進(jìn)行矢量輸入和響應(yīng)分析。這是板級測試的主要環(huán)節(jié),也是邊界掃描結(jié)構(gòu)的主要應(yīng)用。可以用來檢測由于電氣、機(jī)械和溫度導(dǎo)致的板級集成故障

對單個核心邏輯進(jìn)行測試,可以初始化該邏輯并且利用其本身的測試結(jié)構(gòu)。

邏輯單元BIST

Logic BIST是SoC設(shè)計中芯片可測性設(shè)計的發(fā)展方向。

大多數(shù)的ASIC使用基于掃描的DFT技術(shù)。對于規(guī)模越來越大的芯片來說,掃描測試的策略面臨著巨大的挑戰(zhàn)。

整體DFT實現(xiàn)及性能上考慮

盡量避免異步時鐘設(shè)計;

限制不同時鐘域的數(shù)量;

對于多時鐘域的設(shè)計,處于同一時鐘域的觸發(fā)器最好連在同一根掃描鏈上;

注意扇出比較多的端口,如scan_enable信號,尤其在綜合的時候需要特別注意;

對于存儲器、模擬電路等不可綜合的邏輯加入適當(dāng)?shù)母綦x旁路結(jié)構(gòu);

避免過長的掃描鏈;

考慮到測試模式下功耗過高所造成的問題,可將掃描測試分成數(shù)個部分,分開進(jìn)行插入,在不同的掃描測試模式下,測試不同的部分;

盡量減少額外邏輯帶來的面積、功耗的增大;

通過復(fù)用外圍引腳,減少掃描測試對引腳的要求。

掃描設(shè)計流程

審核編輯 :李倩

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123398 -

DFT

+關(guān)注

關(guān)注

2文章

233瀏覽量

23245 -

矢量

+關(guān)注

關(guān)注

0文章

97瀏覽量

24026

原文標(biāo)題:可測性設(shè)計DFT

文章出處:【微信號:數(shù)字ICer,微信公眾號:數(shù)字ICer】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

借助DFT技術(shù)實現(xiàn)競爭力最大化

AEC-Q102認(rèn)證之器件可焊性

提升激光焊錫與銅可焊性的關(guān)鍵措施

淺談DFT可測性設(shè)計的工作原理

EE-345:SHARC處理器的啟動內(nèi)核定制和固件可升級性

DFT的常見誤區(qū)與解決方案

DFT在生物信號分析中的應(yīng)用

DFT的優(yōu)缺點(diǎn)比較 DFT在機(jī)器學(xué)習(xí)中的應(yīng)用

DFT與離散時間傅里葉變換的關(guān)系 DFT在無線通信中的應(yīng)用

DFT在圖像處理中的作用 DFT在音頻信號處理中的應(yīng)用

如何使用DFT進(jìn)行頻譜分析

DFT在信號處理中的應(yīng)用 DFT與FFT的區(qū)別

西門子推出Tessent In-System Test軟件

PCB可制造性設(shè)計:開啟高效生產(chǎn)的鑰匙

可測性設(shè)計DFT

可測性設(shè)計DFT

評論