嵌入式源漏選擇性外延是指在 MOS 晶體管的源漏區(qū)域,選擇性地外延生長一層原位摻雜的半導體單晶層(如摻雜的單晶硅或鍺硅)。這也是單軸應變(Uniaxial Strain) 的應用實例。因為使用嵌入式源漏工藝可以使得 MOS 場效應晶體管性能顯著提升,包括開態(tài)電流的增大和開關速度的增加,故被廣泛用于邏輯集成電路 65nm 以下技術節(jié)點。目前在集成電路工業(yè)中,對于p-MOS 場效應晶體管,嵌入式源漏工藝一般是指在源漏區(qū)域外延生長一層p型摻雜(如硼等)的單晶鍺硅 SiGe;而對于 n-MoS 場效應晶體管,一般是指指在源漏區(qū)域外延生長一層n型摻雜(如磷、砷等)的單晶硅 Si 或碳化硅 SiC。

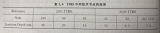

通常,選擇性外延是在低溫下進行的。降低外延生長溫度的一個方法是降低工藝過程中的壓力,目前減壓的外延生長是在 40~100Torr 壓力下操作的,所需的工藝溫度約為 1000℃。當工藝壓力進一步降低到 0.01-0.02Torr 時,操作的溫度可以降低到 750~800°C。產(chǎn)生的應力大小除了與工藝參數(shù)和鍺等雜質(zhì)濃度的分布有關,還與鍺硅與溝道不同的相對位置密切相關。

源漏選擇性外延一般采用氮化硅或二氧化硅作為硬掩模遮蔽層,利用刻蝕氣體抑制遮蔽層上的外延生長,僅在曝露出硅的源漏極區(qū)域?qū)崿F(xiàn)外延生長。源漏選擇性外延工藝一般包括外延前預清洗、外延 SiCoNi 清洗、原位氫氣烘焙、選擇性外延生長4個步驟。外延前預清洗一般在酸槽中進行,采用氫氟酸 (HF)和 RCA 清洗表面氧化層和雜質(zhì);外延 SiCoNi 清洗用于去除自然氧化層;原位氫氣烘焙進一步降低硅片表面的氧原子、碳原子含量;選擇性外延生長,即利用化學氣相外延方法,通入反應氣體源,包括硅源(如 SiH4、SiH2CL2、Si2H6等)、鍺源(GeH4)、刻蝕氣體 (HCl、Cl2)、載流氣體(H2、N2)等,在硅片表面通過氣相化學反應生長外延層。

對于 p-MOS 器件的嵌入式鍺硅工藝,利用鍺、硅晶格常數(shù)的不同,在源漏區(qū)域外延生長鍺硅(晶格常數(shù)大于硅)后,在MOS 器件的溝道區(qū)會產(chǎn)生單軸壓應力,可以提升p-MOS 器件的空穴遷移率。在嵌入式鍺硅外延工藝開發(fā)中,一方面應通過外延工藝的優(yōu)化提高鍺硅的鍺含量和增大原位摻雜濃度,以獲得更高器件性能;另一方面還需要注意控制外延生長過程中產(chǎn)生的各種缺陷,如生長不均、晶格缺陷(如位錯、堆疊缺陷)等。另外,隨著技術的發(fā)展,器件結構的變化,嵌入式鍺硅外延工藝也發(fā)生著相應的變化。早期平面 MOS 器件中嵌入式鍺硅外延傾向于采用∑形狀的結構,而隨著三維器件 FinFET 的出現(xiàn),鍺硅外延更傾向于采用“U”形結構的源漏。

對于n-MOS 器件,源漏選擇性外延技術主要包括在源漏區(qū)域摻雜硅外延生長和摻雜碳化硅外延生長兩種技術。在n-MOs 器件中,通過摻雜硅在源漏區(qū)域的外延生長,可以提升源漏區(qū)域的硅表面水平位置,從而降低寄生電阻和后續(xù)硅化物產(chǎn)生的穿刺缺陷。為了進一步提升器件的性能,源漏外延 SiC 技術被提出,即在n-MOs 器件的源漏區(qū)選擇性外延 SiC。 由于 SiC 晶格常數(shù)小于硅,將在n-MOS溝道區(qū)產(chǎn)生單軸張應變,從而可以提高溝道電子的遷移率。但在實際工藝中,由于碳和硅的晶格常數(shù)相差較大,源漏外延 SiC 會導致出現(xiàn)外延缺陷過多、應力釋放等問題,因此該技術尚需進一步研發(fā)。

審核編輯 :李倩

-

嵌入式

+關注

關注

5150文章

19659瀏覽量

317367 -

晶體管

+關注

關注

77文章

10018瀏覽量

141599 -

MOS

+關注

關注

32文章

1358瀏覽量

96995

原文標題:嵌入式源漏選擇性外延(Embedded Source and Drain Selective Epitaxy)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

運行在嵌入式系統(tǒng)上的emApps

半導體選擇性外延生長技術的發(fā)展歷史

高可靠性嵌入式主板設計

普源精電亮相MWC 2025及Embedded World 2025

坐標德國紐倫堡,飛凌嵌入式亮相Embedded World 2025

3月11~13日,與飛凌嵌入式共赴德國紐倫堡embedded world 2025

AMD推出EPYC Embedded霄龍嵌入式8004系列處理器

mos管源極和漏極電流相等嗎

飛凌嵌入式受邀參加openEuler Embedded Meetup(廣州站)

晶體管的漏極與源極有什么區(qū)別

聚焦嵌入式開發(fā)中的合規(guī)性工具、項目管理工具、版本迭代工具應用

源漏嵌入SiGe應變技術簡介

嵌入式源漏選擇性外延(Embedded Source and Drain Selective Epitaxy)

嵌入式源漏選擇性外延(Embedded Source and Drain Selective Epitaxy)

評論