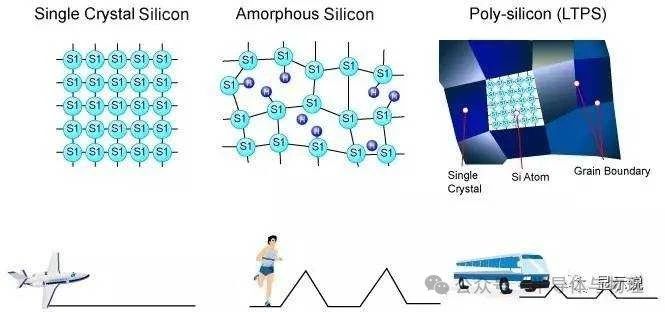

應(yīng)變硅技術(shù)是指在利用工藝過程中不同材料晶格常數(shù)失配或材料熱膨脹差異產(chǎn)生的應(yīng)力使硅原子發(fā)生應(yīng)變的技術(shù)。根據(jù)應(yīng)變的不同,應(yīng)變硅可以分為壓應(yīng)變硅(硅原子間距收縮)和張應(yīng)變硅(硅原子間距擴(kuò)張)兩種。壓應(yīng)變所產(chǎn)生的應(yīng)力稱為壓應(yīng)力或壓縮應(yīng)力,張應(yīng)變所產(chǎn)生的應(yīng)力稱為張應(yīng)力或拉伸應(yīng)力。

在先進(jìn)集成電路工藝中,引入應(yīng)變硅技術(shù)的主要目的是通過提高載流子遷移率來增大場效應(yīng)晶體管驅(qū)動電流。由于晶格結(jié)構(gòu)的變化,應(yīng)變硅的能帶結(jié)構(gòu)會發(fā)生改變,因此通過引入適當(dāng)?shù)膽?yīng)變,可以減小載流子的有效質(zhì)量,降低載流子傳輸過程的散射概率,從而提高載流子的遷移率,這是應(yīng)變硅能夠提升器件性能的機(jī)理。

在IC芯片制造工藝中,采用的主流應(yīng)變技術(shù)有全局應(yīng)變和局域應(yīng)變兩大類。全局應(yīng)變是指利用器件薄層材料和晶片之間的自然晶格常數(shù)失配,在整個器件薄層材料內(nèi)產(chǎn)生相對一致的應(yīng)變。局域應(yīng)變是指在器件表面局部區(qū)域引入應(yīng)力,通過局部區(qū)域作用到 MOS 器件溝道。局域應(yīng)變作用的效果與器件結(jié)構(gòu)密切相關(guān),而應(yīng)力臨近度(即局域應(yīng)力層臨近器件溝道的距離)是一個重要的指標(biāo)。

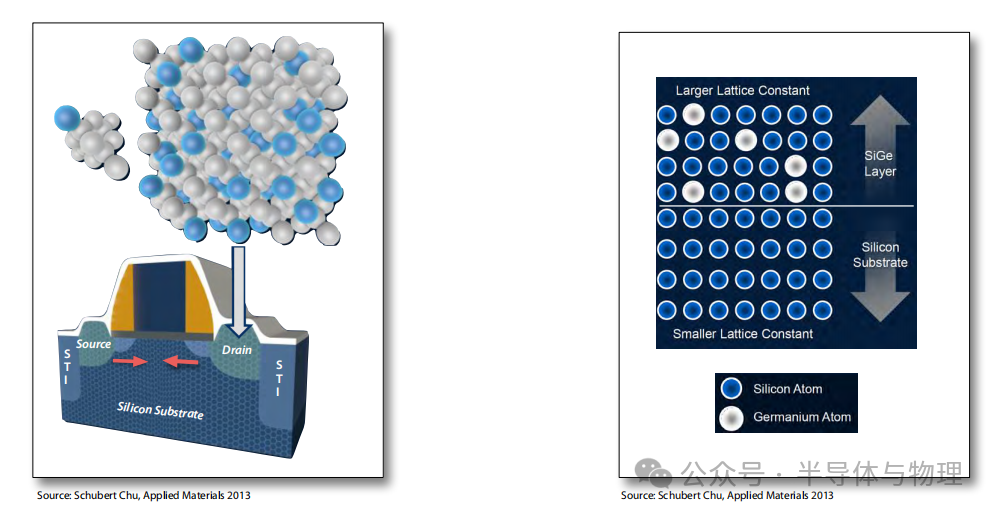

在鍺硅襯底上外延生長硅薄層是常見的全局應(yīng)變工藝,較大的鍺硅晶格常數(shù)將使硅薄層的晶格常數(shù)大于 原始值,從而在硅層內(nèi)形成張應(yīng)變,其應(yīng)力大小主要由硅薄層厚度與鍺硅虛襯底中鍺的含量決定。與全局應(yīng)變不同,局域應(yīng)變主要通過在芯片制造工藝中局部引入應(yīng)力來實(shí)現(xiàn),如在器件源漏區(qū)選擇性外延鍺硅外延等,其產(chǎn)生的應(yīng)力不僅與鍺的濃度相關(guān),而且與器件的結(jié)構(gòu)(尤其是外延層對溝道的臨近度) 有密切關(guān)系。

另外,由于應(yīng)力還受到柵側(cè)墻介質(zhì)、淺槽隔離介質(zhì)、硅化物或絕緣夾層的影響,雖然研究結(jié)果表明電子的遷移率在應(yīng)變硅材料中可以提升 70%,但是制成器件后實(shí)測的改善效果卻小于理想結(jié)果。由此可見,器件結(jié)構(gòu)和工藝流程因素限制了器件性能的提升。

根據(jù)應(yīng)變的作用方向差異,應(yīng)變還可以分為雙軸應(yīng)變(Biaxial Strain,在晶片表面的x和y兩個方向上形成相對一致的應(yīng)力)和單軸應(yīng)變 (Uniaxial Strain,在晶片表面主要沿單一方向的應(yīng)變)。 針對 CMOS 應(yīng)用的研究結(jié)果表明,沿溝道方向的張應(yīng)力有利于提升電子遷移率,故用于 n-MOS 器件;而沿溝道方向的壓應(yīng)力有助于提升空穴遷移率,故用于p-MOS 器件。

集成電路發(fā)展到 90nmn 節(jié)點(diǎn)以后,開始在 MOSFET 器件中使用應(yīng)變硅技術(shù),早期引入的應(yīng)變硅技術(shù)包括針對 p-MOS 器件的鍺硅源漏外延技術(shù)和針對 n-MOS 器件的應(yīng)力層技術(shù)。

鍺硅源漏外延技術(shù)是指在p-MOS 器件的源漏區(qū)域選擇性外延生長原位摻雜的鍺硅,利用鍺硅晶格常數(shù)高于硅,在器件溝道區(qū)產(chǎn)生壓應(yīng)變。采用應(yīng)力層技術(shù)可以生長一層應(yīng)力層介質(zhì)材料,通過熱作用等在器件溝道區(qū)產(chǎn)生應(yīng)變,如應(yīng)力記憶技術(shù) (Stress Memorization Technique, SMT) 和接觸孔刻蝕停止層(Contact Etch Stop Layer, CESL)技術(shù)。

根據(jù)工藝的不同,應(yīng)力層技術(shù)可以產(chǎn)生張應(yīng)變和壓應(yīng)變,目前最常用的是n-MOS 器件的張應(yīng)變層。此外,還可以引入雙應(yīng)力層 (Dual Stress Liner, DSL)在p-MOS 和n-MOS 器件上分別實(shí)現(xiàn)壓應(yīng)變和張應(yīng)變,但其集成難度大,較少用于實(shí)際工藝中。

對于n-MOS器件而言,還可以在源漏選擇性外延碳化硅層或極高磷摻雜濃度的Si :P層,產(chǎn)生沿溝道方向的張應(yīng)變。

審核編輯 :李倩

-

場效應(yīng)晶體管

+關(guān)注

關(guān)注

6文章

394瀏覽量

19906 -

晶格

+關(guān)注

關(guān)注

0文章

95瀏覽量

9432

原文標(biāo)題:應(yīng)變硅(Strained Silicon)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

電阻應(yīng)變傳感器的原理與應(yīng)用

應(yīng)變計的測量范圍和精度是如何界定?

OptiFDTD應(yīng)用:用于光纖入波導(dǎo)耦合的硅納米錐仿真

【峟思】應(yīng)變單位 με 是如何換算成應(yīng)力的

SiGe外延工藝及其在外延生長、應(yīng)變硅應(yīng)用及GAA結(jié)構(gòu)中的作用

應(yīng)變是反映構(gòu)件什么的?應(yīng)變計起到什么作用?

OptiFDTD應(yīng)用:用于光纖入波導(dǎo)耦合的硅納米錐仿真

振弦式應(yīng)變計測出來的應(yīng)變量有什么用

振弦式表面應(yīng)變計具有哪些功能?

案例分享 應(yīng)變測試方案

源漏嵌入SiGe應(yīng)變技術(shù)簡介

源漏嵌入SiC應(yīng)變技術(shù)簡介

應(yīng)變硅(Strained Silicon)

應(yīng)變硅(Strained Silicon)

評論