多晶硅柵的形成是集成電路工藝中最關鍵的步驟,因為它包括了最薄的柵氧化層的熱生長(干氧和濕氧),形成多晶硅柵的先進且復雜的光刻技術和干法刻蝕技術,以及需要精確控制且復雜的側墻工藝。

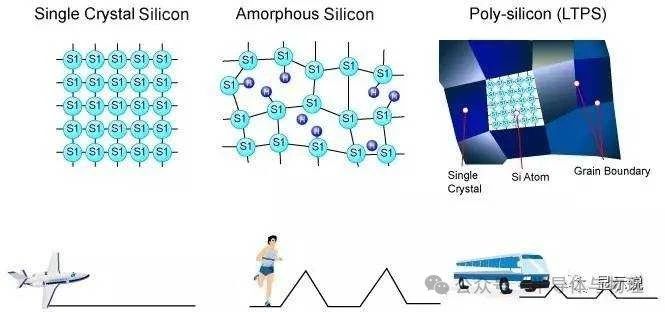

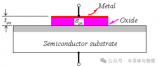

多晶硅柵結構通常是一代集成電路工藝中物理尺度最小的結構,也是形成晶體管的關鍵。多晶硅柵形成的一般流程是,首先使用高溫熱氧化生成柵氧化膜,膜的厚度約為 1~10nm(由于在集成電路中有不同工作電壓的場效應晶體管,所以柵氧化層的厚度也不相同,需要采取多個步驟才能完成不同厚度的柵氧化層),然后進行多晶硅柵的化學氣相沉積和摻雜(擴散或離子注入),最后進行光刻和干法刻蝕。

多晶硅柵光刻工藝使用的光刻機是同一技術代集成電路工藝線中最先進、最昂貴的設備,它采用 UV 光源進行曝光,波長從g線(436nm)到DUV(248pm 和 193nm),以及 193nm 浸沒式;在光刻掩模版上采用了 OPC和PSM等技術;在光刻工藝中采用了抗反射層、硬光刻膠技術、多重曝光技術等。

多晶硅柵的刻蝕采用的是最精細的刻蝕設備和技術,通常采用 NF3、 SF6~HBr、CL2,等氣體,要求與 SiO2有極高的選擇比。多晶硅柵的檢測技術也是最精細的檢測技術,用于光刻和刻蝕完成后多晶硅柵線寬和形狀等的檢測。

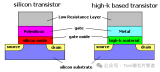

雖然在 45nm 以下的超大規模集成電路制造工藝中,為了解決多晶硅柵耗盡效應,以及多晶硅與高K介質高界面態密度等問題,多采用了高K金屬柵工藝,多晶硅柵的重要性有所降低,但是多晶硅柵工藝仍然被認為是集成電路的標志性工藝之一。

審核編輯 :李倩

-

集成電路

+關注

關注

5416文章

11923瀏覽量

366870 -

多晶硅

+關注

關注

3文章

248瀏覽量

29644

原文標題:多晶硅柵(Poly-Si Gate)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

LPCVD方法在多晶硅制備中的優勢與挑戰

芯片制造中的多晶硅介紹

多晶硅錠定向凝固生長方法

單晶圓系統:多晶硅與氮化硅的沉積

為什么采用多晶硅作為柵極材料

Poly-SE選擇性多晶硅鈍化觸點在n-TOPCon電池中的應用

多晶硅的存儲條件是什么

效率提升0.15-0.2%:雙面Poly和Poly Finger技術在TOPCon電池中的創新應用

多晶硅生產過程中硅芯的作用

多晶硅柵工藝的制造流程

光伏多晶硅的分片方法及優缺點

Poly層厚度對N型TOPCon太陽能電池電學性能的影響

多晶硅柵耗盡效應簡述

多晶硅柵(Poly-Si Gate)

多晶硅柵(Poly-Si Gate)

評論