一些關于PCB設計論壇中的遵守/避免布線法則,使得PCB設計者在這些規(guī)則也許不適用的地方要么遵守,要么忽略他們。一些情況下,這未必造成電路板設計失敗。正像一些有經(jīng)驗PCB設計者所說,電路板是出于偶然的機會恰好可以正常工作。

關于PCB設計的經(jīng)驗法則的討論并不是說他們是正確還是錯誤,問題是這些討論往往缺乏應用場合的針對性,這樣也使得規(guī)則的討論時長在論壇中被提起。本文希望將這些規(guī)則背后所適應的場景講清楚,希望將不同的規(guī)則在什么時候適用,什么時候需要避免闡釋準確。

我們不用再費周折,將一些常用到的PCB布線經(jīng)驗法則抽絲剝繭,分析它們背后所適用的場景。

一、垂直布線

最近我在文章The Case Against Orthogonal Trace Routing in Multilayer PCBs中已經(jīng)詳細討論過這個布線規(guī)則,下面將其中一些重要結論重新給出。垂直布線的規(guī)則是說在相鄰信號層的引線需要相互垂直,以減少相互之間互感引起的串擾。在高頻信號中,通過電容耦合產(chǎn)生的串擾占主要成分,在垂直引線之間產(chǎn)生電流尖峰。

當信號的變化沿時間,或者頻率較低(小于幾個GHz),相鄰信號層垂直布線件的耦合電容干擾小。在射頻(RF)頻段(幾十個GHz),引線間交織產(chǎn)生空穴諧振,沒有被地線包圍導體結構會在一些特殊頻率點產(chǎn)生電磁諧振。此時即便引線間是垂直的,也會在它們之間引起強的串擾。

為了消除一切頻率點上的干擾,簡單有效的方法就是采用多層板,在信號層之間使用隔離層。在當代信號高速變化的應用中尤其重要。當你對正交線之間耦合強度拿不準時,你需要使用基本串擾仿真軟件對垂直引線進行檢查,看它們之間的串擾是否在噪聲容然范圍之內。此時,你更需要對信號回流路徑進行規(guī)劃,這在垂直布線中是一個主要的問題。

二、散熱過孔

這是一個經(jīng)典的“遵守/避免”法則,嘗嘗引起爭論。一些PCB設計者說他們從來不使用防止散熱過孔,并從未遇到焊接和組裝方面的問題。而另外一批人則堅持防止散熱過孔需要在每一個平面相連的時候都需要使用。他們到底誰對呢?

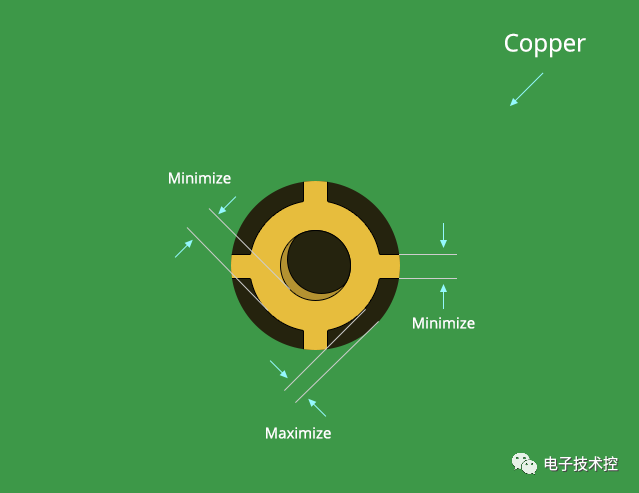

▲ 圖1.2.1 在鋪底層上設計的防止散熱的焊接通孔

他們的觀點分別適用于不同的長號。如果你手工焊接電路板時,你需要提高烙鐵頭的溫度以補償焊接過孔在銅層散熱帶來的焊接問題。但如果使用波峰焊接時,則需要使用防止散熱過孔來防止器件松脫、冷焊、立碑等現(xiàn)象,所以我建議你最好咬緊牙關堅持使用防止散熱過孔設計。

三、直角布線

這個PCB布線法則也許最令人又愛又恨。如今我仍然看到很多PCB設計者堅稱在任何時候布線都不能夠拐直角,理由也是五花八門。比如他們說電子在引線中運動時拐直角彎困難,但他們也不想想,在電路板上的所有過孔可都是與引線垂直的呀。還有些理由顯得比較靠譜,比如通過45°拐角可以減少引線長度,所有直角拐彎布線都需要倒角。還有的說直角拐彎會在電路板酸性腐蝕液中產(chǎn)生酸蝕陷阱,在現(xiàn)在廣泛使用堿性電路板腐蝕液中則沒有這個問題。

除非你的電路板工作在50GHz以上的高頻(涉及到毫米波雷達/5G通訊)電路,你無需擔心引線拐直角。實際上,在電路板布線時你可以使用任何你所喜歡的角度來鋪設引線。如果你所使用的的PCB設計軟件內置有電磁場求解功能這會使得你布線更加容易。

▲ 圖1.3.1 一些PCB設計者堅稱所有的直角拐彎的布線都需要改成帶有斜角的布線方式

四、“3W”法則

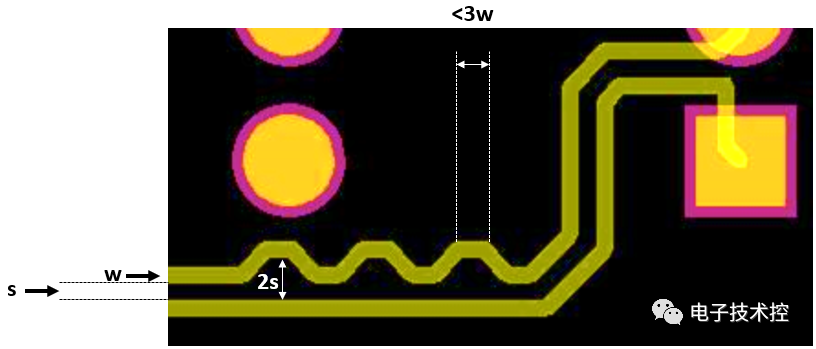

也就是三條布線經(jīng)驗法則。第一個版本的"3W法則是說,在相鄰兩條引線之間的間隔應該大于等于引線寬度的三倍 ,為的是降低引線之間的磁通量耦合,進而減少引線見得電磁干擾。

這個法則也許忘記了,引線之間的電磁耦合是與引線回路重疊面積成正比,而不是引線之間的距離;因此將引線回路重疊面積降低,引線間距不用受到3W法則限制。就像前面垂直布線一樣,通過基本電磁干擾仿真可以檢查不同布線間距帶來的影響。

“3W”法則的另外一個版本是指在引線長度匹配時所使用的鋸齒布線時,鋸齒寬度需要大于等于引線寬度的三倍,這可以將引線阻抗的不連續(xù)性降到最低。關于這一點可以在文章Length Matching for High-speed Signals: Trombone, Accordion, and Sawtooth Tuning看到更詳細的討論。

▲ 圖1.4.1 在鋸齒布線中的3W法則

五、“20H”法則

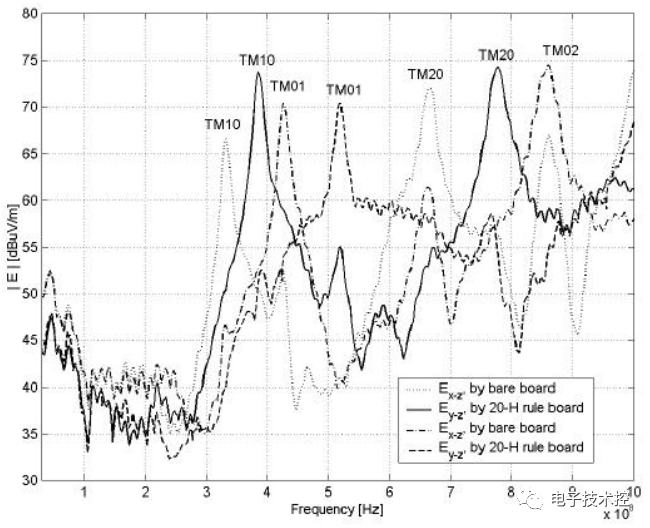

這個法則定義了PCB中的地線層與電源層之間重疊距離,在現(xiàn)代PCB設計時需要將電源鋪設在地線附近,這樣可以保證它們之間具有足夠的層間電容,進而在高速電路板上減少電源波動。

但實際測量結果會發(fā)現(xiàn)結果很復雜。有些時間結果標準名在300MHz時遵守20H法則可以降低電磁輻射。但在地線-電源層之間會出現(xiàn)高頻諧振,它們結構類似于波導,反而會加重線路之間的高頻干擾。

▲ 圖1.5.1 在一些遵守20H法則電路板設計中會出現(xiàn)不同的射頻輻射干擾

審核編輯:郭婷

-

pcb

+關注

關注

4351文章

23405瀏覽量

406529 -

射頻

+關注

關注

106文章

5725瀏覽量

169678

原文標題:PCB布線法則

文章出處:【微信號:項華電子DXE,微信公眾號:項華電子DXE】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

超強超全布線經(jīng)驗教程大全

高層數(shù)層疊結構PCB的布線策略

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

必學!PCB設計布線技巧、電機控制、電源管理設計教程等精華資料

混合信號分析儀的原理和應用場景

電子工程師的PCB設計經(jīng)驗

104條關于PCB布局布線的小技巧

是否存在有關 PCB 走線電感的經(jīng)驗法則?

PCB布線經(jīng)驗法則背后所適用的場景分析

PCB布線經(jīng)驗法則背后所適用的場景分析

評論