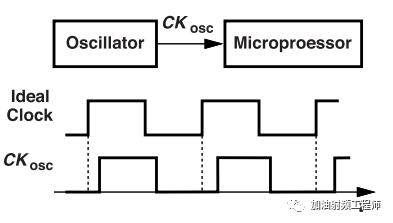

如果用一個(gè)自由振蕩的振蕩器,給MCU提供時(shí)鐘。會(huì)咋樣呢?

首先,得說(shuō)一下,簡(jiǎn)單的LC自由振蕩的振蕩器的頻率很脆弱。

哪哪都會(huì)影響到它。

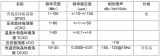

供電大小變化,它會(huì)變;環(huán)境溫度變化,它會(huì)變;工藝角變化,它也會(huì)變。

所以,如果用MCU提供時(shí)鐘的話,假設(shè)環(huán)境溫度緩慢變化,則振蕩器的輸出頻率也會(huì)緩慢變化,這樣就會(huì)引起隨機(jī)相位累積。

單獨(dú)看,可能看不太出來(lái),如果把它和標(biāo)準(zhǔn)時(shí)鐘輸出放在一起,就能感受到變化。

你會(huì)發(fā)現(xiàn),CKosc的上升沿離標(biāo)準(zhǔn)時(shí)鐘的上升沿越來(lái)越遠(yuǎn)。

而MCU的運(yùn)行是靠時(shí)鐘的上升沿或者下降沿來(lái)判別的,你上升沿和下降沿變那么多,MCU可能就運(yùn)行不正常了啊。

為了避免這個(gè)事情發(fā)生,就需要對(duì)振蕩器的相位進(jìn)行控制。

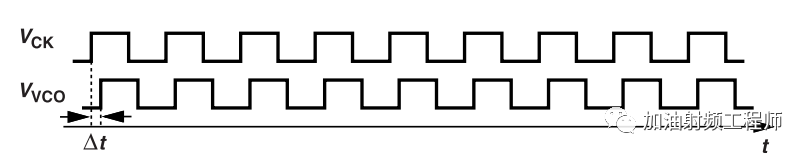

控制的目的,是希望VCO的相位與參考時(shí)鐘的相位對(duì)齊。

如下圖所示,這邊VCO的上升沿相對(duì)于VCK有Δt 秒的偏移,那怎么消除這個(gè)Δt的偏移呢。

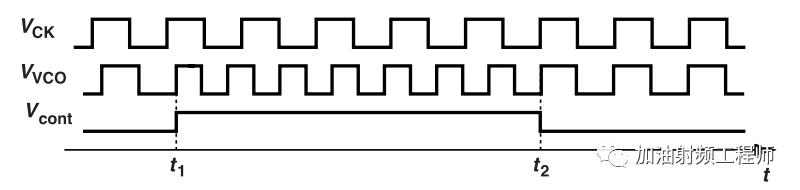

具體過(guò)程如下:

假設(shè)在t=t1時(shí),VCO的頻率突然變大,然后電路開(kāi)始累積相位差,相位誤差逐漸減小。在t=t2時(shí),VCK和VVCO之間的相位差變?yōu)?,兩信號(hào)的相位對(duì)齊。

此過(guò)程,即是將VCO的輸出相位與參考相位對(duì)齊的過(guò)程,稱為“鎖相”。

從上面的過(guò)程中,可以看出,要使得VCO的相位和參考信號(hào)的相位對(duì)齊,需要做到以下兩點(diǎn):

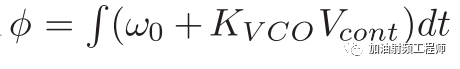

(1) VCO的頻率瞬間改變,并且能夠發(fā)生下面的積分運(yùn)算。

(2) 用鑒相器來(lái)比對(duì)兩個(gè)信號(hào)的相位差,以確定VCO和參考信號(hào)對(duì)齊的時(shí)間點(diǎn)。

將VCO的輸出相位與參考相位對(duì)齊的過(guò)程,稱為“鎖相”。

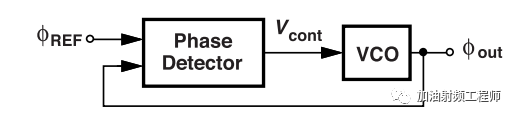

那怎么實(shí)時(shí)控制振蕩器的輸出相位呢,答案就是采用負(fù)反饋,如下圖所示。

將輸出信號(hào)的相位與參考信號(hào)的相位進(jìn)行比對(duì),用鑒相器輸出的Vcont去調(diào)節(jié)VCO的頻率和相位。

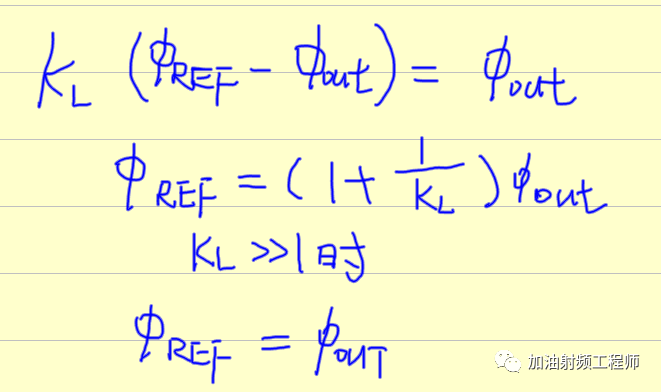

如果環(huán)路增益足夠大,則

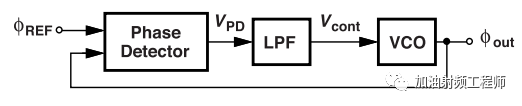

鑒相器的輸出是周期性脈沖,這會(huì)對(duì)VCO的性能產(chǎn)生影響。

為了解決這個(gè)問(wèn)題,可以在鑒相器和VCO之間加一個(gè)低通濾波器,抑制鑒相器輸出的高頻分量。

這種負(fù)反饋電路,即稱為鎖相環(huán)(PLL)。當(dāng)φin ? φout不隨時(shí)間變化(或者變化很小時(shí)),即稱環(huán)路鎖定。也就是說(shuō),這個(gè)環(huán)路的目的,是使得φin = φout,那如果是這個(gè)目的的話,為什么不直接用一根線連接呢。

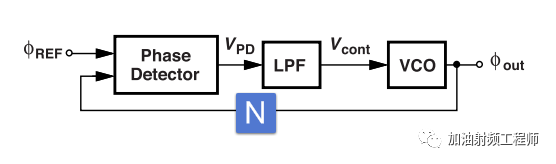

這是因?yàn)椋绻诜答伝芈飞希由弦粋€(gè)分頻器,那鎖相環(huán)就可以產(chǎn)生和參考信號(hào)差不多穩(wěn)定,但是頻率更高的信號(hào)。

審核編輯:湯梓紅

-

mcu

+關(guān)注

關(guān)注

146文章

17824瀏覽量

360073 -

振蕩器

+關(guān)注

關(guān)注

28文章

3965瀏覽量

140385 -

pll

+關(guān)注

關(guān)注

6文章

880瀏覽量

136023 -

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

69964

原文標(biāo)題:PLL為什么是這么一個(gè)結(jié)構(gòu)呢?

文章出處:【微信號(hào):加油射頻工程師,微信公眾號(hào):加油射頻工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

MOSFET是如何成為一個(gè)電流源的呢

LMX2820 PLL_NUM / PLL_DEN減到最低項(xiàng)是什么意思呢?

請(qǐng)問(wèn)如何在一個(gè)quartust里調(diào)用多個(gè)PLL

請(qǐng)問(wèn)AD9361的一個(gè)PLL對(duì)應(yīng)幾個(gè)VCO分頻器呢?

SAC內(nèi)部是個(gè)什么結(jié)構(gòu)呢

怎樣去定義一個(gè)結(jié)構(gòu)體數(shù)組呢

為什么實(shí)際距離與理論值之間會(huì)有這么大的差距呢?

模擬PLL,模擬PLL是什么意思

PLL鎖定過(guò)程的兩個(gè)步驟

PLL芯片接口方面最常見(jiàn)的11個(gè)問(wèn)題

如何建立一個(gè)簡(jiǎn)單的PLL電路

PLL為什么是這么一個(gè)結(jié)構(gòu)呢?

PLL為什么是這么一個(gè)結(jié)構(gòu)呢?

評(píng)論