鎖相環(huán)(PLL)是一種反饋系統(tǒng),其中電壓控制振蕩器(VCO)和相位比較器相互連接,使得振蕩器可以相對(duì)于參考信號(hào)維持恒定的相位角度。在使用PLL的過(guò)程中您都遇到過(guò)哪些問(wèn)題呢?咱們工程師整理了PLL芯片接口方面最常見(jiàn)的11個(gè)問(wèn)題,這里分享給大家!

1參考晶振有哪些要求?該如何選擇參考源?

波形: 可以使正弦波,也可以為方波。

功率: 滿足參考輸入靈敏度的要求。

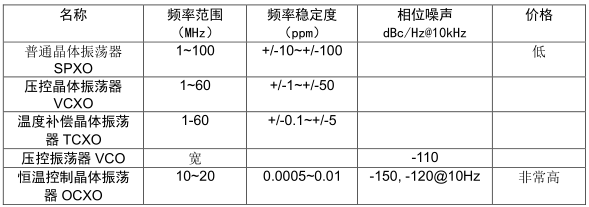

穩(wěn)定性: 通常用 TCXO,穩(wěn)定性要求《 2 ppm。這里給出幾種參考的穩(wěn)定性指標(biāo)和相位噪聲指標(biāo)。

頻率范圍: ADI 提供的 PLL 產(chǎn)品也可以工作在低于最小的參考輸入頻率下,條件是輸入信號(hào)的轉(zhuǎn)換速率要滿足給定的要求。

建議

在PLL 頻率綜合器的設(shè)計(jì)中,我們推薦使用溫度補(bǔ)償型晶振(TCXO)。在需要微調(diào)參考的情況下使用 VCXO,需要注意 VCXO 靈敏度比較小,比如 100Hz/V,所以設(shè)計(jì)環(huán)路濾波器的帶寬不能很大(比如 200Hz),否則構(gòu)成濾波器的電容將會(huì)很大,而電阻會(huì)很小。普通有源晶振,由于其溫度穩(wěn)定性差,在高精度的頻率設(shè)計(jì)中不推薦使用。

2能詳細(xì)解釋下控制時(shí)序、電平及要求嗎?

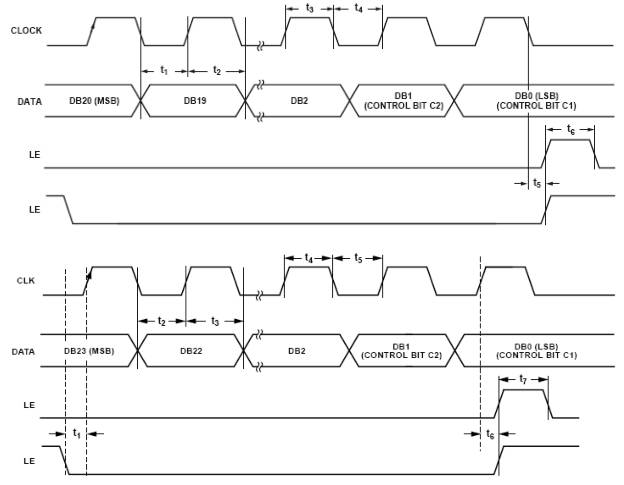

ADI 的所有鎖相環(huán)產(chǎn)品控制接口均為三線串行控制接口,如圖 1所示。要注意的是:在 ADI 的PLL 產(chǎn)品中,大多數(shù)的時(shí)序圖如圖 1中上面的圖所示,該圖是錯(cuò)誤的,正確的時(shí)序圖如圖 1中下面的圖所示,LE 的上升沿應(yīng)跟 Clock 的上升沿對(duì)齊,而非 Clock 的下降沿。

圖 1. PLL 頻率合成器的串行控制接口(3 Wire Serial Interface)

控制接口由時(shí)鐘 CLOCK,數(shù)據(jù) DATA,加載使能 LE 構(gòu)成。加載使能 LE 的下降沿提供起始串行數(shù)據(jù)的同步。串行數(shù)據(jù)先移位到 PLL 頻率合成器的移位寄存器中,然后在 LE 的上升沿更新內(nèi)部相應(yīng)寄存器。注意到時(shí)序圖中有兩種 LE 的控制方法。

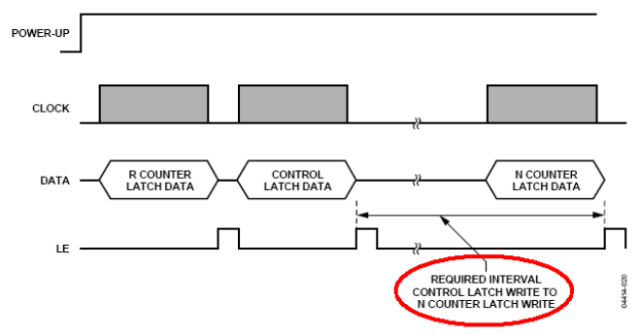

SPI 控制接口為 3V/3.3V CMOS 電平。另外,需要注意的是對(duì) PLL 芯片的寄存器進(jìn)行寫操作時(shí),需要按照一定的次序來(lái)寫,具體請(qǐng)參照芯片資料中的描述。特別地,在對(duì) ADF4360 的寄存器進(jìn)行操作時(shí),注意在寫控制寄存器和 N計(jì)數(shù)器間要有一定的延時(shí)。

控制信號(hào)的產(chǎn)生,可以用 MCU,DSP,或者 FPGA。產(chǎn)生的時(shí)鐘和數(shù)據(jù)一定要干凈,過(guò)沖小。當(dāng)用 FPGA 產(chǎn)生時(shí),要避免競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象,防止產(chǎn)生毛刺。如果毛刺無(wú)法避免,可以在數(shù)據(jù)線和時(shí)鐘線上并聯(lián)一個(gè) 10~47pF 的電容,來(lái)吸收這些毛刺。

3控制多片 PLL 芯片時(shí),串行控制線是否可以復(fù)用?

一般地,控制 PLL 的信號(hào)包括:CE,LE,CLK,DATA。CLK 和 DATA 信號(hào)可以共用,即占用2 個(gè) MCU 的 IO 口,用 LE 信號(hào)來(lái)控制對(duì)哪個(gè) PLL 芯片進(jìn)行操作。多個(gè) LE 信號(hào)也可以共用一個(gè)MCU 的 IO 口,這時(shí)需要用 CE 信號(hào)對(duì)芯片進(jìn)行上電和下電的控制。

4可否簡(jiǎn)要介紹環(huán)路濾波器參數(shù)的設(shè)置?

ADIsimPLL V3.3 使應(yīng)用工程師從繁雜的數(shù)學(xué)計(jì)算中解脫出來(lái)。我們只要輸入設(shè)置環(huán)路濾波器的幾個(gè)關(guān)鍵參數(shù),ADIsimPLL 就可以自動(dòng)計(jì)算出我們所需要的濾波器元器件的數(shù)值。這些參數(shù)包括,鑒相頻率 PFD,電荷泵電流 Icp,環(huán)路帶寬 BW,相位裕度,VCO 控制靈敏度 Kv,濾波器的形式(有源還是無(wú)源,階數(shù))。計(jì)算出的結(jié)果往往不是我們?cè)谑忻嫔夏軌蛸I到的元器件數(shù)值,只要選擇一個(gè)最接近元器件的就可以。

通常環(huán)路的帶寬設(shè)置為鑒相頻率的 1/10 或者 1/20。

相位裕度設(shè)置為 45 度。

濾波器優(yōu)先選擇無(wú)源濾波器。

濾波器開(kāi)環(huán)增益和閉環(huán)增益以及相位噪聲圖之間的關(guān)系。閉環(huán)增益的轉(zhuǎn)折頻率就是環(huán)路帶寬。相位噪聲圖上,該點(diǎn)對(duì)應(yīng)于相位噪聲曲線的轉(zhuǎn)折頻率。如果設(shè)計(jì)的鎖相環(huán)噪聲太大,就會(huì)出現(xiàn)頻譜分析儀上看到的轉(zhuǎn)折頻率大于所設(shè)定的環(huán)路帶寬。

5環(huán)路濾波器采用有源濾波器還是無(wú)源濾波器?

有源濾波器因?yàn)椴捎?a href="http://www.asorrir.com/tags/放大器/" target="_blank">放大器而引入噪聲,所以采用有源濾波器的 PLL 產(chǎn)生的頻率的相位噪聲性能會(huì)比采用無(wú)源濾波器的 PLL 輸出差。因此在設(shè)計(jì)中我們盡量選用無(wú)源濾波器。其中三階無(wú)源濾波器是最常用的一種結(jié)構(gòu)。PLL 頻率合成器的電荷泵電壓 Vp 一般取 5V 或者稍高,電荷泵電流通過(guò)環(huán)路濾波器積分后的最大控制電壓低于 Vp 或者接近 Vp。

如果VCO/VCXO 的控制電壓在此范圍之內(nèi),無(wú)源濾波器完全能夠勝任;如果VCO/VCXO 的控制電壓超出了 Vp,或者非常接近 Vp 的時(shí)候,就需要用有源濾波器。在對(duì)環(huán)路誤差信號(hào)進(jìn)行濾波的同時(shí),也提供一定的增益,從而調(diào)整VCO/VCXO控制電壓到合適的范圍。

那么如何選擇有源濾波器的放大器呢?這類應(yīng)用主要關(guān)心一下的技術(shù)指標(biāo):

低失調(diào)電壓(Low Offset Voltage) [通常小于 500uV]

低偏流(Low Bias Current) [通常小于 50pA]

如果是單電源供電,需要考慮使用軌到軌(Rail-to-Rail)輸出型放大器。

6PLL 對(duì)于 VCO 有什么要求?如何設(shè)計(jì) VCO 輸出功率分配器?

選擇 VCO 時(shí),盡量選擇 VCO 的輸出頻率對(duì)應(yīng)的控制電壓在可用調(diào)諧電壓范圍的中點(diǎn)。選用低控制電壓的 VCO 可以簡(jiǎn)化 PLL 設(shè)計(jì)。

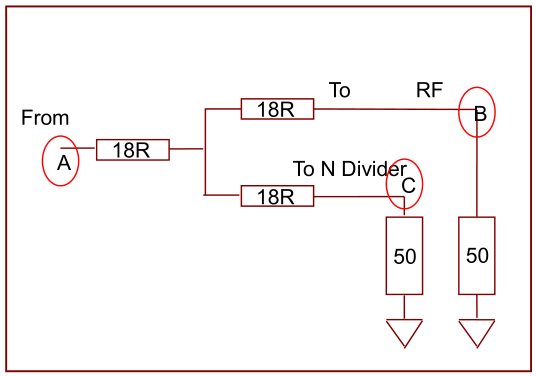

VCO 的輸出通過(guò)一個(gè)簡(jiǎn)單的電阻分配網(wǎng)絡(luò)來(lái)完成功率分配。從 VCO 的輸出看到電阻網(wǎng)絡(luò)的阻抗為 18+(18+50)//(18+50)=52ohm。形成與 VCO 的輸出阻抗匹配。下圖中 ABC 三點(diǎn)功率關(guān)系。B,C 點(diǎn)的功率比 A 點(diǎn)小 6dB。

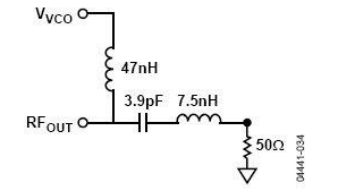

如下圖是 ADF4360-7 輸出頻率在 850MHz~950MHz 時(shí)的輸出匹配電路,注意該例是匹配到 50 歐的負(fù)載。如果負(fù)載是 75 歐,那么匹配電路無(wú)需改動(dòng),ADF4360-7 的輸出級(jí)為電流源,負(fù)載值的小變動(dòng)不會(huì)造成很大的影響,但要注意差分輸出端的負(fù)載需相等。

7如何設(shè)置電荷泵的極性?

在下列情況下,電荷泵的極性為正。

環(huán)路濾波器為無(wú)源濾波器,VCO 的控制靈敏度為正(即,隨著控制電壓的升高,輸出頻率增大)。

在下列情況下,電荷泵的極性為負(fù)。

環(huán)路濾波器為有源濾波器,并且放大環(huán)節(jié)為反相放大;VCO 的控制靈敏度為正。

環(huán)路濾波器為無(wú)源濾波器,VCO 的控制靈敏度為負(fù)。

PLL分頻應(yīng)用,濾波器為無(wú)源型。即參考信號(hào)直接 RF 反饋分頻輸入端,VCO 反饋到參考輸入的情況。

8鎖定指示電路如何設(shè)計(jì)?

PLL 鎖定指示分為模擬鎖定指示和數(shù)字鎖定指示兩種。

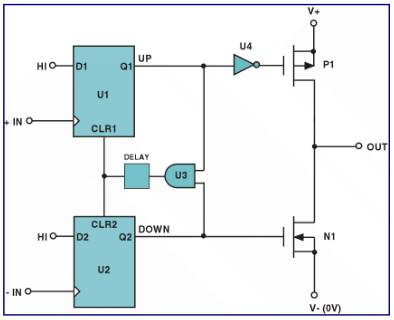

鑒相器和電荷泵原理圖

數(shù)字鎖定指示:

當(dāng) PFD 的輸入端連續(xù)檢測(cè)到相位誤差小于 15ns 的次數(shù)為 3(5)次,那么 PLL 就會(huì)給出數(shù)字鎖定指示。

數(shù)字鎖定指示的工作頻率范圍:通常為 5kHz~50MHz。在更低的 PFD 頻率上,漏電流會(huì)觸發(fā)鎖定指示電路;在更高的頻率上,15ns 的時(shí)間裕度不再適合。在數(shù)字鎖定指示的工作頻段范圍之外,推薦使用模擬鎖定指示。

模擬鎖定指示:

對(duì)電荷泵輸入端的 Up 脈沖和 Down 脈沖進(jìn)行異或處理后得出的脈沖串。所以當(dāng)鎖定時(shí),鎖定指示電路的輸出為帶窄負(fù)脈沖串的高電平信號(hào)。圖為一個(gè)典型的模擬鎖定指示輸出(MUXOUT 輸出端單獨(dú)加上拉電阻的情況)。

模擬鎖定指示的輸出級(jí)為 N 溝道開(kāi)漏結(jié)構(gòu),需要外接上拉電阻,通常為 10KOhm~160kohm。我們可以通過(guò)一個(gè)積分電路(低通濾波器)得到一個(gè)平坦的高電平輸出,如圖所是的藍(lán)色框電路。

誤鎖定的一個(gè)條件:

參考信號(hào)REFIN信號(hào)丟失。當(dāng)REFIN信號(hào)與PLL頻合器斷開(kāi)連接時(shí),PLL顯然會(huì)失鎖;然而,ADF41xx 系列的 PLL,其數(shù)字鎖定指示用 REFIN 時(shí)鐘來(lái)檢查是否鎖定,如果 PLL 先前已經(jīng)鎖定,REFIN 時(shí)鐘突然丟失,PLL 會(huì)繼續(xù)顯示鎖定狀態(tài)。解決方法是使用模擬鎖定指示。

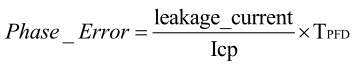

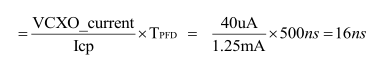

當(dāng) VCXO 代替 VCO 時(shí),PLL 常常失鎖的原因。以 ADF4001 為例說(shuō)明。VCXO 的輸入阻抗通常較小(相對(duì)于 VCO 而言),大約為 100kohm。這樣 VCXO 需要的電流必須由 PLL 來(lái)提供。PFD=2MHz, Icp=1.25mA,Vtune=4V,VCXO 輸入阻抗=100kohm,VCXO 控制口電流=4/100k=40uA。在 PFD 輸入端,用于抵消 VCXO 的輸入電流而需要的靜態(tài)相位誤差

16ns》15ns,所以,數(shù)字鎖定指示為低電平。

解決方法1,使用模擬鎖定指示。

解決方法2,使用更高的電荷泵電流來(lái)減小靜態(tài)相位誤差。增大環(huán)路濾波器電容,使放電變緩。

9PLL 對(duì)射頻輸入信號(hào)有什么要求?

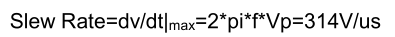

頻率指標(biāo):可以工作在低于最小的射頻輸入信號(hào)頻率上,條件是 RF 信號(hào)的 Slew Rate 滿足要求。

例如,ADF4106 數(shù)據(jù)手冊(cè)規(guī)定最小射頻輸入信號(hào) 500MHz,功率為-10dBm,這相應(yīng)于峰峰值為200mV,slew rate=314V/us。如果您的輸入信號(hào)頻率低于 500MHz,但功率滿足要求,并且slew rate 大于 314V/us,那么 ADF4106 同樣能夠正常工作。通常 LVDS 驅(qū)動(dòng)器的轉(zhuǎn)換速率可以很容易達(dá)到 1000V/us。

10PLL 芯片對(duì)電源的要求有哪些?

要求 PLL 電源和電荷泵電源具有良好的退耦,相比之下,電荷泵的電源具有更加嚴(yán)格的要求。具體實(shí)現(xiàn)如下:

在電源引腳出依次放置 0.1uF,0.01uF,100pF 的電容。最大限度濾除電源線上的干擾。大電容的等效串聯(lián)電阻往往較大,而且對(duì)高頻噪聲的濾波效果較差,高頻噪聲的抑制需要用小容值的電容。下圖可以看到,隨著頻率的升高,經(jīng)過(guò)一定的轉(zhuǎn)折頻率后,電容開(kāi)始呈現(xiàn)電感的特性。不同的電容值,其轉(zhuǎn)折頻率往往不同,電容越大,轉(zhuǎn)折頻率越低,其濾除高頻信號(hào)的能力越差。

另外在電源線上串聯(lián)一個(gè)小電阻(18ohm)也是隔離噪聲的一種常用方法。

11集成VCO 的ADF4360-x ,其中心頻率如何設(shè)定?

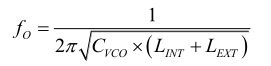

VCO 的中心頻率由下列三個(gè)因素決定。

1)VCO 的電容 C VCO

2)由芯片內(nèi)部 Bond Wires 引入的電感 L BW

3)外置電感 L EXT 。即

其中前2項(xiàng)由器件決定,這樣只要給定一個(gè)外置電感,就可以得到VCO的輸出 中心頻率。VCO的控制靈敏度在相應(yīng)的數(shù)據(jù)手冊(cè)上給出。作為一個(gè)例子,下圖給出了 ADF4360-7 的集成 VCO 特性。

電感的選取,最好選用高 Q 值的。Coilcraft 公司是不錯(cuò)的選擇。市面上常見(jiàn)的電感基本在 1nH以上。更小的電感可以用 PCB 導(dǎo)線制作。這里給出一個(gè)計(jì)算 PCB 引線電感的簡(jiǎn)單公式,如下圖所示。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435905 -

接口

+關(guān)注

關(guān)注

33文章

8932瀏覽量

153182 -

pll

+關(guān)注

關(guān)注

6文章

880瀏覽量

136025

原文標(biāo)題:接下來(lái)是答疑環(huán)節(jié)——常見(jiàn)PLL芯片接口問(wèn)題11則

文章出處:【微信號(hào):analog_devices,微信公眾號(hào):analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ESD防護(hù)設(shè)計(jì)中的10個(gè)常見(jiàn)誤區(qū),你中招了嗎?

RCA接口的常見(jiàn)故障及解決方法

示波器接口和連接方式 示波器的常見(jiàn)故障及解決方法

使用LMK04821芯片的單PLL模式,輸出的時(shí)鐘頻率基本上是對(duì)的,但PLL2不能lock,為什么?

對(duì)電動(dòng)汽車電池11大誤解的解答

鎖相環(huán)PLL的常見(jiàn)故障及解決方案

常見(jiàn)視頻接口的優(yōu)勢(shì)與劣勢(shì)

接口芯片的譯碼電路設(shè)計(jì)一般采用什么方法

接口芯片的編程模型方法是什么

盤點(diǎn)那些常見(jiàn)音視頻接口

PLL1705/PLL1706雙通道PLL多時(shí)鐘發(fā)生器數(shù)據(jù)表

PLL是什么意思

紫光同創(chuàng)——PLL IP 的使用(Logos2)

HDMI接口和VGA接口有什么區(qū)別

LVDS用法:LVDS RX 時(shí)鐘選擇 LVDS的PLL的復(fù)位信號(hào)的處理

PLL芯片接口方面最常見(jiàn)的11個(gè)問(wèn)題

PLL芯片接口方面最常見(jiàn)的11個(gè)問(wèn)題

評(píng)論