注意示波器的探頭和示波器本身的帶寬能夠滿足測(cè)試要求。

測(cè)試點(diǎn)的選擇要注意選到盡量靠近信號(hào)的接受端。由于 DDR 信令比較復(fù)雜,因此為了能快速測(cè)試、調(diào)試和解決信號(hào)上的問(wèn)題,我們希望能簡(jiǎn)單地分離讀/寫比特。

此時(shí),最常用的是通過(guò)眼圖分析來(lái)幫助檢查 DDR 信號(hào)是否滿足電壓、定時(shí)和抖動(dòng)方面的要求。觸發(fā)模式的設(shè)置有幾種,首先可以利用前導(dǎo)寬度觸發(fā)器分離讀/寫信號(hào)。

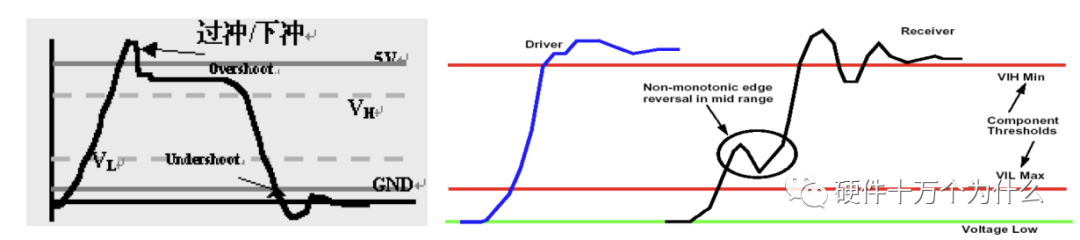

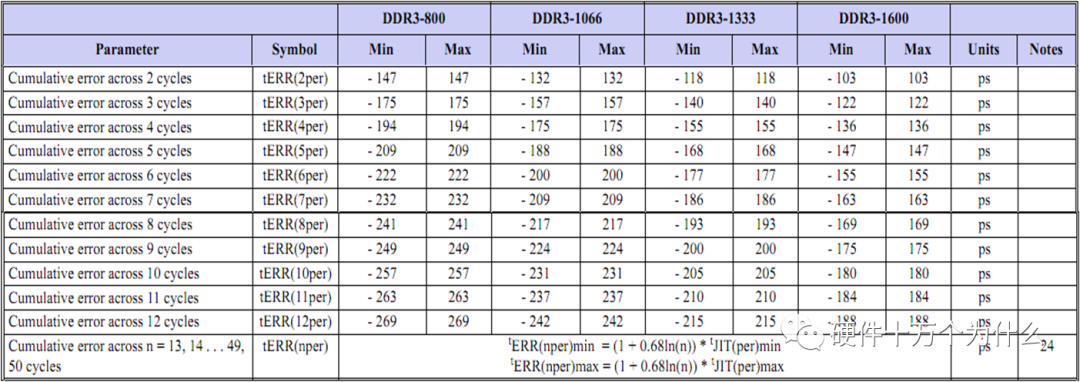

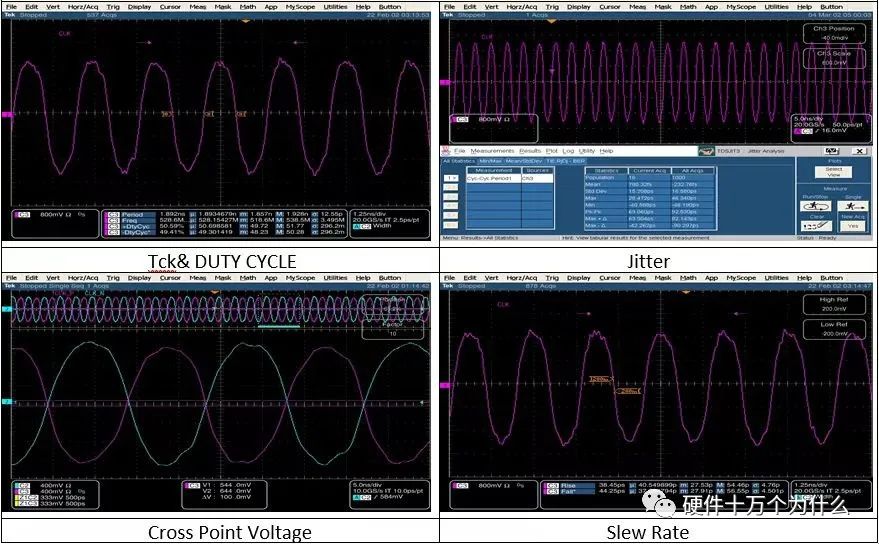

根據(jù) JEDEC 規(guī)范,讀前導(dǎo)的寬度為 0.9 到 1.1 個(gè)時(shí)鐘周期,而寫前導(dǎo)的寬度規(guī)定為大于 0.35 個(gè)時(shí)鐘周期,沒有上限。第二種觸發(fā)方式是利用更大的信號(hào)幅度觸發(fā)方法分離讀/寫信號(hào)。通常,讀/寫信號(hào)的信號(hào)幅度是不同的,因此我們可以通過(guò)在更大的信號(hào)幅度上觸發(fā)示波器來(lái)實(shí)現(xiàn)兩者的分離。測(cè)試中要注意信號(hào)的幅度,時(shí)鐘的頻率,差分時(shí)鐘的交叉點(diǎn),上升沿是否單調(diào),過(guò)沖等。

2、DDR3中的幾種采樣關(guān)系

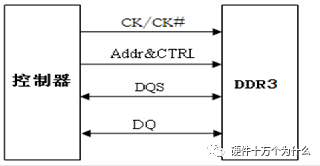

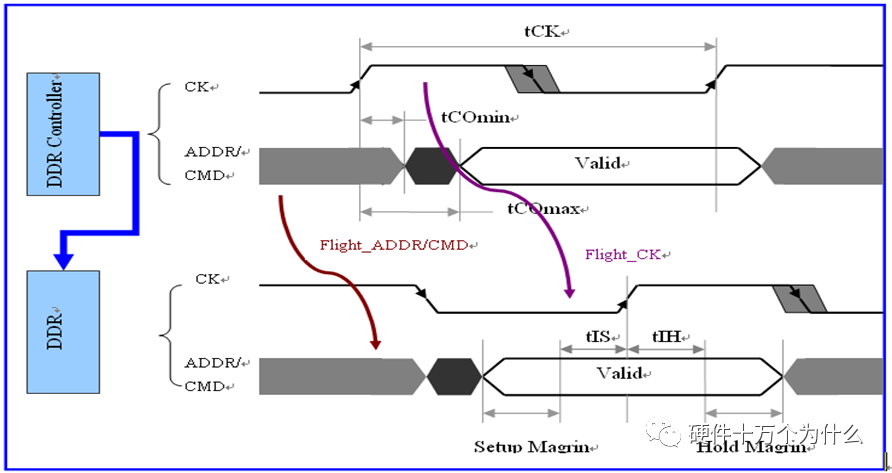

地址控制信號(hào)ADDR/CMD與系統(tǒng)時(shí)鐘CK的時(shí)序關(guān)系

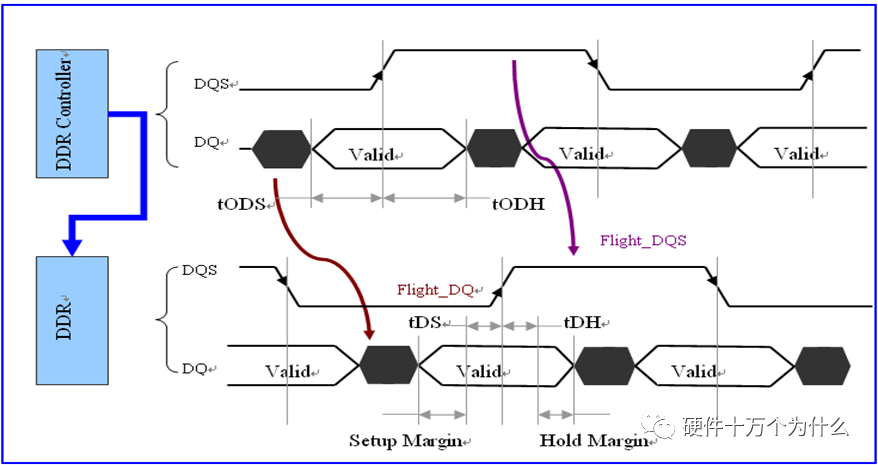

數(shù)據(jù)信號(hào)DQ/DM與數(shù)據(jù)選通信號(hào)DQS的時(shí)序關(guān)系

寫周期

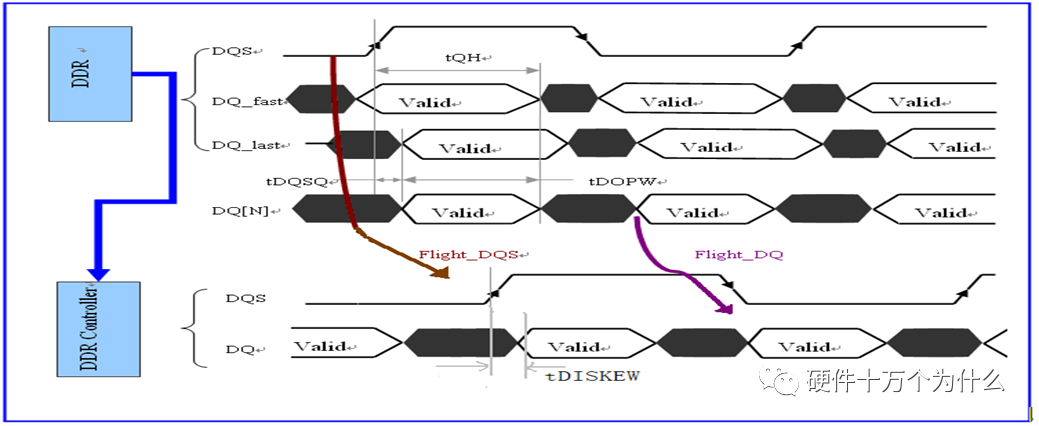

讀周期

幾種時(shí)序關(guān)系,后續(xù)會(huì)做詳解

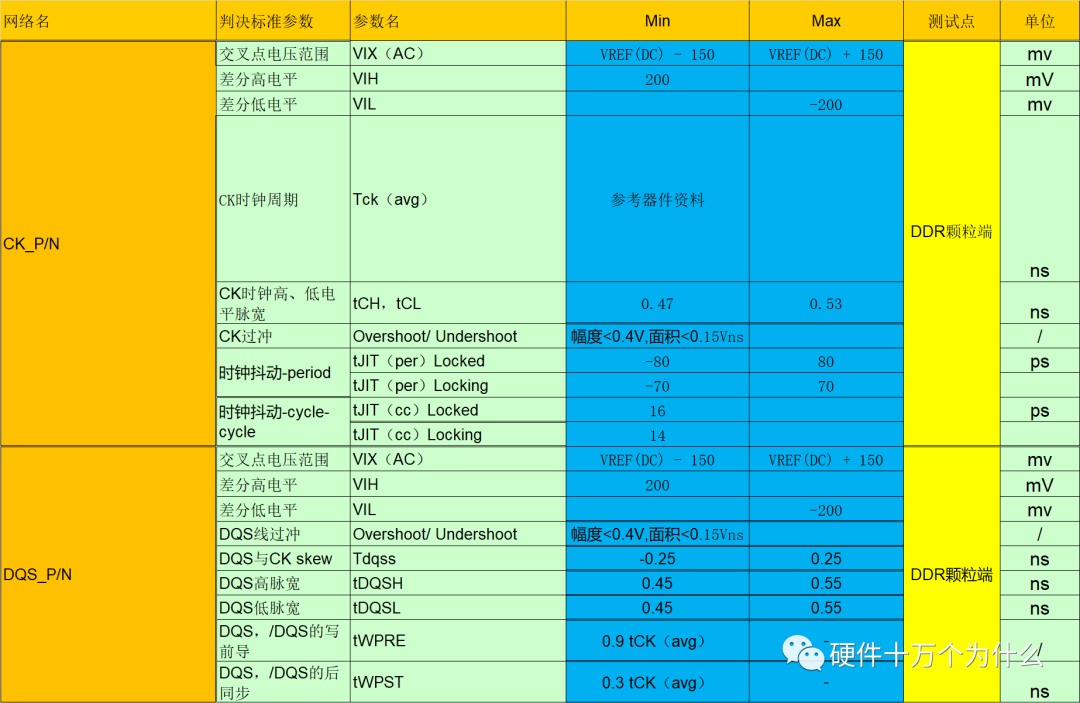

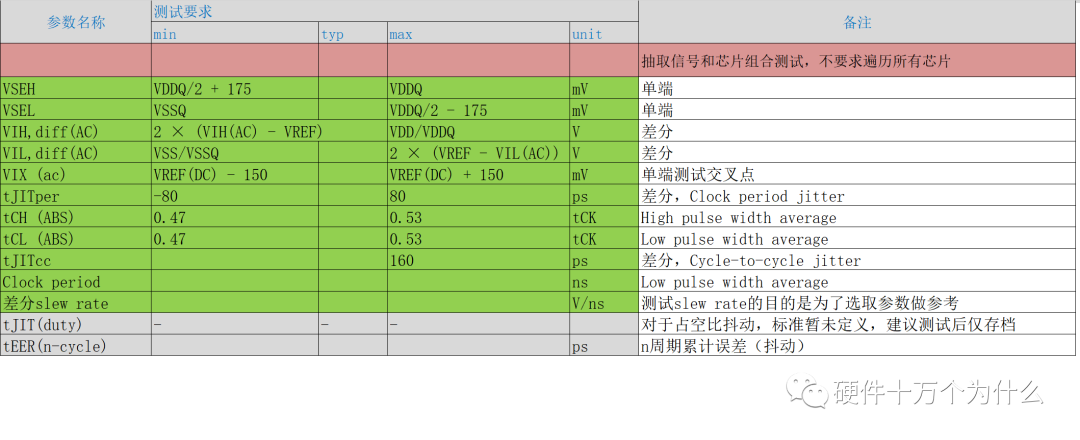

3、DDR時(shí)鐘信號(hào)(CK、DQS)測(cè)試:

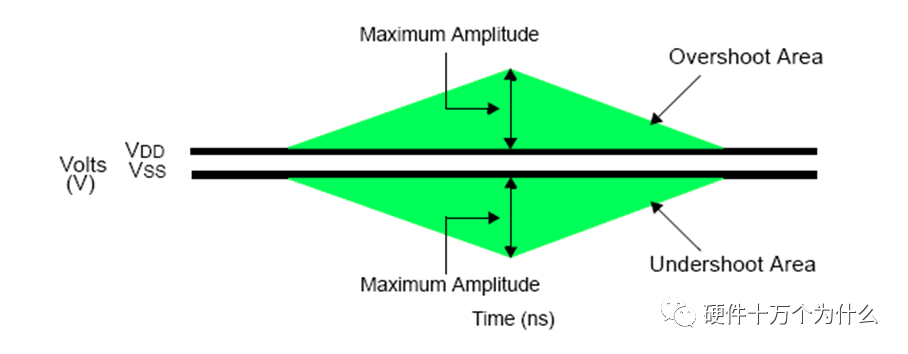

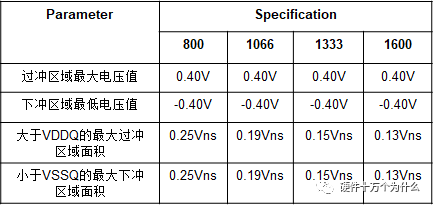

時(shí)鐘信號(hào)過(guò)沖要求

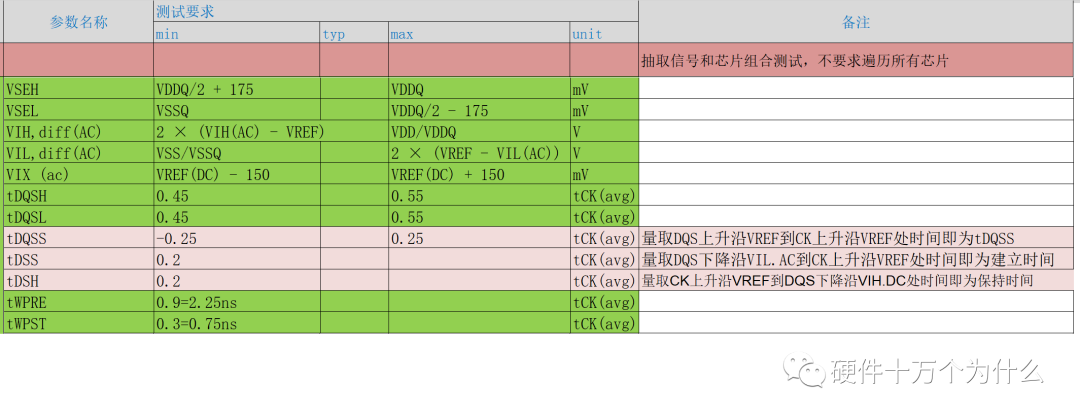

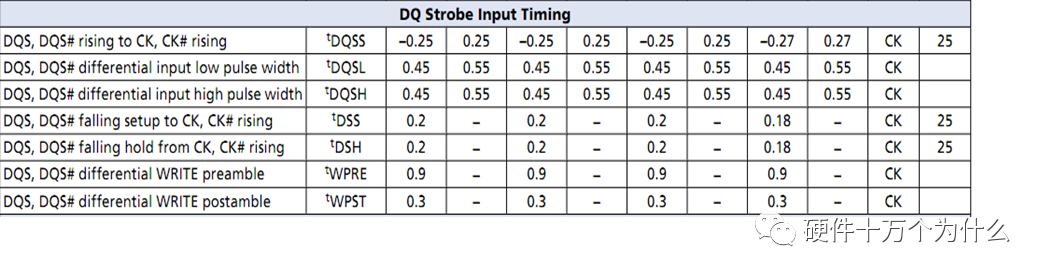

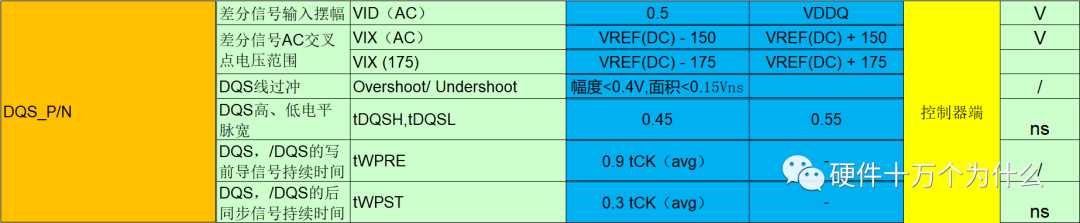

寫方向

CK

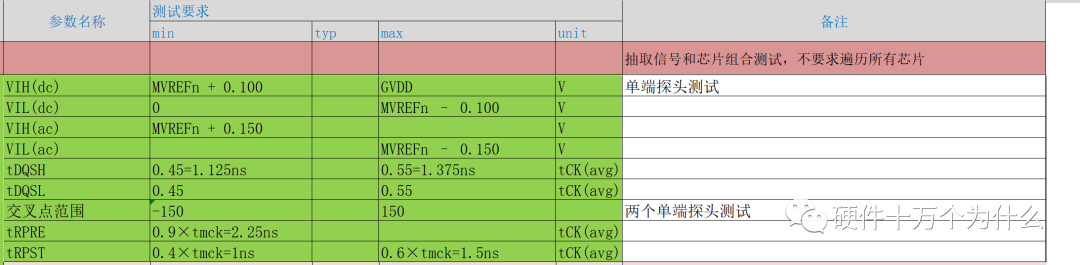

DQS

讀方向

審核編輯:湯梓紅

-

示波器

+關(guān)注

關(guān)注

113文章

6535瀏覽量

188190 -

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56023 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66371

原文標(biāo)題:【硬件的單元測(cè)試_6】DDR3信號(hào)測(cè)試1

文章出處:【微信號(hào):Hardware_10W,微信公眾號(hào):硬件十萬(wàn)個(gè)為什么】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

DDR3 SDRAM配置教程

5V 輸入、10A負(fù)載DDR3/DDR4通用電源解決方案

泰克公司推出市面上性能最高的DDR3協(xié)議測(cè)試解決方案

針對(duì)DDR2-800和DDR3的PCB信號(hào)完整性設(shè)計(jì)

針對(duì)DDR2-800和DDR3的PCB信號(hào)完整性設(shè)計(jì)

ddr4和ddr3內(nèi)存的區(qū)別,可以通用嗎

模擬DDR3的地址信號(hào)與時(shí)鐘信號(hào)資料下載

Virtex7上DDR3的測(cè)試例程

基于AXI總線的DDR3讀寫測(cè)試

基于FPGA的DDR3讀寫測(cè)試

完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表

完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表

完整DDR,DDR2,DDR3 和LPDDR3 存儲(chǔ)器電源解決方案同步降壓控制器數(shù)據(jù)表

DDR3信號(hào)測(cè)試解決方案

DDR3信號(hào)測(cè)試解決方案

評(píng)論