無論身處哪條賽道,為客戶提供先進的、具有差異化的產品,是所有芯片設計團隊的共同目標。突破先進工藝節點設計的功耗、性能和面積(PPA)極限正是開發者們努力的方向之一。

大多數芯片設計團隊在這一環節使用新思科技的數字設計產品系列,即Design Compiler或Fusion Compiler解決方案。團隊通常想要利用時序重定、多位寄存器合并、高級數據路徑優化等所有可用的復雜功能,來實現更出色的結果質量(QoR)。對客戶來說,能夠快速建立一個可預測的芯片設計周期可以讓他們更早地上市新產品,這將是他們跑贏市場的一個關鍵性競爭優勢。

此外,RTL代碼經常發生預期之外的功能性變更,甚至可能到最后一刻都還在變,對這些變更做出及時響應對開發者來說非常重要。此類變更通常使用功能工程變更命令(ECO)來實現,此時的RTL已凍結,且綜合與布局布線都已經處于后期階段。無論是為了修復功能驗證漏洞,還是要增加重要新功能,ECO都必不可少。

相比把所有代碼從頭再跑一遍,ECO所需的時間和成本較少,因此成為首選方案。但ECO往往出現在設計流程后期,而且可能涉及到相當復雜的工作,這意味著ECO可能會對時序邏輯、狀態機、時鐘復位路徑等產生影響。正因如此,開發者們對自動化工具的需求更加明確。

什么是功能ECO?

功能ECO是指將邏輯直接插入與RTL中變更相對應的門級網表的過程。提供此功能的自動化解決方案應該能夠比較原有設計和經過ECO修改后設計中的受影響的邏輯錐,識別代表變更的最小邏輯門集合,然后對其生成補丁并確保補丁可在原布局布線網表中輕松應用。

ECO中包含多種實現方式,從在設計中添加或移除邏輯,到清理布線以確保信號完整性等細微變更。所有ECO都側重于盡可能加快產品上市速度,并最大限度地降低修改和計劃風險。處理ECO的工作不僅壓力大、時間長,而且還充滿不確定性。

考慮到ECO生成過程中的巨大時間壓力,務必要做到以下幾點:

縮短周轉時間:盡快生成準確的補丁

盡量減少迭代:補丁應功能正確且兼顧時序,從而盡可能減少對已實現設計的干擾

為什么許多功能ECO解決方案 無此效果?

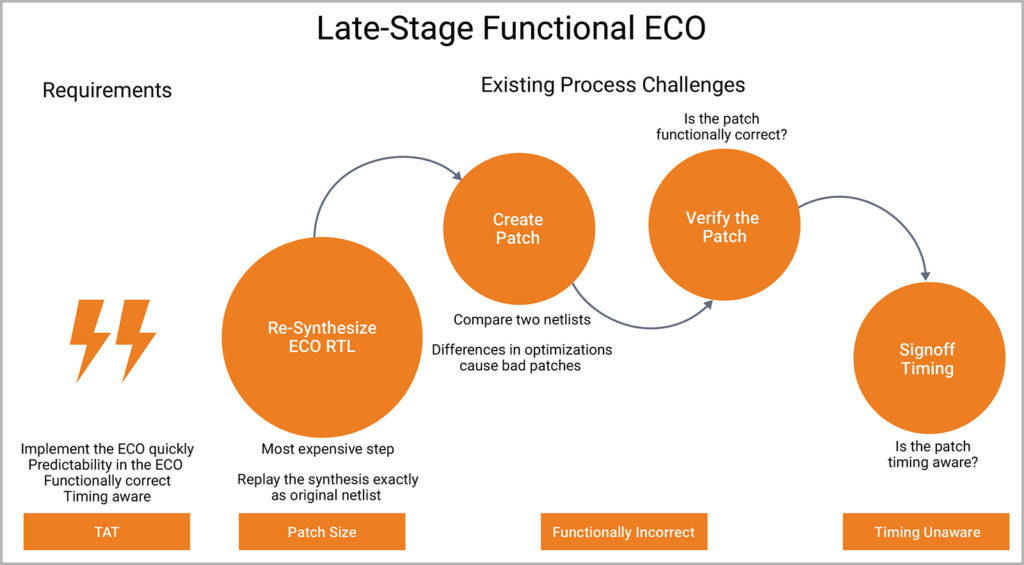

結合上述要求,我們來看一下市場上現有功能ECO解決方案的局限性(圖1)。

▲圖1:市場上許多現有的功能ECO解決方案都存在局限性,影響質量和周轉時間。

第一代功能ECO解決方案受制于基本流程局限性:全部都要遵循網表驅動型流程。這意味著,ECO創建過程只能比較兩個完全綜合的網表,即原網表與新綜合的ECO網表。在使用這些解決方案時,即使ECO實際上只涉及數行RTL代碼或幾個組合門,用戶也需要對經過ECO的分區進行完整重新綜合。如果該分區的完整綜合需要數天時間,這一步可能成本極高,而由于ECO實現時間非常緊張,設計團隊根本等不起。

第二個局限性在于,在ECO綜合階段,這些工具很多都嚴格要求重現綜合優化。換言之,這些解決方案要求ECO網表實現與原網表完全相同的優化。這是因為,在ECO綜合期間,ECO中包含的RTL變更可能會提示綜合工具選擇不同的優化路徑。例如,一些寄存器以前可能是常值寄存器,但在ECO之后,變成了非常值寄存器。一些寄存器合并策略可能有所不同,可能導致存在寄存器合并或寄存器復制步驟的不同。

在比較這樣兩個優化路徑不同的網表時,工具可能很難正確識別邏輯錐之間的真正差異,因而無法生成功能正確或最優的補丁。最終,這會給ECO綜合步驟帶來不必要的限制。此外,因為上述原因,開發者還需要完成大量手動或自定義設置來重現綜合,以便ECO工具能夠分析這兩個網表并創建最小的補丁。

擔心在ECO流程后期面臨這些復雜因素,開發者通常會減少諸如打平層次、時序邏輯優化和反相驅動等綜合優化操作,以便縮短ECO周期。ECO基本上決定了團隊如何執行綜合,而這種情況是可以避免的。

總的來說,在從ECO RTL就緒到ECO完成的過程中,許多現有的自動化解決方案存在以下局限性:

僅支持網表流程,因此用戶必須先執行ECO綜合步驟,才能開始創建補丁。而分區綜合有時可能需要數天時間,這顯著延長了周轉時間(TAT)。

引入限制。ECO綜合必須與原有綜合完全相同,從而盡可能減少兩個網表之間的優化差異。另外,重現綜合需要完成大量自定義設置,這又進一步延長了周轉時間。

上述兩個步驟只要出現任何差錯,工具生成的補丁就會錯誤低效,進而需要多次手動迭代來修正補丁。

最后,由于擔心面對上述種種復雜因素,開發者會選擇禁用綜合優化,而犧牲結果質量。

能夠一次成功的ECO解決方案

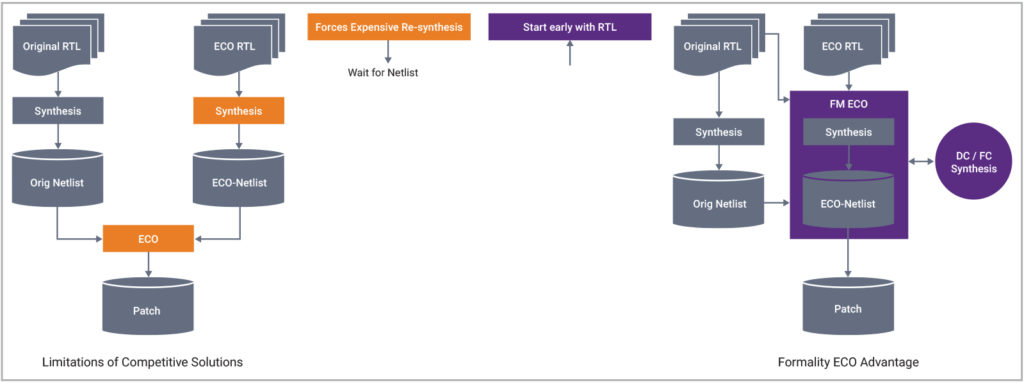

能夠一次成功的ECO解決方案在市場上還是存在的,該解決方案用時更短,質量也更好,那就是新思科技Formality ECO解決方案。 新思科技的功能ECO解決方案,Formality ECO會在ECO RTL就緒后,立即開始ECO生成過程。在后期ECO過程中,這為開發者提供了有利的開端,并為他們節省了寶貴的時間(圖2)。

▲圖2:左圖說明了市場上其他功能ECO解決方案的局限性,右圖則凸顯了新思科技Formality ECO解決方案如何以更優質量、更快周轉時間讓ECO一次成功。

該解決方案突破性地利用Formality等效性檢查技術和Design Compiler或Fusion Compiler解決方案的內部編譯技術。

首先,Formality ECO解決方案會比較原RTL和ECO RTL,利用結構分析功能來識別并分隔代表ECO的變更區域。“find_equivalent_net”功能可以越過模塊和觸發器邊界并一直到網絡邊界進行遍歷和局部分析。該方法有助于分隔在ECO RTL中捕捉變更所需的最小ECO區域集合。

然后,這些區域會發送至Design Compiler或Fusion Compiler解決方案,由后者根據指示執行“目標綜合”。從本質上來說,這屬于具有ECO意識的智能編譯,它僅對變更區域進行綜合,而無需執行完整的ECO綜合。該解決方案會準確識別目標綜合,并僅對模塊內部受ECO影響的區域進行綜合。此外,綜合是在整體設計約束下執行的智能編譯。該綜合支持所有必要的優化,因而不會影響結果質量。這樣一來,該ECO生成可確保功能正確。

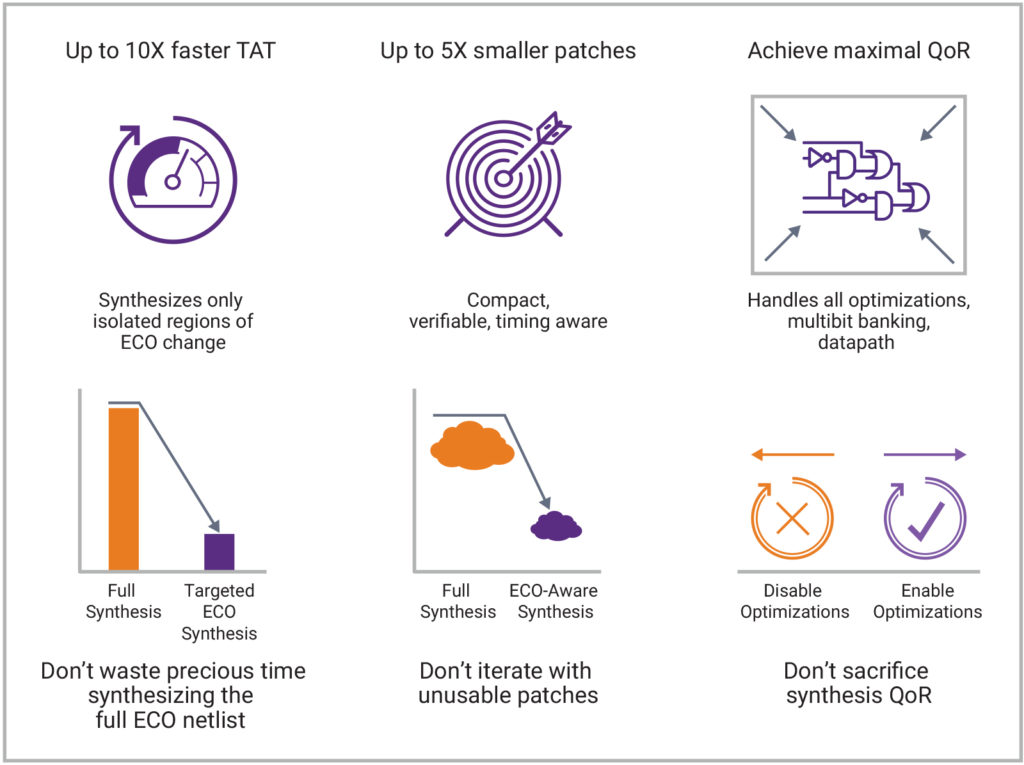

實踐表明,Formality ECO技術可將周轉時間縮短到原來的十分之一,使補丁最多縮小到原來的五分之一,并能夠為廣泛應用領域中的設計大幅提高結果質量(圖3)。

▲圖3:新思科技Formality ECO解決方案具有諸多優勢,能夠實現更高質量的ECO。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5415瀏覽量

123215 -

RTL

+關注

關注

1文章

388瀏覽量

60621 -

ECO

+關注

關注

0文章

52瀏覽量

15106

原文標題:ECO一次成功很難嗎?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

V6 FPGA可以ECO功能嗎?

多功能步進電機驅動器為許多應用提供了經濟高效的解決方案

汽車eco模式使用技巧_eco模式真能省油嗎

eco模式的好處以及壞處_eco模式會引起積碳是真的嗎

一場關于自動化ECO解決方案的在線研討會

空調遙控器上的eco是什么意思

詳解Xilinx FPGA的ECO功能

新思科技推出突破性ECO解決方案PrimeClosure,助力設計效率提升10倍

什么是DFT友好的功能ECO呢?

什么是ECO?ECO的應用場景和實現流程

解析什么是DFT友好的功能ECO?

分享一種大型SOC設計中功能ECO加速的解決方案

什么是功能ECO?為什么許多功能ECO解決方案無此效果?

什么是功能ECO?為什么許多功能ECO解決方案無此效果?

評論