在設計PCB時,需要考慮的一個最基本的問題就是實現電路要求的功能需要多少個布線層、接地平面和電源平面,而印制電路板的布線層、接地平面和電源平面的層數的確定與電路功能、信號完整性、EMI、EMC、制造成本等要求有關。 對于大多數的設計,PCB的性能要求、目標成本、制造技術和系統的復雜程度等因素存在許多相互沖突的要求,PCB的疊層設計通常是在考慮各方面的因素后折中決定的。高速數字電路和射須電路通常采用多層板設計。 下面列出了層疊設計要注意的8個原則。

1

分層

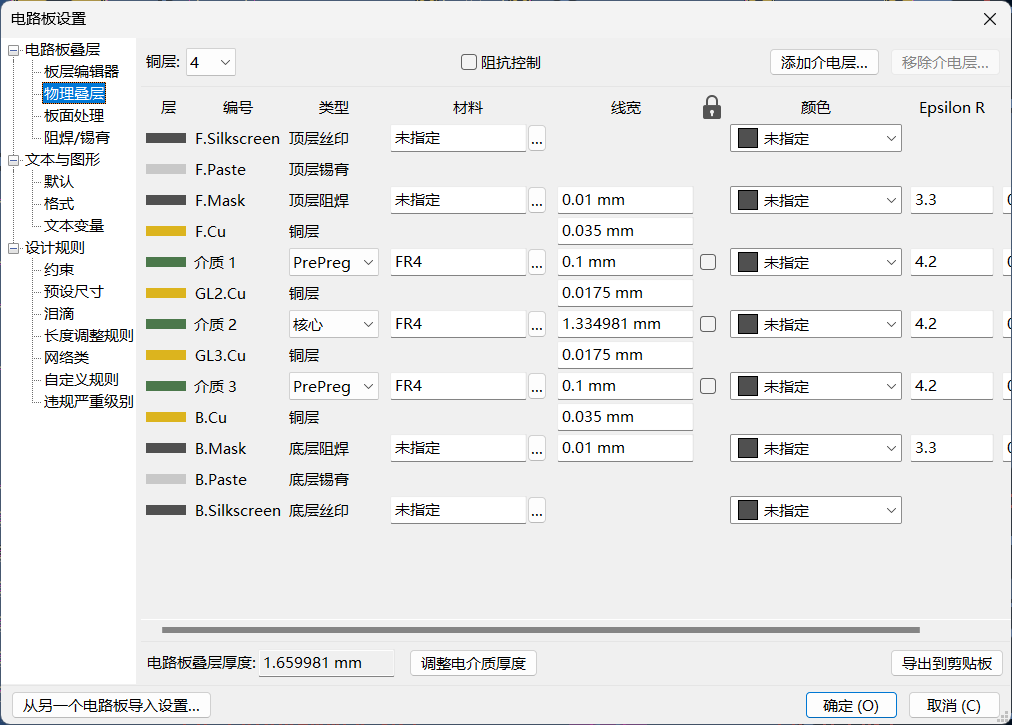

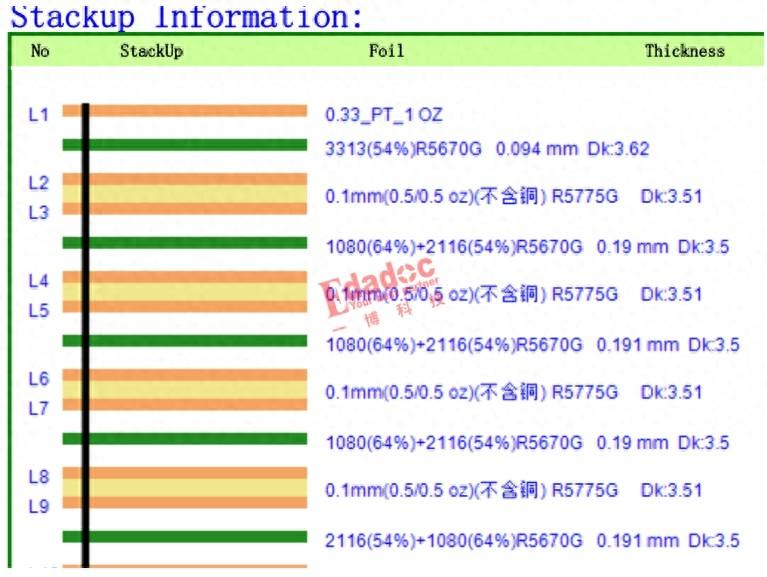

在多層PCB中,通常包含有信號層(S)、電源(P)平面和接地(GND)平面。電源平面和接地平面通常是沒有分割的實體平面,它們將為相鄰信號走線的電流提供一個好的低阻抗的電流返回路徑。 信號層大部分位于這些電源或地參考平面層之間,構成對稱帶狀線或非對稱帶狀線。多層PCB的頂層和底層通常用于放置元器件和少量走線,這些信號走線要求不能太長,以減少走線產生的直接輻射。

2

確定單電源參考平面

使用去耦電容是解決電源完整性的一個重要措施。去耦電容只能放置在PCB的頂層和底層。去耦電容的走線、焊盤,以及過孔將嚴重影響去耦電容的效果,這就要求設計時必須考慮連接去耦電容的走線應盡量短而寬,連接到過孔的導線也應盡量短。例如,在一個高速數字電路中,可以將去耦電容放置在PCB的頂層,將第2層分配給高速數字電路(如處理器)作為電源層,將第3層作為信號層,將第4層設置成高速數字電路地。 此外,要盡量保證由同一個高速數字器件所驅動的信號走線以同樣的電源層作為參考平面,而且此電源層為高速數字器件的供電電源層。

3

確定多電源參考平面

多電源參考平面將被分割成幾個電壓不同的實體區域。如果緊靠多電源層的是信號層,那么其附近的信號層上的信號電流將會遭遇不理想的返回路徑,使返回路徑上出現縫隙。 對于高速數字信號,這種不合理的返回路徑設計可能會帶來嚴重的問題,所以要求高速數字信號布線應該遠離多電源參考平面。

4

確定多個接地參考平面

多個接地參考平面(接地層)可以提供一個好的低阻抗的電流返回路徑,可以減小共模EMl。接地平面和電源平面應該緊密耦合,信號層也應該和鄰近的參考平面緊密耦合。減少層與層之間的介質厚度可以達到這個目的。

5

合理設計布線組合

一個信號路徑所跨越的兩個層稱為一個“布線組合”。最好的布線組合設計是避免返回電流從一個參考平面流到另一個參考平面,而是從一個參考平面的一個點(面)流到另一個點(面)。而為了完成復雜的布線,走線的層間轉換是不可避免的。在信號層間轉換時,要保證返回電流可以順利地從一個參考平面流到另一個參考平面。在一個設計中,把鄰近層作為一個布線組合是合理的。 如果一個信號路徑需要跨越多個層,將其作為一個布線組合通常不是合理的設計,因為一個經過多層的路徑對于返回電流而言是不通暢的。雖然可以通過在過孔附近放置去耦電容或者減小參考平面間的介質厚度等來減小地彈,但也非一個好的設計。

6

設定布線方向

在同一信號層上,應保證大多數布線的方向是一致的,同時應與相鄰信號層的布線方向正交。例如,可以將一個信號層的布線方向設為"Y軸”走向,而將另一個相鄰的信號層布線方向設為“X軸”走向。

7

采用偶數層結構

從所設計的PCB疊層可以發現,經典的疊層設計幾乎全部是偶數層的,而不是奇數層的,這種現象是由多種因素造成的。 從印制電路板的制造工藝可以了解到,電路板中的所有導電層救在芯層上,芯層的材料一般是雙面覆板,當全面利用芯層時,印制電路板的導電層數就為偶數。 偶數層印制電路板具有成本優勢。由于少一層介質和覆銅,故奇數層印制電路板原材料的成本略低于偶數層的印制電路板的成本。但因為奇數層印制電路板需要在芯層結構工藝的基礎上增加非標準的層疊芯層黏合工藝,故造成奇數層印制電路板的加工成本明顯高于偶數層印制電路板。與普通芯層結構相比,在芯層結構外添加覆銅將會導致生產效率下降,生產周期延長。在層壓黏合以前,外面的芯層還需要附加的工藝處理,這增加了外層被劃傷和錯誤蝕刻的風險。增加的外層處理將會大幅度提高制造成本。 當印制電路板在多層電路黏合工藝后,其內層和外層在冷卻時,不同的層壓張力會使印制電路板上產生不同程度上的彎曲。而且隨著電路板厚度的增加,具有兩個不同結構的復合印制電路板彎曲的風險就越大。奇數層電路板容易彎曲,偶數層印制電路板可以避免電路板彎曲。 在設計時,如果出現了奇數層的疊層,可以采用下面的方法來增加層數。 如果設計印制電路板的電源層為偶數而信號層為奇數,則可采用增加信號層的方法。增加的信號層不會導致成本的增加,反而可以縮短加工時間、改善印制電路板質量。 如果設計印制電路板的電源層為奇數而信號層為偶數,則可采用增加電源層這種方法。而另一個簡單的方法是在不改變其他設置的情況下在層疊中間加一個接地層,即先按奇數層印制電路板布線,再在中間復制一個接地層。 在微波電路和混合介質(介質有不同介電常數)電路中,可以在接近印制電路板層疊中央增加一個空白信號層,這樣可以最小化層疊不平衡性。

8

成本考慮

在制造成本上,在具有相同的PCB面積的情況下,多層電路板的成本肯定比單層和雙層電路板高,而且層數越多,成本越高。但在考慮實現電路功能和電路板小型化,保證信號完整性、EMl、EMC等性能指標等因素時,應盡量使用多層電路板。綜合評價,多層電路板與單雙層電路板兩者的成本差異并不會比預期的高很多。

審核編輯 :李倩

-

電源

+關注

關注

185文章

18251瀏覽量

254875 -

pcb

+關注

關注

4349文章

23403瀏覽量

406415 -

印制電路板

+關注

關注

14文章

963瀏覽量

41500

原文標題:【技術園地】PCB疊層設計需要注意的那些事,你都做好了嗎?

文章出處:【微信號:江西省電子電路行業協會,微信公眾號:江西省電子電路行業協會】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

怎么設計ADS828E的高速PCB板,要注意哪些問題?

PCB 設計規則、層疊結構的導入/導出

0.4mm層疊封裝(PoP)封裝的PCB組裝指南,第二部分

0.5mm層疊封裝應用處理器的PCB組裝指南,第II部分

PCB GND設計原則和注意事項

使用THS3091有什么要注意的地方嗎?

PCB設計基本原則總結,工程師必看

秘密背后的秘密-高速PCB的層疊確認時,工廠為何不寫銅箔類型

PCB層疊設計要注意的8個原則

PCB層疊設計要注意的8個原則

評論