隨著FPGA的功能越來越強大,并且有SOC等異構(gòu)的架構(gòu)不斷演進(jìn),硬件設(shè)計也有更多的時鐘要求,例如:

A. PCIe 系統(tǒng)要求HSTL 100Mhz的時鐘;

B. DDR有推薦時鐘,7系列上常用200Mhz 差分時鐘;UltraScale和UltraScale Plus上常用300Mhz時鐘;

C. Zynq或者Zynq UltraScale,PS常用33.3333Mhz1.8V單端時鐘;

D. UltraScale接USB的話,常用26Mhz LVDS時鐘,SATA需要125Mhz或者150Mhz時鐘;

E. 收發(fā)器的頻率比較多,125Mhz、156.25Mhz、161.1328Mhz,148.5Mhz等等;

F. FPGA的PL有時候備一個SYSCLK,50Mhz,100Mhz或者200Mhz都比較常見,作為系統(tǒng)工作時鐘,有單端的,也有用差分的;

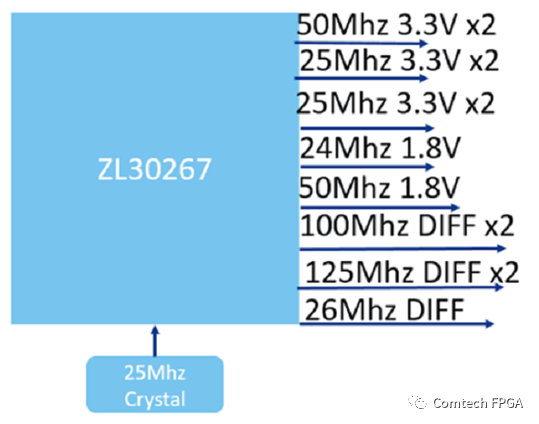

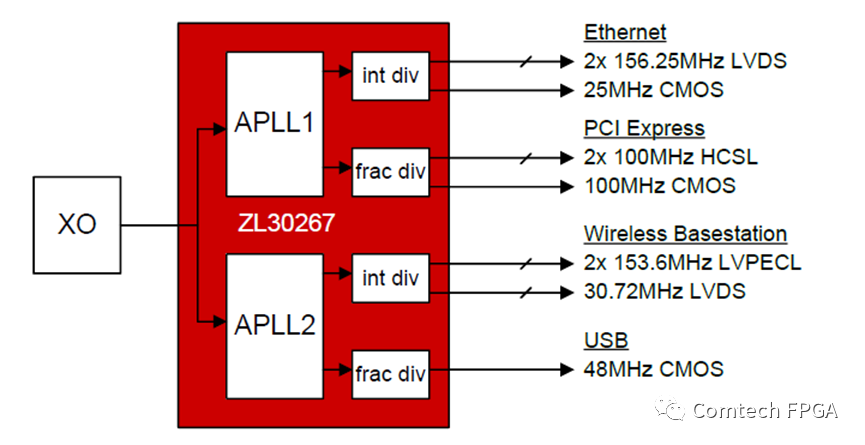

一個板子下來,3-6種時鐘需求常見,不同的頻率,不同的電平標(biāo)準(zhǔn)。硬件工程師做設(shè)計,不同板卡,各種設(shè)計混合在一塊,庫房有10多種晶振,時鐘驅(qū)動芯片,時鐘PLL芯片,琳瑯滿目。針對FPGA的設(shè)計,Microchip有一塊芯片,ZL30265/7,單芯片解決方案。

ZL30265/7概要介紹

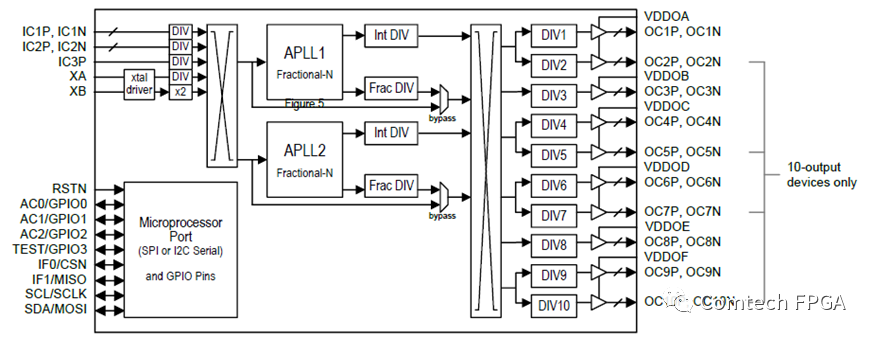

ZL30265/7內(nèi)部配置有任意倍數(shù)的乘法器以及兩個同時具有分?jǐn)?shù)和整數(shù)能力的模擬鎖相環(huán),可以生成4個獨立的頻率系列,進(jìn)一步的可以輸出多達(dá)6路或10路的任意頻點任意輸出類型的超低抖動的時鐘信號。ZL30265/7在輸入僅為一顆晶體的情況下,依靠其出色的性能,創(chuàng)建了完整的時鐘樹,替換了多個晶體晶振和外圍時序簡化了設(shè)計,降低了BOM成本,節(jié)省了PCB空間,并提高了設(shè)計的可靠性。

ZL30265/7的特性

A. 內(nèi)置兩個具有分?jǐn)?shù)分頻和整數(shù)分頻功能的APLL,構(gòu)成四個獨立的頻率族;

B. 四路輸入時鐘可以靈活配置,分別是:一個晶體/CMOS、兩個差分/CMOS、一個單端/CMOS;

C. 輸入頻率可以是9.72MHz至1.25GHz中的任意值(CMOS最大300MHz);

D. 每個APLL的四個輸入(IC1,IC2,IC3,XA)均有一個輸入監(jiān)視器,當(dāng)檢測到輸入出現(xiàn)異常時,支持自動或手動切換至其他輸入;切換方式包括GPIO Pin、寄存器、輸入監(jiān)視器;

E. 6路任意頻率、任意格式的輸出,輸出頻率為1Hz至1045MHz中的任意值;

F. 整數(shù)乘法器和除法器的輸出抖動低至0.17ps RMS(12kHz-20MHz);

G. 分?jǐn)?shù)分頻器的輸出抖動典型標(biāo)稱值<1ps RMS,實際應(yīng)用中大多數(shù)情況<0.5ps RMS;

H. 每個輸出都有一個獨立的分頻器,并且每個輸出均可配置為LVDS、LVPECL、HCSL、2xCMOS或HSTL;

I. 在2xCMOS模式下,P和N可以輸出不同的頻率(例如125MHz和25MHz),CMOS輸出電壓可調(diào),范圍是 1.5V至3.3V;

J. 各路時鐘輸出可以進(jìn)行精確校準(zhǔn),并且輸出相位可調(diào)整;

K. 各路時鐘輸出可以獨立的啟用或者禁用,并且支持glitch-less啟動和停止;

L. ZL30265/7內(nèi)部集成有EEPROM,可以存儲8組配置,上電時可以選擇其中一組自動配置;

N. 擴頻調(diào)制模式;

O. 生成符合PCIe 1、2、3、4、5的時鐘;

Q. 核心電源電壓有多種選項:僅2.5V、僅3.3V、1.8V+2.5V或1.8V+3.3V;

R. 封裝為8x8mm QFN56(0.5mm間距),節(jié)省PCB空間;

ZL30265/7的配置方式

ZL30265/7內(nèi)部集成有EEPROM,可以存儲8組不同的配置。EEPROM寫入配置數(shù)據(jù)后,每次RST時將會根據(jù)GPIO自動加載一組配置數(shù)據(jù);

寫EEPROM時的硬件連接:TEST=1,AC[2:0]=000, IF[1:0]=11

通訊方式:SPI

燒寫器:standard industry SPI EEPROMprogrammers,購買途徑也很方便,在淘寶就能買到,不到百元;

燒寫軟件:Microchip提供免費的GUI,可以按需求進(jìn)行配置,生成EEPROM IMAGE,然后用燒寫器燒錄;

案例集錦一:

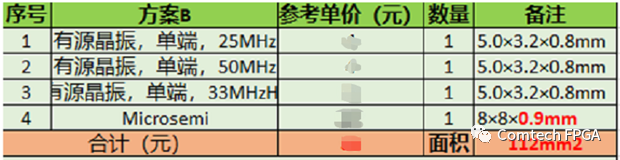

某客戶的產(chǎn)品最初用分立時鐘方案(方案A),后來用Microchip的ZL30267(方案B)進(jìn)行了優(yōu)化,并進(jìn)行了對比,得出兩個結(jié)論:

A. 方案B的BOM成本比方案A低大約30%;并且物料種類減少,方便采購備貨;

B. 方案B的PCB占用面積是方案A的一半;

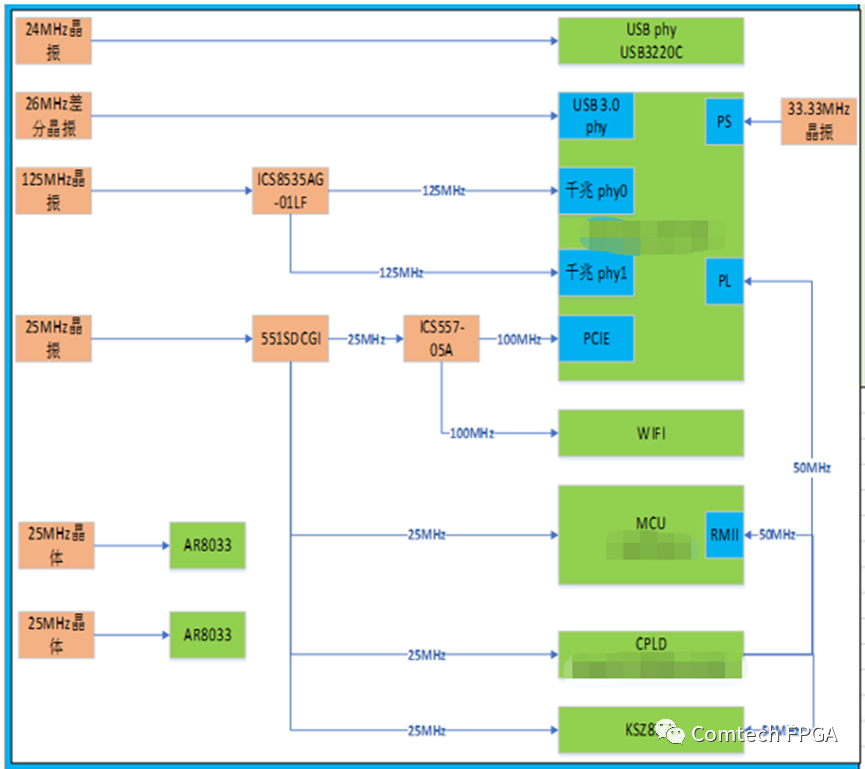

時鐘樹框圖如下:

案例集錦二

結(jié)語:

ZL30265/7隸屬于ZL3026x產(chǎn)品家族,其家族成員具有相同的封裝、相同的Pin腳定義,在當(dāng)前缺芯的大環(huán)境下,能帶給您更多的選擇空間。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1645文章

22049瀏覽量

618389 -

microchip

+關(guān)注

關(guān)注

52文章

1549瀏覽量

119061 -

Xilinx

+關(guān)注

關(guān)注

73文章

2185瀏覽量

125325 -

時鐘芯片

+關(guān)注

關(guān)注

2文章

271瀏覽量

40808

原文標(biāo)題:一種適配Xilinx FPGA的時鐘芯片--Microchip ZL30265/7

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于Intersil ZL2008的數(shù)字電源電路設(shè)計 —電路圖天天讀(52)

數(shù)字DC-DC轉(zhuǎn)換器控制原理 ZL2008的主要特性 方框圖

Intersil全集成式6A數(shù)字同步步降DC/DC電源穩(wěn)壓器ZL2102

嵌入式互聯(lián)網(wǎng)概要性介紹

STM32時鐘系統(tǒng)內(nèi)容概要

如何配置基于Win 2003 的服務(wù)器

CT107D_單片機綜合訓(xùn)練平臺概要介紹

AD級聯(lián)的工作方式配置和AD雙排序的工作方式配置詳細(xì)說明

ZL6305和ZL6300的完美結(jié)合:解決加載時間長系統(tǒng)的復(fù)位難題

ZL30265/7概要介紹、特性及配置方式

ZL30265/7概要介紹、特性及配置方式

評論