HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

網址如下:

https://hdlbits.01xz.net/

關于HDLBits的Verilog實現可以查看下面專欄:

https://www.zhihu.com/column/c_1131528588117385216

縮略詞索引:

SV:SystemVerilog

Problem 28-Alwaysblock1

從這一題開始我們將進行過程塊的學習,也就是時序和組合邏輯的一些知識,下面簡單介紹一下這方面知識:

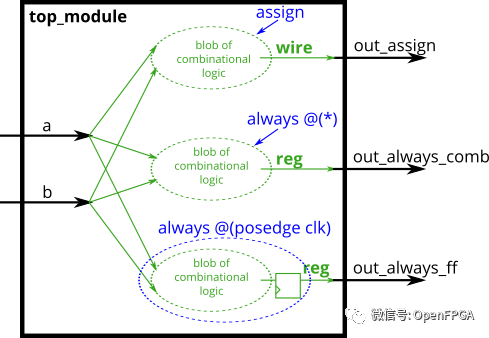

由于數字電路是由用導線連接的邏輯門組成的,因此任何電路都可以表示為module和assign語句的某種組合。然而,有時這并不是描述電路的最方便的方式。過程塊(比如always塊)提供了一種用于替代assign語句描述電路的方法。

對于可綜合硬件,有兩種類型的 always :

組合邏輯:always@(*) 時序邏輯:always@(posedgeclk)

組合always塊相當于assign語句,因此組合電路存在兩種表達方法。選擇使用哪個主要是哪個語法更方便的問題。程序塊內部代碼的語法與外部代碼不同。程序塊具有更豐富的語句集(例如,if-then、case),不能包含連續賦值,但是卻引入了許多新的非直觀的出錯方式。 (程序連續賦值確實存在,但與連續賦值有些不同,并且不可綜合。)

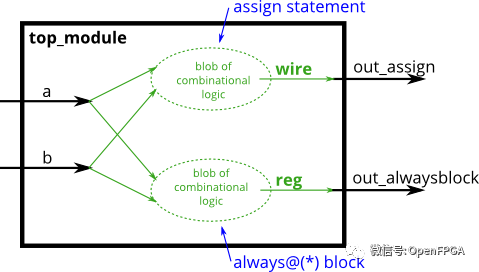

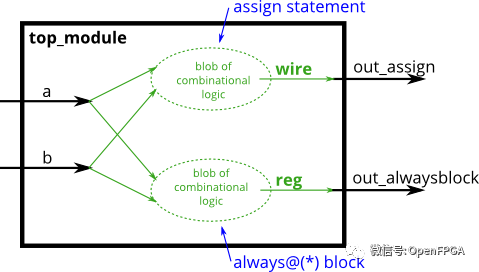

例如,assign和組合always塊描述相同的電路。兩者都創建了相同的組合邏輯塊。每當任何輸入(右側)更改值時,兩者都會重新計算輸出。

assignout1=a&b|c^d; always@(*)out2=a&b|c^d;

圖片來自 HDLBits

圖片來自 HDLBits

對于組合always塊,敏感變量列表總是使用(*)。如果把所有的輸入都列出來也是可以的,但容易出錯的(可能少列出了一個),并且在硬件綜合時會忽略您少列了一個,仍按原電路綜合。 但仿真器將會按少列一個來仿真,這導致了仿真與硬件不匹配。(在SystemVerilog中,使用always_comb)

關于 wire 與 reg 的注意事項:assign 語句的左側必須是net類型(例如,wire),而過程賦值(在 always 塊中)的左側必須是變量類型(例如,reg)。這些類型(wire vs. reg)與合成的硬件無關,只是 Verilog 用作硬件模擬語言時留下的語法。

題目說明

使用 assign 語句和組合 always 塊構建 AND 門。

圖片來自 HDLBits

圖片來自 HDLBits

模塊端口聲明

//synthesisverilog_input_versionverilog_2001 moduletop_module( inputa, inputb, outputwireout_assign, outputregout_alwaysblock );

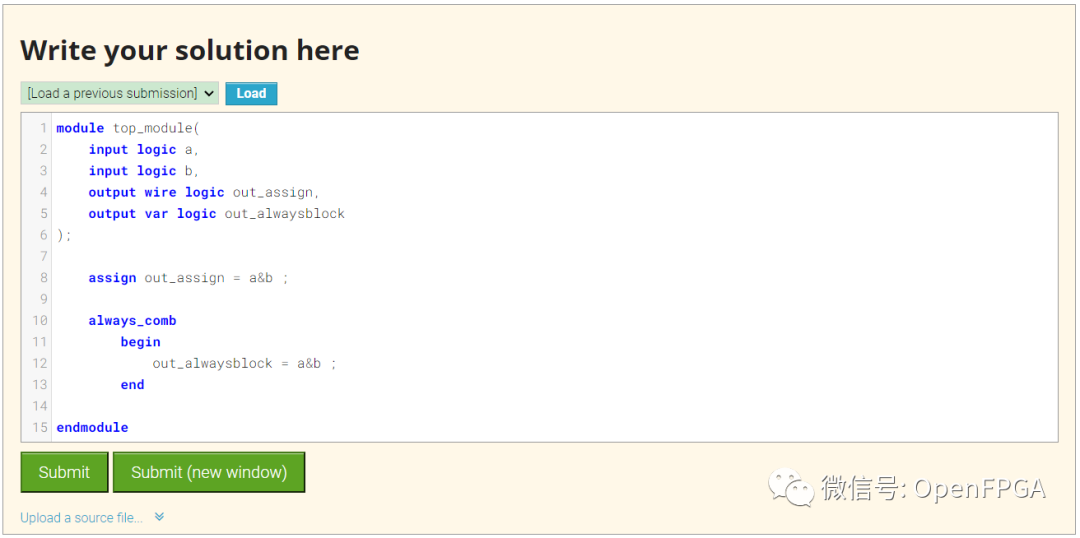

題目解析

這個題目重點是使用assign和always兩種方式描述一個AND門,整體難度不大。

moduletop_module( inputlogica, inputlogicb, outputwirelogicout_assign, outputvarlogicout_alwaysblock ); assignout_assign=a&b; always_comb begin out_alwaysblock=a&b; end endmodule

always_comb程序有很多好處,其中之一便是能自動推斷出完整的敏感列表。該列表是完全完整的,避免了@*推斷不完整敏感列表的極端情況。

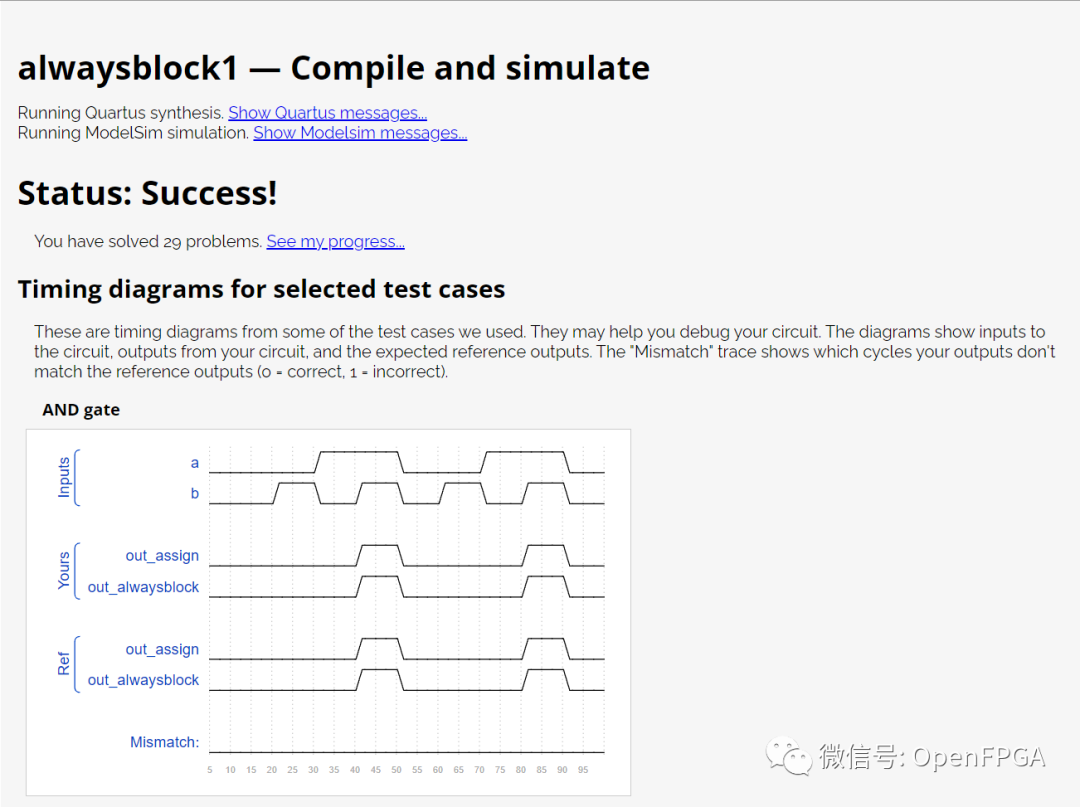

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 29-Alwaysblock2

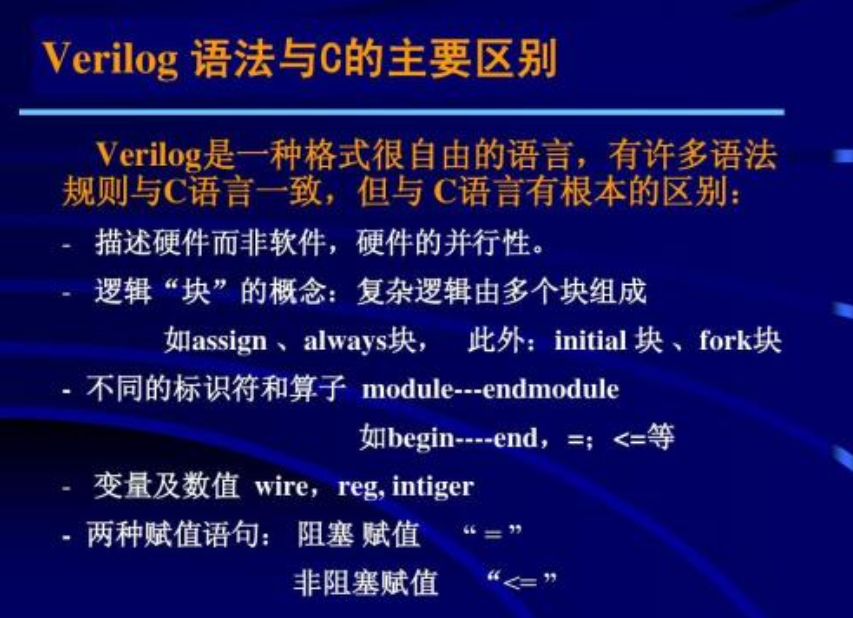

阻塞性賦值和非阻塞性賦值

在Verilog中有以下三種賦值方法:

連續賦值(assign x=y;):不能在過程塊內使用;

過程阻塞性賦值(x=y;):只能在過程塊中使用;

過程費阻塞性復制(x<=y):只能在過程塊內使用。

在組合always塊中,使用阻塞性賦值。在時序always塊中,使用非阻塞性賦值。具體為什么對設計硬件用處不大,還需要理解Verilog模擬器如何跟蹤事件(的確是這樣,記住組合用阻塞性,時序用非阻塞性就可以了)。不遵循此規則會導致極難發現非確定性錯誤,并且在仿真和綜合出來的硬件之間存在差異。

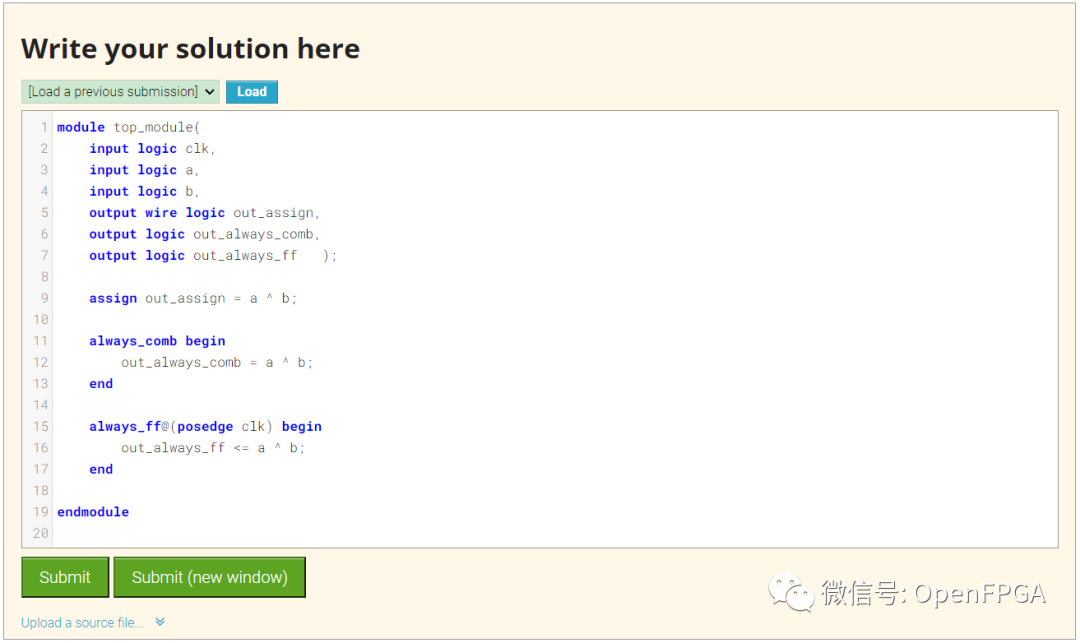

題目說明

以三種方式構建異或門,使用assign語句、組合always塊和時序always塊。請注意,時序always塊產生的電路與其他兩個不同:有一個觸發器,因此輸出被延遲。

圖片來自 HDLBits

圖片來自 HDLBits

模塊端口聲明

//synthesisverilog_input_versionverilog_2001 moduletop_module( inputclk, inputa, inputb, outputwireout_assign, outputregout_always_comb, outputregout_always_ff);

題目解析

這道題難度不大,主要時區分三種方式。

moduletop_module( inputlogicclk, inputlogica, inputlogicb, outputwirelogicout_assign, outputlogicout_always_comb, outputlogicout_always_ff); assignout_assign=a^b; always_combbegin out_always_comb=a^b; end always_ff@(posedgeclk)begin out_always_ff<=?a?^?b; ????end endmodule

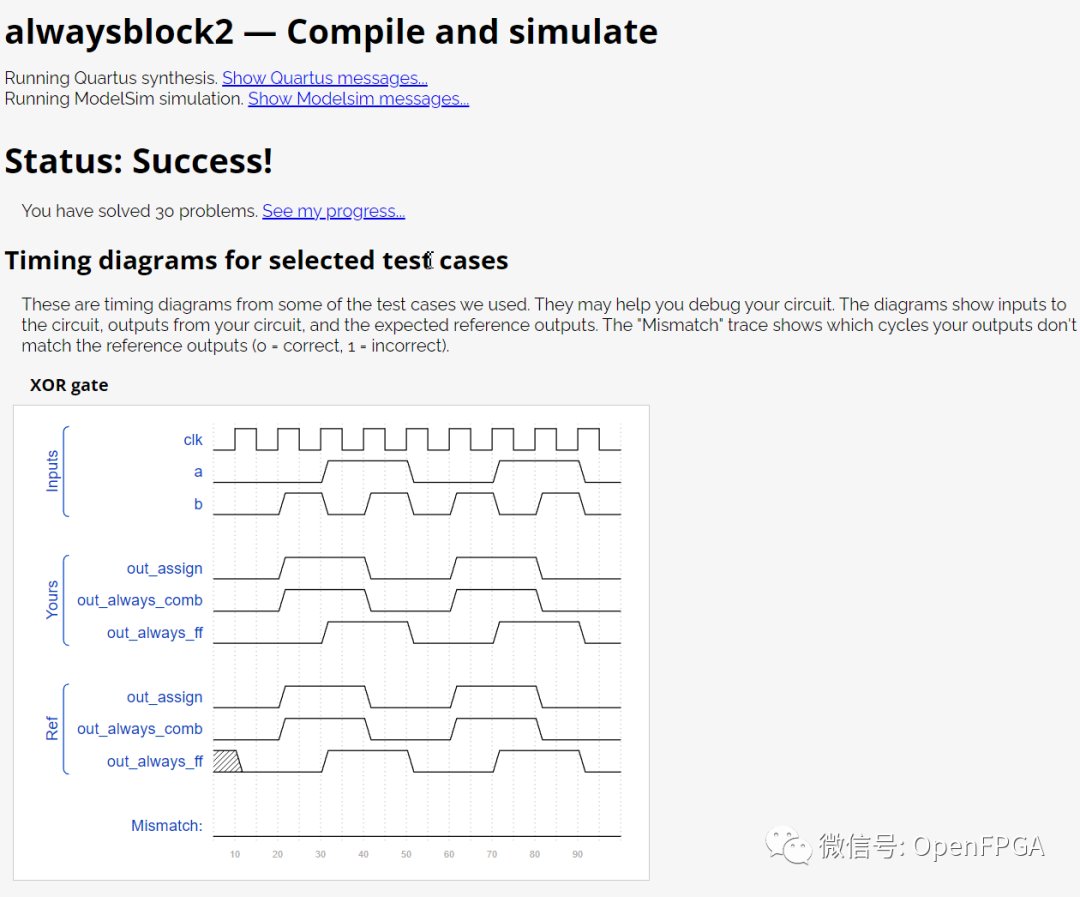

點擊Submit,等待一會就能看到下圖結果:

從仿真的波形圖可以看出,out_always_ff比其他兩個輸出延遲了一個時鐘周期,這就是非阻塞性賦值帶來的。

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

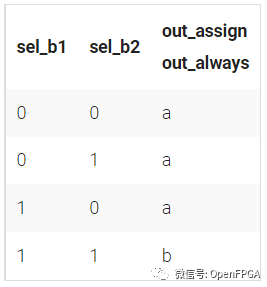

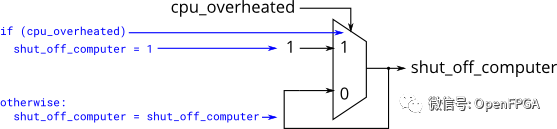

Problem 30-Always if

if語句通常創建一個2 對 1 多路復用器,如果條件為真則選擇一個輸入,如果條件為假則選擇另一個輸入。

下面給出了一個基本的if語句和其綜合出來的電路。

always@(*)begin if(condition)begin out=x; end elsebegin out=y; end end

這與下面使用條件運算符連續賦值的語句是等價的:

assignout=(condition)?x:y;

但是,過程if語句使用不當可能會引入新的錯誤,只有out在所有的條件下都被賦值才會生成正確的組合電路。

題目說明

構建一個在a和b之間進行選擇的 2 對 1 多路復用器。如果sel_b1和sel_b2都為真,則選擇b 。其他情況輸出a。請使用兩種方法作答,一次使用assign賦值,一次使用if語句。

模塊端口聲明

moduletop_module( inputa, inputb, inputsel_b1, inputsel_b2, outputwireout_assign, outputregout_always);

題目解析

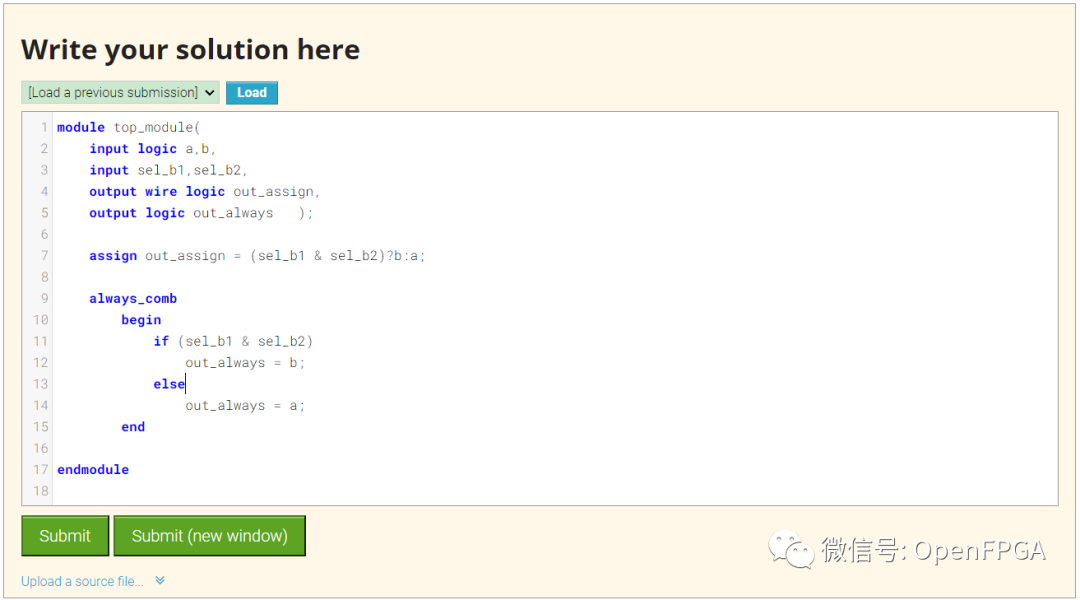

本題考查的是if語句的簡單用法,使用條件運算符作為對比,入門練習題。

moduletop_module( inputlogica,b, inputsel_b1,sel_b2, outputwirelogicout_assign, outputlogicout_always); assignout_assign=(sel_b1&sel_b2)?b:a; always_comb begin if(sel_b1&sel_b2) out_always=b; else out_always=a; end endmodule

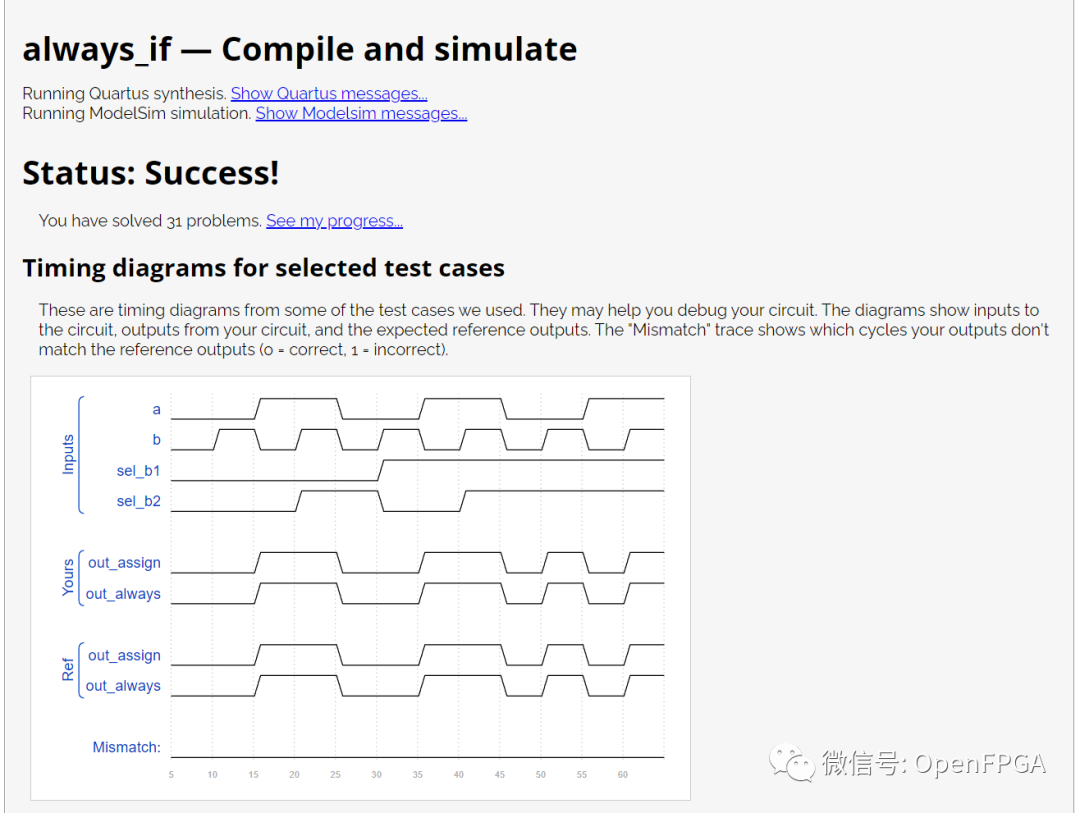

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

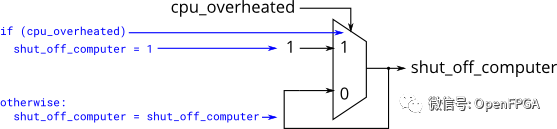

Problem 31-Always_if2

常見的錯誤來源:如何避免引入鎖存器

在設計電路時,必須首先具體考慮電路:

1、我想實現一個邏輯門;

2、我想實現一個具有輸入并產生輸出的組合邏輯塊;

3、我想實現一組組合邏輯,緊接著一組觸發器。

不要上來就寫代碼,這樣往往與你想象的電路相差很遠。

if(cpu_overheated)thenshut_off_computer=1; if(~arrived)thenkeep_driving=~gas_tank_empty;

除了你指定的情況以外,會發生些什么,答案是什么也不會發生,輸出保持不變。而這往往就導致了電路的錯誤,所以說語法正確的代碼不一定能產生合理的電路(組合邏輯+觸發器)。

輸出保持不變,這就意味著電路需要記住當前狀態,從而產生鎖存器。組合邏輯(比如邏輯門)不能記住任何狀態。

題目說明

以下代碼包含創建鎖存器的不正確行為。修復錯誤~

always@(*)begin if(cpu_overheated) shut_off_computer=1; end always@(*)begin if(~arrived) keep_driving=~gas_tank_empty; end

圖片來自 HDLBits

圖片來自 HDLBits

模塊端口聲明

moduletop_module( inputcpu_overheated, outputregshut_off_computer, inputarrived, inputgas_tank_empty, outputregkeep_driving);

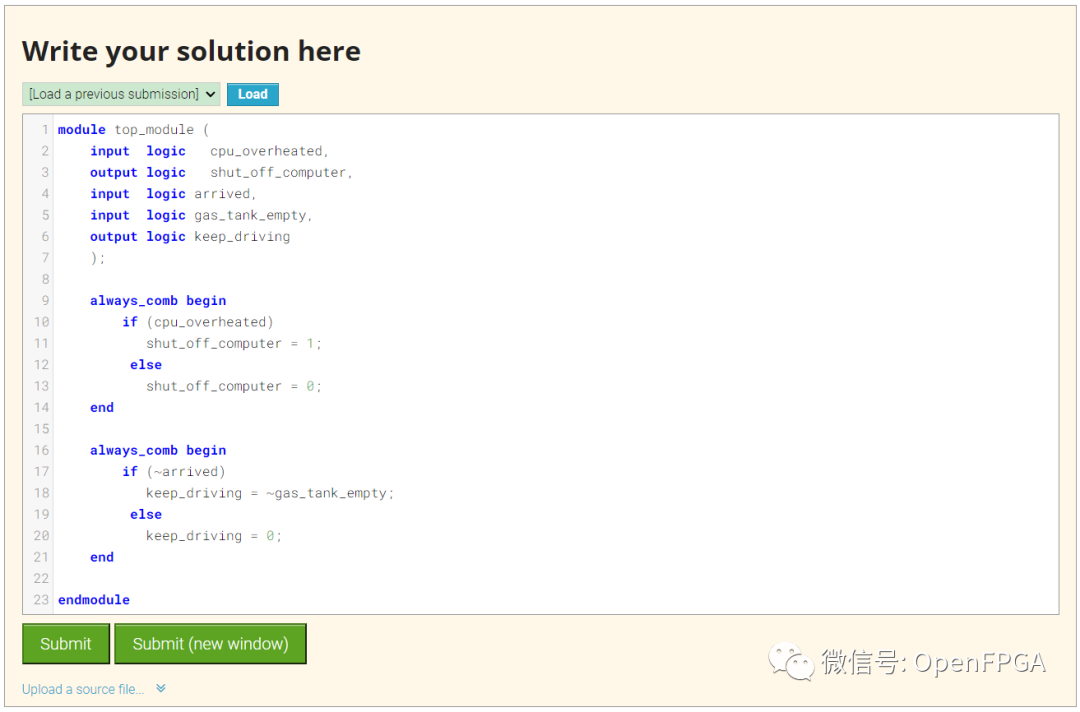

題目解析

這個題目的核心是修復由于各種原因在組合電路中引入的鎖存器代碼,理解了前面說的產生鎖存器的原因,看這個代碼還是比較好找出問題的,盡量補全if語句的條件。

moduletop_module( inputlogiccpu_overheated, outputlogicshut_off_computer, inputlogicarrived, inputlogicgas_tank_empty, outputlogickeep_driving ); always_combbegin if(cpu_overheated) shut_off_computer=1; else shut_off_computer=0; end always_combbegin if(~arrived) keep_driving=~gas_tank_empty; else keep_driving=0; end endmodule

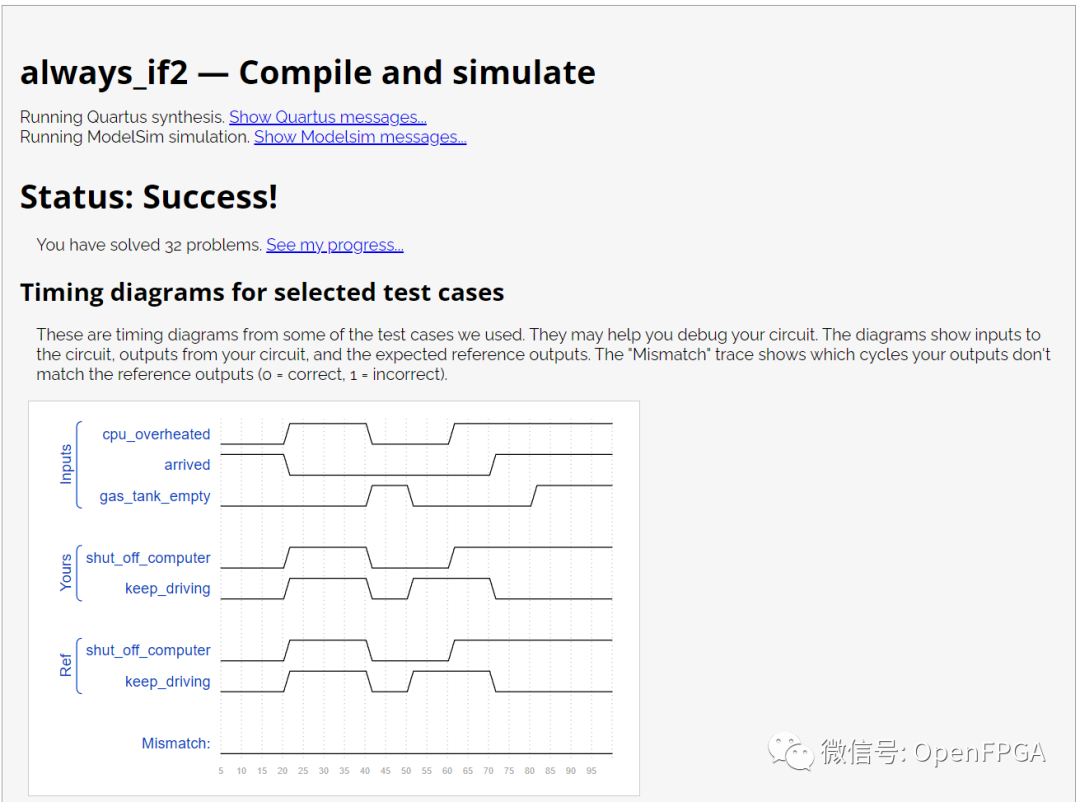

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

總結

今天的幾道題就結束了,整體難度不大,逐漸的在學習新知識~

最后我這邊做題的代碼也是個人理解使用,有錯誤歡迎大家批評指正,祝大家學習愉快~

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614078 -

硬件

+關注

關注

11文章

3461瀏覽量

67193 -

Verilog

+關注

關注

28文章

1366瀏覽量

111815 -

HDL

+關注

關注

8文章

330瀏覽量

47822

原文標題:HDLBits: 在線學習 SystemVerilog(七)-Problem 28-31

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

HDLBits: 65.mux256to1v

夏宇聞老師優秀的verilog教程課件

基本組合邏輯功能雙向管腳的Verilog HDL源代碼

Verilog實現74LS194芯片設計程序

關于Verilog語言標準層次問題

關于verilog的學習經驗簡單分享

FPGA設計中DAC控制的Verilog實現

HDLBits:在線學習 Verilog (二十八 · Problem 135-139)

關于HDLBits的Verilog實現

關于HDLBits的Verilog實現

評論