高端計算的解決方案是堆疊硅片。

一批高性能處理器表明,延續(xù)摩爾定律的新方向是向上發(fā)展。每一代處理器都要比上一代性能更好,究其根本,這意味著要在硅片上集成更多的邏輯。但其中存在兩個問題。首先,我們縮小晶體管及其組成的邏輯和內(nèi)存塊的能力正在放緩。其次,單塊芯片已經(jīng)達到了尺寸極限。光刻工具可以在850平方毫米的面積內(nèi)繪制圖案,這大約是一個現(xiàn)代服務(wù)器圖形處理單元(GPU)的大小。

有一種解決辦法是將兩塊或多塊硅片并排放置在同一個封裝中,并使用幾毫米長的密集互連將它們縫合在一起,這樣它們就可以作為一個單元有效地運行。這種所謂的2.5D方案由先進的封裝技術(shù)實現(xiàn),已經(jīng)落后于幾個頂級處理器,這些處理器現(xiàn)在由多個功能性“芯粒”組成,而不是單個集成電路。 但是,要像在同一塊芯片上一樣傳輸大量數(shù)據(jù),我們需要更短、更密集的連接,而這只能通過將一塊芯片堆疊在另一塊芯片上來實現(xiàn)。在3D方案中面對面連接兩塊芯片可能意味著每平方毫米要有數(shù)百甚至數(shù)千微米長的連接。通過這些短而密集的連接,只需很少的能量就能將數(shù)據(jù)從一塊硅片快速傳輸?shù)搅硪粔K,就好像兩塊硅片是一塊芯片一樣。

要做到這一點需要很多創(chuàng)新。工程師們必須想辦法防止堆棧中一塊芯片的熱量破壞另一塊芯片,決定哪些功能應(yīng)該放在哪里、這些功能如何實現(xiàn),防止偶爾出現(xiàn)的壞芯片造成大量昂貴的無用系統(tǒng),以及應(yīng)對一次完成這一切所增加的復(fù)雜性。

以下3個示例不僅展示了3D芯片堆疊是如何完成的,還介紹了其優(yōu)勢。

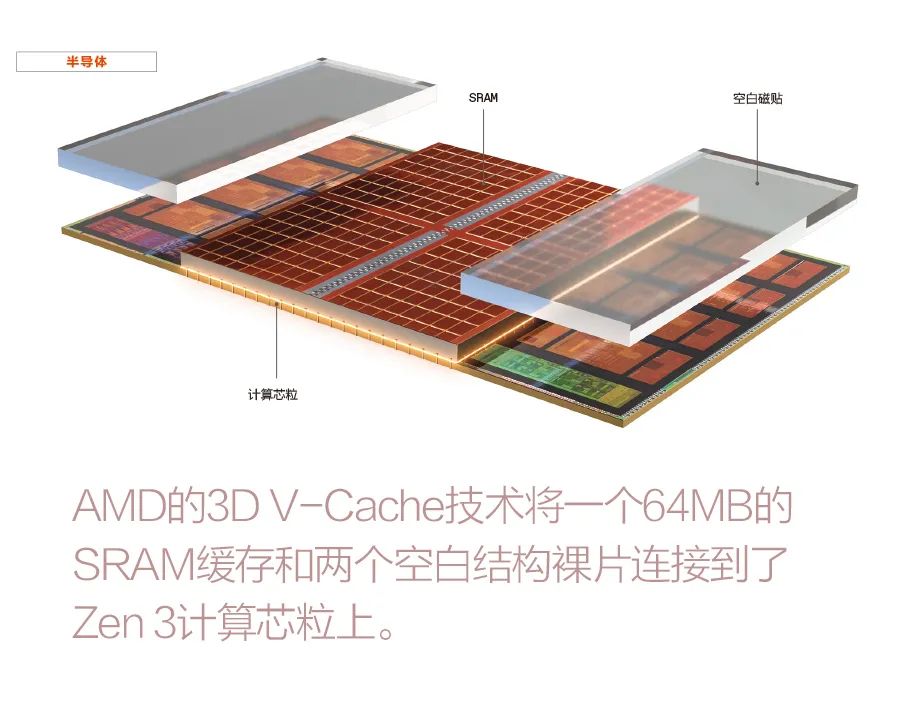

采用3D V-Cache緩存技術(shù)的AMD Zen 3

長期以來,個人計算機都可以選擇增加內(nèi)存,以便提高處理超大應(yīng)用和大數(shù)據(jù)量工作的速度。由于3D芯片堆疊的出現(xiàn),超微半導(dǎo)體公司(AMD)的下一代CPU芯粒也有了這個選擇。當然,這不是售后市場的擴展組件,但如果你想打造一臺更具魅力的計算機,那么訂購一款有超大緩存的處理器可能是正確的選擇。

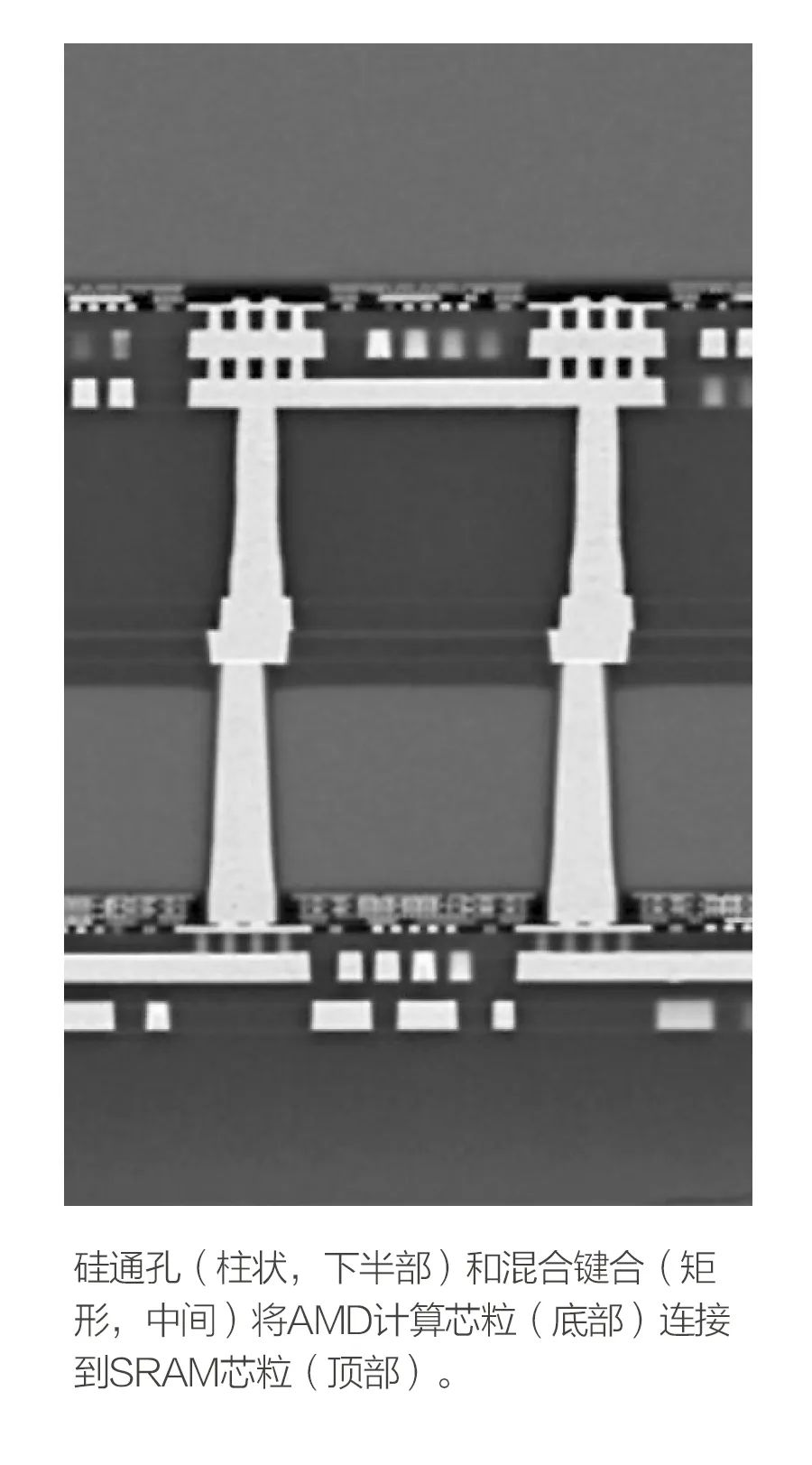

新款Zen 3計算芯粒及其前代版本均采用了相同的臺積電(TSMC)制造工藝,因此其晶體管大小、互連和其他屬性均相同。但是AMD對Zen 3做了很多架構(gòu)修改,因此即使沒有額外的高速緩存,其時鐘運行速度也提高了6%,平均性能也提高了19%。在這些架構(gòu)瑰寶之上,還有一組硅通孔(TSV),即直接穿透大部分硅的垂直互連。硅通孔構(gòu)建在Zen 3的最后一級緩存中,也就是名為L3的靜態(tài)隨機存取存儲器(SRAM)塊中。緩存位于計算芯粒的中間,并由其全部8個內(nèi)核共享。 在處理大量數(shù)據(jù)工作負載的處理器中,Zen 3晶圓的背面被減薄,使得硅通孔暴露出來。

然后,使用混合鍵合(參見補充介紹“3D技術(shù)”)將64MB的SRAM芯粒連接到這些暴露出來的硅通孔上。后一種技術(shù)可以每隔9微米在CPU內(nèi)核和高速緩存之間形成連接。最后,為了結(jié)構(gòu)穩(wěn)定性和便于熱傳導(dǎo),附加上空白硅芯粒以覆蓋Zen 3 CPU裸片的其余部分。 以2.5D排列形式在CPU 裸片旁額外添加緩存并不可取,因為數(shù)據(jù)要花很長時間才能到達處理器內(nèi)核。AMD高級研究員、設(shè)計工程師約翰?吳(John Wuu)在今年2月舉行的IEEE國際固態(tài)電路會議(ISSCC)上對虛擬參會者說:“雖然L3(緩存)的尺寸增加了兩倍,但3D V-cache只增加了4個(時鐘)周期的延遲,這只有通過3D堆疊才能實現(xiàn)。”

更高的緩存在高端游戲中有了用武之地。使用臺式銳龍CPU和3D V-Cache可將1080p渲染的游戲速度平均提高15%。這也適用于霄龍服務(wù)器中央處理機(CPU)所處理的更重要的工作,可將困難的半導(dǎo)體設(shè)計驗證工作的運行時間縮短66%。

吳指出,與縮小邏輯的能力相比,業(yè)界縮小SRAM的能力正在放緩。因此,未來的SRAM擴展包可能會繼續(xù)使用更成熟的制造工藝,而計算芯粒將被推到摩爾定律的最前沿。

Graphcore的Bow AI處理器

即使堆棧中的一塊芯片上沒有晶體管,3D集成也可以加快計算速度。總部位于英國的人工智能(AI)計算機公司Graphcore僅通過在其AI處理器上安裝一塊功率傳輸芯片,就大幅提高了其系統(tǒng)的性能。增加功率傳輸硅片意味著名為Bow的組合芯片可以運行得更快,為1.85而非1.325千兆赫,且電壓低于其前一代。與上一代相比,這相當于通過訓(xùn)練神經(jīng)網(wǎng)絡(luò)使計算機的速度提高了40%,而能耗降低了16%。重要的是,用戶無須更改其軟件便能獲得這種提升。 功率管理裸片由電容器和硅通孔組合而成。后者只是向處理器芯片供電和提供數(shù)據(jù)。真正起作用的是電容器。

與動態(tài)RAM中的位存儲組件一樣,這些電容器位于硅片中深窄的溝槽中。由于這些電荷儲存器離處理器晶體管非常近,因此功率可以順暢地傳輸,從而能使處理器內(nèi)核在較低電壓下更快地運行。如果沒有功率傳輸芯片,處理器必須將其工作電壓提高到標稱水平以上,才能在1.85千兆赫下工作,因此耗電量更高。有了功率芯片,它可以實現(xiàn)更高的時鐘頻率,并且功耗也更低。 Bow的制造工藝獨一無二,但不太可能一直保持這種方式。

大多數(shù)3D堆疊是在其中一塊芯片仍在晶圓上時將一塊芯片鍵合到另一塊芯片上完成的,稱為“晶圓上芯片”(chip-on-wafer)。相反,Bow采用了臺積電的堆疊晶圓(wafer-on-wafer)技術(shù),將一種類型的整片晶圓與另一種類型的整片晶圓鍵合起來,然后切割成芯片。

Graphcore首席技術(shù)官兼聯(lián)合創(chuàng)始人西蒙?諾爾斯(Simon Knowles)表示,Bow是市場上第一款使用這種技術(shù)的芯片,它使兩塊裸片之間的連接密度高于使用晶圓上芯片工藝所能達到的密度。 雖然目前Graphcore的功率傳輸芯片沒有晶體管,但未來可能會有。諾爾斯說,將這種技術(shù)用于功率傳輸“只是我們的第一步,在不久的將來,它會走得更遠”。

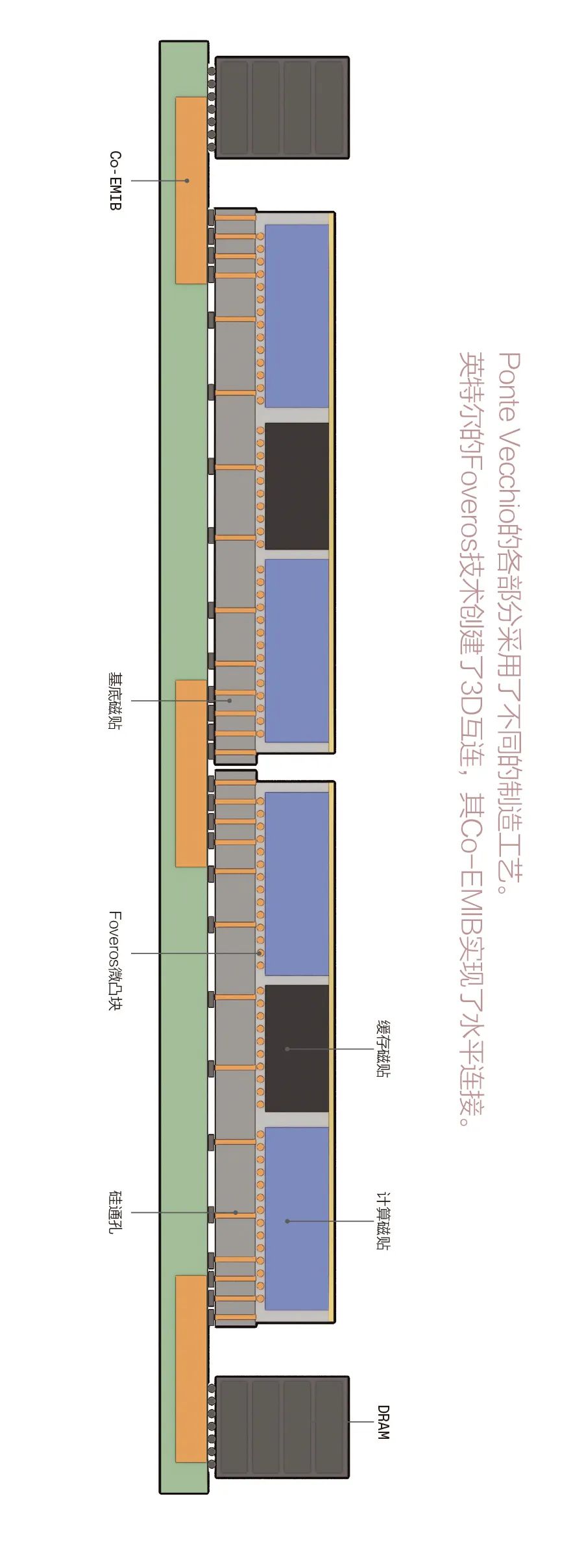

極光超級計算機旨在成為美國首批突破exaflop屏障(每秒百億億次高精度浮點運算)的高性能計算機之一。為了讓極光達到這種高度,英特爾的Ponte Vecchio在47塊硅片上封裝了1000多億個晶體管,構(gòu)成了一臺處理器。英特爾使用2.5D和3D技術(shù)將3100平方毫米的硅片塞進了2330平方毫米的空間中,大約相當于4塊英偉達A100 GPU。

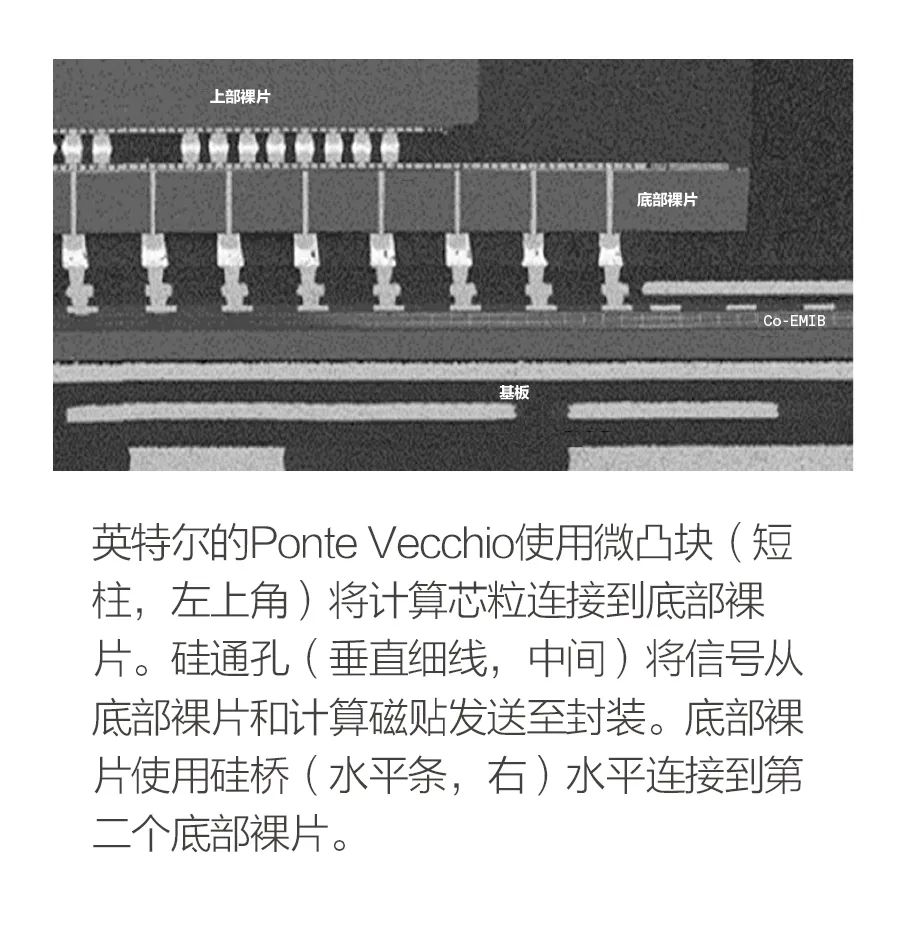

英特爾院士威爾弗雷德?戈麥斯(Wilfred Gomes)在ISSCC上對各位工程師說,這款處理器將英特爾的2D和3D集成技術(shù)推向了極限。 每個Ponte Vecchio實際上是兩組使用英特爾2.5D集成技術(shù)Co-EMIB連接在一起的鏡像芯粒。Co-EMIB是“共嵌式多裸片互連橋接”的縮寫,它在兩個3D芯粒堆棧之間形成了高密度互連硅橋。Co-EMIB裸片還將高帶寬內(nèi)存和一個I/O芯粒連接到了其余芯粒堆疊的“基底磁貼”上。

基底磁貼采用了英特爾的3D集成技術(shù)Foveros,將計算和緩存芯粒堆疊其上。Foveros使用微凸塊(每根頂部有一個微米寬焊球的短銅柱)使垂直連接相隔幾十微米。信號和電源通過硅通孔進入該堆棧。 8個計算磁貼、4個緩存磁貼和8個給處理器散熱的空白“熱”磁貼都連接到了基底磁貼上。基底磁貼本身具備高速緩存和允許任何計算磁貼訪問任何存儲元件的網(wǎng)絡(luò)。  ?

?

無需多言,這一切都不容易。戈麥斯對與會者說,這項技術(shù)在收益管理、時鐘電路、熱調(diào)節(jié)和功率傳輸方面進行了創(chuàng)新。例如,英特爾工程師選擇為處理器提供高于正常值(1.8伏)的電壓,以便電流足夠低,從而簡化封裝。基底磁貼中的電路將電壓降低到了近0.7伏,以便在計算磁貼上使用,并且每個計算磁貼必須在基底磁貼上有自己的功率域。這項能力的關(guān)鍵是一種名為“同軸磁集成電感器”的新型高效組件。因為這些組件都內(nèi)置在封裝基板中,所以在向計算磁貼提供電壓之前,電路實際上在基底磁貼和封裝之間來回蜿蜒。

戈麥斯表示,從2008年第一臺千萬億次浮點運算超級計算機發(fā)展到今年的百億億次浮點運算超級計算機花了14年。他預(yù)測,借助3D堆疊等先進封裝技術(shù),下次將計算速度提高千倍所需的時間可能會縮短到6年。

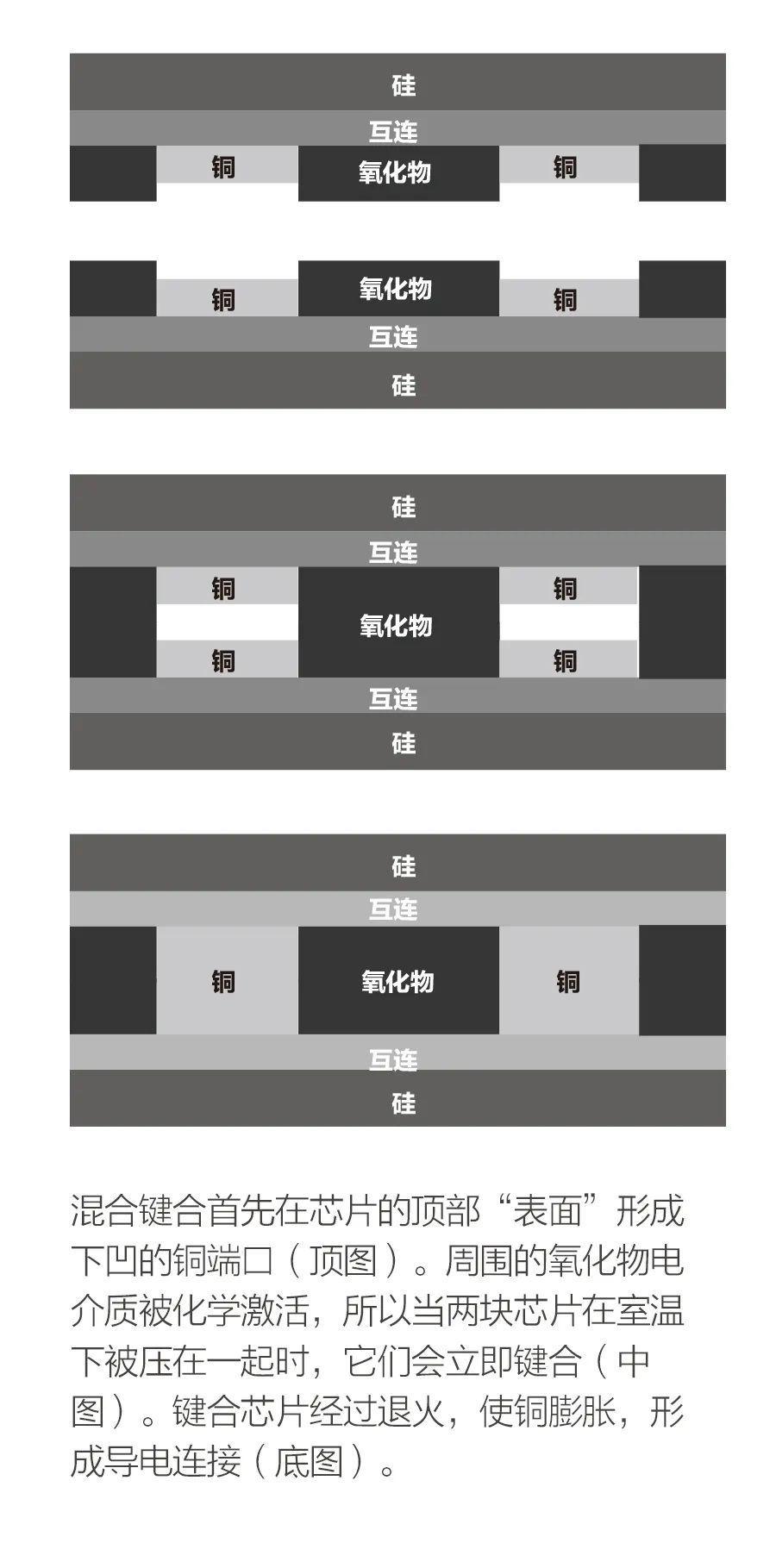

3D技術(shù)

混合鍵合將芯片互連堆棧頂部的銅焊盤與另一塊芯片上的銅焊盤直接鍵合在一起。在混合鍵合中,焊盤位于被氧化物絕緣體包圍的小凹槽中。絕緣體被化學(xué)激活,在室溫下被反向按壓時會立即結(jié)合。然后,在退火步驟中,銅焊盤會膨脹并橋接間隙,形成低阻抗鏈路。 混合鍵合的連接密度高達每平方毫米1萬個鍵合,遠高于微凸塊技術(shù)每平方毫米400至1600個鍵合的連接密度(見圖表)。

如今可以實現(xiàn)的間距(從一個互連的邊緣到下一個互連最邊緣的距離)約為9微米,更緊密的幾何結(jié)構(gòu)正在研究中。封裝技術(shù)公司ASE集團的工程和技術(shù)營銷總監(jiān)曹麗紅(Lihong Cao,音)表示,這項技術(shù)的極限間距可能在3微米左右。她說,改進混合鍵合最關(guān)鍵的步驟是防止晶圓翹曲,并將每一面的表面粗糙度降低到納米級。

微凸塊本質(zhì)上是一種叫做“倒裝芯片”的標準封裝技術(shù)的縮小版。在倒裝芯片中,焊料凸塊被添加到了芯片頂部(表面)的互連端點。然后將芯片翻轉(zhuǎn)到具有一組匹配互連的封裝基板上,并熔化焊料形成鍵合。要用這種技術(shù)堆疊兩塊芯片,其中一塊芯片的表面必須有短銅柱。然后用一個“微凸塊”焊料蓋住這些芯片,通過熔化焊料將兩塊芯片面對面連接起來。

使用微凸塊時,從一個連接的起點到下一個連接最邊緣的最短距離(也就是間距)可以小于50微米。英特爾在Ponte Vecchio超級計算機芯片中使用了36微米間距版本的Foveros 3D集成技術(shù)。三星表示,其名為3D X-Cube的微凸塊技術(shù)可以實現(xiàn)30微米的間距。該技術(shù)達不到(上述)混合鍵合的密度。然而,它對對齊和平面化的要求并不像混合鍵合那樣嚴格,因此更容易將采用不同制造技術(shù)制造的多塊芯片堆疊到單個基極芯片上。

硅通孔(TSV)是垂直向下穿過芯片硅的互連。它們不會貫穿整個晶圓,因此必須將硅片的背面磨平,直至硅通孔暴露出來。這在3D堆疊芯片中通常是必要的,因為要將芯片鍵合在一起使其互連面對面。在這種情況下,硅通孔可為堆棧供電并提供數(shù)據(jù)。多年來,它們在垂直堆疊多塊內(nèi)存芯片的高帶寬動態(tài)RAM中得到了廣泛應(yīng)用。但隨著3D芯片堆疊技術(shù)的發(fā)展,這項技術(shù)也應(yīng)用到了邏輯芯片中。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19799瀏覽量

233490 -

gpu

+關(guān)注

關(guān)注

28文章

4909瀏覽量

130639 -

sram

+關(guān)注

關(guān)注

6文章

780瀏覽量

115657 -

3D芯片

+關(guān)注

關(guān)注

0文章

52瀏覽量

18683

原文標題:3D處理器的3種制造方法

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

預(yù)期提前,鎧俠再次加速,3D NAND準備沖擊1000層

芯片晶圓堆疊過程中的邊緣缺陷修整

從焊錫膏到3D堆疊:材料創(chuàng)新如何重塑芯片性能規(guī)則?

Marvell展示2納米芯片3D堆疊技術(shù),應(yīng)對設(shè)計復(fù)雜性挑戰(zhàn)!

芯片3D堆疊封裝:開啟高性能封裝新時代!

SciChart 3D for WPF圖表庫

2.5D和3D封裝技術(shù)介紹

安寶特產(chǎn)品 3D Evolution : 基于特征實現(xiàn)無損CAD格式轉(zhuǎn)換

3D芯片堆疊是如何完成的

3D芯片堆疊是如何完成的

評論