據全球半導體觀察不完全統計,由DRAM與NAND Flash所主導的傳統存儲市場規模已超過1600億美元,其中最大的內存細分市場DRAM,正逼近當前技術材料和工藝使用的基本物理極限。

從1998年三星生產出最早的商用DDR SDRAM芯片,再到DDR1、DDR2、DDR3、DDR4的延續,然后是即將登臺唱戲的DDR5和正在研發的DDR6,20多年時間里,DRAM技術一直在突破向前。

當下新的技術解決方案如EUV光刻、HBM、3D DRAM、無電容DRAM等逐漸浮出水面,DRAM進入到下一個發展階段,其未來技術路線如何呢?

何為DRAM和DDR?

在探討DRAM技術未來如何演變前,我們先對DRAM和DDR的概念進行理清。

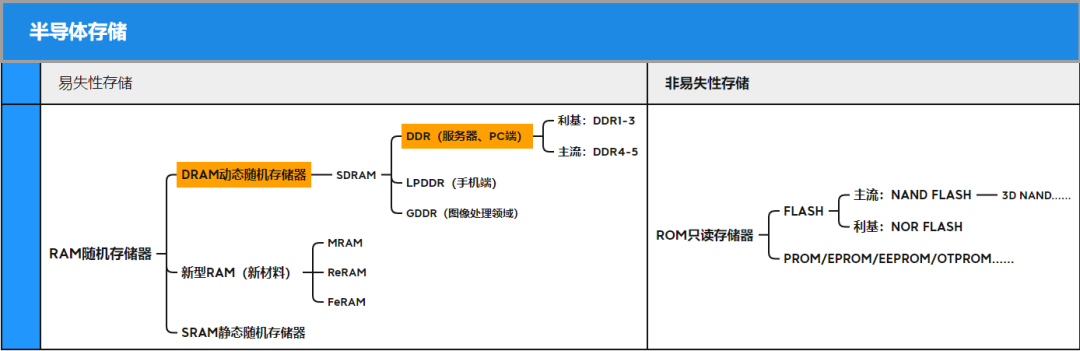

在半導體存儲器中,按照電源關斷后數據能否被保存可分為ROM(Read Only Memory只讀存儲器,關閉電源仍可保留數據)和RAM(Random Access Memory隨機存儲器,關閉電源即丟失數據)。位于RAM之下,又可分為SRAM(靜態隨機存儲器)、DRAM(動態隨機存儲器)以及新型RAM(基于新材料研制而成,尚未實現商業化)三大類。

全球半導體觀察根據公開信息整理

基于DRAM這一支后,又連續衍生了SDRAM(Synchronous DRAM,同步動態隨機存儲器)和DDR SDRAM(Double Data Rate SDRAM,雙倍速率SDRAM,簡稱DDR),從歷史沿革上,DDR可以說是SDRAM的升級版本。

按照不同的應用場景劃分,固態技術協會(JEDEC)把DRAM分成標準DDR、LPDDR、GDDR三類,其中DDR主要應用于服務器和PC端,LPDDR主要應用于手機端和消費電子,GDDR的主要應用領域為圖像處理領域。目前從它們發展情況,三者雖然存在一定的競爭,但是更多是互為借鑒成長。

今天我們討論的焦點則側重于DDR端。

DDR內存建立的初衷是為了加快內存的傳輸速度,從而彌補內存帶寬上的不足,其關鍵的技術就是雙倍數據速率以及預存取。業界數據顯示,在一個時鐘周期中,DDR可以完成SDR兩個周期才能完成的任務,所以在理論上同速率的DDR內存與SDR內存相比,性能要超出一倍,這也是為何SDRAM在所處的那個時代,即便內存帶寬已相當出色,卻仍舊被DDR后來居上的原因。

從市場的角度看,DRAM則分為主流DRAM和利基型DRAM(其指從主流規格退役的DRAM產品,目前主要是DDR3及DDR2,或中低密度容量的產品,多屬于客制化存儲晶圓)。

在主流DRAM市場格局上,以三星、美光、SK海力士三分天下,目前具備DDR5/LPDDR5量產能力的也僅為上述三家。此外,中國臺灣存儲企業華邦及南亞科技,以及大陸存儲企業長鑫存儲的定位也在主流DRAM市場。

而利基型DRAM市場的玩家則相對分散,除了三星、美光、海力士之外(三星已在2021年Q4確定停產DDR2,同時三星及海力士計劃逐步退出DDR3市場),還包含南亞科、華邦等公司。

主流DRAM技術演進

DDR1-DDR6

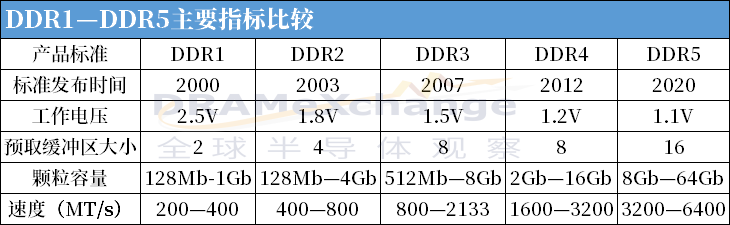

目前已推出的DDR1-DDR5是由固態技術協會(JEDEC)制定的產品標準。從DDR1到DDR5演變看,DDR的能耗越來越低,傳輸速度越來越快、存儲容量也越來越大;而從制程工藝的進展來看,早前產品的更新時間大致在3到5年更新一代,在步入20nm以內的制程后,DDR在制程上的突破進展呈現放緩趨勢。

全球半導體觀察根據公開信息整理

不同于半導體其他工藝直接使用確切數字表達制程的方法,存儲行業近年通常使用1X、1Y、1Z、1α、1β、1γ之類的術語表達制程。對此,美光表示,這種改變很大程度上是因為確切的數字與性能沒有很好的相關性。電路結構是三維的,使用線性的衡量方式并不適合。

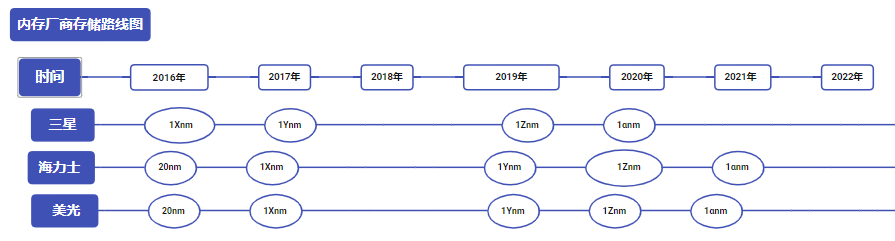

業界認為,10nm~20nm系列制程至少包括六代,1X大約等同于19nm,1Y約等同于18nm,1Z大約為16-17nm,1α、1β、1γ則對應12—14nm(15nm以下)。

據悉,三星電子、SK海力士和美光已在2016~2017年期間進入1Xnm階段,2018~2019年進入1Ynm階段,2020年后進入1Znm階段。目前,各大廠家繼續向10nm逼近,目前最新的1αnm仍處于10+nm階段。

全球半導體觀察根據公開信息整理

從過往歷史看,每代DDR新標準發布后都需要經過2年左右的優化,才能實現性能的較為全面的穩定提升,而后實現對上一代產品的市場替代則可能需要3到5年的時間。業界數據顯示,DDR3和DDR4都享有大約7年的生命周期。DDR4存儲器標準于2012年發布,而其初代產品則于2014年入市,直到2016年才實現了市場份額的大幅提升。

對于最新一代的DDR5而言,其最新款產品產能還處于爬坡期,售價還較高,性能也未發展到最優。業界預測今年將是DDR5的預熱年,而從明年開始,DDR5滲透率將大幅提升。并且由于DDR技術愈發成熟,DDR5的保質期或比DDR4長。

從推出DDR5標準至今已有兩年時間,JEDEC最近也對DDR5標準 (JESD79-5A)進行了更新,包括密集型云和企業數據中心應用驅動的需求要求,為開發人員提供了兩倍的性能和大大提高的能效。為了更高的密度和更高的性能,DDR5有望采用最先進的DRAM單元技術節點,例如D1z或D1a (D1α)代,這是10納米級DRAM節點的第3代或第4代。DDR5內存包含多項創新和新的DIMM架構,可實現速度等級跳躍并支持未來擴展。

隨著DDR5內存逐漸進入市場,三星又已在馬不停蹄的開發下一代DDR6內存,并預計在2024年之前完成設計。在今年7月召開的研討會上,三星證實將采用MSAP技術研發加強下一代DDR6內存的電路連接,并將適應DDR6內存中增加的層數。就規格而言,DDR6內存的速度將是現有DDR5內存的兩倍,傳輸速度可達12800 Mbps(JEDEC),超頻后的速度可超過17000 Mbps。

哪一條會是DRAM的

未來演進之路?

由于現存的DRAM技術正不斷逼近當前技術材料和工藝使用的基本物理極限,關于DDR6技術亦或是DRAM的未來技術探討遠不止于此,以下將對EUV光刻、HBM、3D DRAM、無電容DRAM技術進行說明。

確信的一步,EUV光刻機的成熟運用

對于DRAM廠商而言,利用EUV光刻機邁入到10nm工藝路線已經成為確信的一步,目前三星、SK海力士和美光三大DRAM廠商已先后采納EUV技術。

TrendForce集邦咨詢分析師吳雅婷表示,使用EUV光刻技術是DRAM制程微縮的必經之路,具體有三大好處:

一是可以使DRAM制程進一步微縮至15nm以下;

二是通過更先進制程的遞進,單顆顆粒的容量向上提升至16Gb或更高;

三是生產制程時間縮短,因為其要曝光的道數可以減少。

三星最早引入EUV光刻。2020年3月,三星率先使用EUV光刻技術,同年10月便開始批量生產基于EUV的14nm DRAM。在此過程中,三星將其最先進的14nm DDR5上的EUV層數從兩層增加到了五層DRAM工藝。今年2月,三星官方表示其基于極紫外(EUV)光刻技術的1z-nm工藝的DRAM已完成了量產。業界消息顯示,三星還將繼續為下一代DRAM增加EUV步驟,其三星的P3工廠也將采用EUV工藝生產10nm DRAM。

SK海力士引入EUV是在2021年。2021年2月,SK海力士完成首個用于DRAM的EUV晶圓廠M16,正式引入了EUV光刻設備。2021年7月,SK海力士宣布量產了1a nm工藝的8千兆的LPDDR4 EUV DRAM。

官方消息顯示,與第三代1z nm內存芯片相比,1a技術在相同的晶圓面積下,生產的芯片數量可以增加25%。此外,2021年SK海力士還發布了據稱是業界性能最高的DDR5 DRAM,作為海力士的第三代高帶寬內存,該芯片被稱為HBM3。

對比前兩家的早早加碼EUV,美光方面則稍晚一些。據外媒此前消息,美光計劃從2024年將EUV納入DRAM開發路線圖,結合今年6月美光董事長盧東暉的發言,其A3廠將會在今年下半年導入EUV設備,為美光1γ DRAM早日量產預做準備。

值得注意的是,與三星和SK海力士相比,美光在2021年便推出了其1anm內存節點DRAM,推出該工藝時,美光依舊未使用EUV光刻技術,美光稱其存儲密度比之前的1z nm節點DRAM提高40%。

廠商對于EUV設備何時引入的考量的重點還在于成本。公開消息顯示,ASML正在著手研發的新旗艦光刻機造價十分高昂,價值便達到4億美元(約合人民幣26.75億元)。現下尖端DRAM是基于大約12~15納米的最小節點,這時引入EUV光刻機時機已經成熟。

挑戰極限,3D DRAM有望接棒

EUV光刻機解決的僅僅是眼下的難題,面對當下的瓶頸,DRAM廠商的長遠命題是材料和架構的突破。

當下,努力通過遷移到3D來顛覆平面DRAM技術成為了DRAM廠商解決困境的共識,這便是3D DRAM技術,其甚至被稱之為未來十年的命題。

DRAM工藝之所以提升越來越難,還需要回歸到它的結構上。DRAM是基于一個晶體管和一個電容器的存儲單元。其擴展是在一個平面上,將每個存儲單元像拼圖一樣拼接起來。要想提升DRAM工藝,電容器的縮放是一個挑戰。另一個挑戰是電容到數字線的電荷共享,要考慮用多少時間將電荷轉移到數字線上、數字線有多長。

既然在一個平面內塞入更多存儲單元很困難,那么將多個平面疊起來行不行?這就是3D DRAM,一種將存儲單元堆疊至邏輯單元上方,以實現在單位晶圓面積上產出更多產量的新型存儲方式。除了晶圓的裸晶產出量增加外,使用3D堆疊技術也能因為可重復使用儲存電容而有效降低 DRAM的單位成本。

3D堆疊技術可在NAND發展上有所借鑒,3D NAND Flash早在2015年就已步入3D堆疊,并開始朝著200+層堆疊過渡,然而DRAM市場卻仍處于探索階段,為了使3D DRAM能夠早日普及并量產,各大廠商和研究院所也在努力尋找突破技術。

曲線突圍路徑,突破這堵內存墻

另外,許多廠商也對內存處理方法進行了研究。據悉,當前的數據處理方案依賴于數據存儲與數據處理分離的體系結構,這需要不斷地在內存中來回傳輸信息,較為耗費時間和精力,且隨著當下數據以指數函數陡升下,性能成本也不斷上升。

突破內存墻的設想便是通過開發不同的接口和協議,從而顯著提高信息傳輸的效率。其中新型內存處理技術HBM(High Bandwidth Memory,高帶寬存儲器)技術以及作為“外部存儲器”互連而獲得采用的Compute Express Link(CXL)在當下獲得的認可度較高。

HBM技術是通過TSV技術進行芯片堆疊,以增加吞吐量并克服單一封裝內帶寬的限制。其能充分利用空間并縮小面積,并且突破了內存容量與帶寬瓶頸。其也因為DRAM和CPU/GPU物理位置的接近使得速度進一步提升。業界消息顯示,目前HBM2在很大程度上是GDDR6的競爭對手。不過從長遠看,因為2D在制造上接近天花板,DRAM仍有很強的3D化趨勢。

CXL則是一種開放標準的行業支持的緩存一致性互連,用于處理器、內存擴展和加速器的鏈接。從本質上講,CXL技術維護CPU內存空間和連接設備上的內存之間的內存一致性,這可以實現資源共享(或池化)以獲得更高的性能,降低軟件堆棧的復雜性,并降低整體系統成本。簡單而言就是可以提供更大的內存空間,目前在這一塊上的玩家主要有三星、英特爾、SK海力士等。

新的研究方向,無電容DRAM

除了以上所述技術外,業界近年也開始在無電容技術方面下功夫,試圖借此解決目前的難題。關于無電容,早有Dynamic Flash Memory、VLT技術、Z-RAM等技術出現,但日前,美國和比利時的獨立研究小組IMEC在2021 IEDM上展示了一款全新的無電容器DRAM,這種新型的DRAM基于IGZO(indium-gallium-zinc-oxide)可以完全兼容300mm BEOL (back-end-of-line),并具有>103s保留和無限 (>1011) 耐久性。

總體而言,無論是哪種方法,均遵循著兩種路徑,要么是在先進封裝上下功能,要么是在先進制程上苦心鉆研。兩條路徑相輔相成,缺一不可。

結 語

DRAM存儲早已滲透到現代生活的方方面面,當下所有以數據為中心的基礎設施都迫切需要更高級智慧的半導體內存和存儲技術,這也是DRAM為何吸引如此之多目光的原因,其深刻關乎著未來相關技術前進的步伐。技術發展日新月異,但是總能從歷史的車輪中看到其行進的道路。當下DRAM又走到了技術發展的十字路口,不破不立,未來DRAM將會走向何方呢,我們拭目以待。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52169瀏覽量

436095 -

DRAM

+關注

關注

40文章

2342瀏覽量

185166 -

DDR

+關注

關注

11文章

731瀏覽量

66371

原文標題:這場DRAM技術困局誰來破?

文章出處:【微信號:TRENDFORCE,微信公眾號:TrendForce集邦】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【「零基礎開發AI Agent」閱讀體驗】+初品Agent

ad7616 burst模式讀取數據時,是否可以在下一個convst啟動轉換?

淺談半導體技術的發展階段

Arm 技術預測:2025 年及未來的技術趨勢

使用ADC121S101的時候,會在未知情況下會進入到一個“異常模式”,為什么?

未來10年智能傳感器怎么發展?美國發布最新MEMS路線圖

給您下一個FPGA項目選擇Pluto XZU20五大理由!

DRAM進入到下一個發展階段,其未來技術路線如何呢?

DRAM進入到下一個發展階段,其未來技術路線如何呢?

評論