最近兩天經(jīng)常看到Chiplet這個詞,以為是什么新技術(shù)呢,google一下這不就是幾年前都在提的先進封裝嗎。最近資本市場帶動了芯片投資市場,和chiplet有關(guān)的公司身價直接飛天。帶著好奇今天扒一扒chiplet是什么:

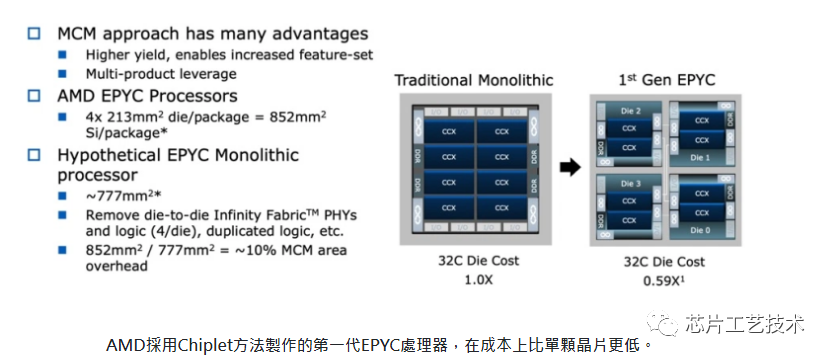

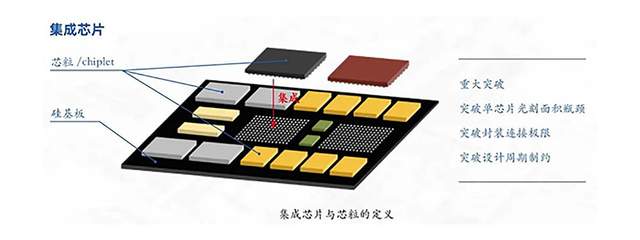

Chiplet的概念其實很簡單,就是硅片級別的重用。從系統(tǒng)端出發(fā),首先將復雜功能進行分解,然后開發(fā)出多種具有單一特定功能、可相互進行模塊化組裝的裸芯片,如實現(xiàn)數(shù)據(jù)存儲、計算、信號處理、數(shù)據(jù)流管理等功能,并最終以此為基礎(chǔ),建立一個Chiplet的芯片網(wǎng)絡(luò)。

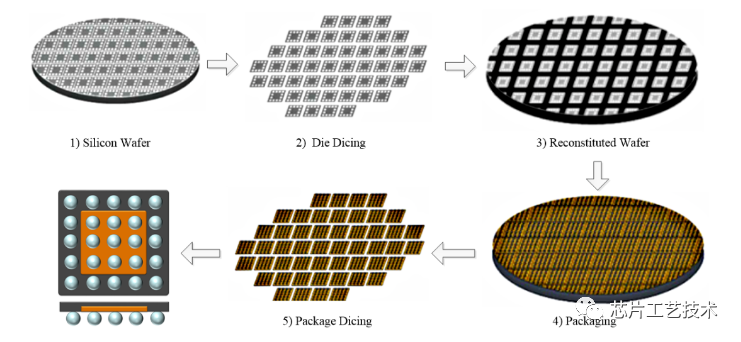

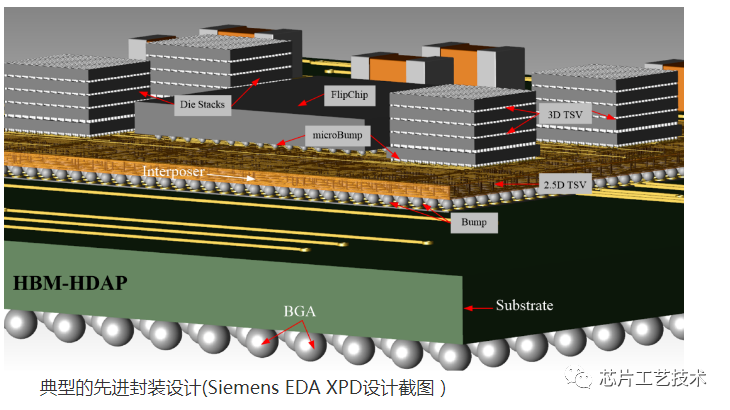

chiplet就是把不同功能的裸芯片,也就是常說的Die,通過某些渠道或者介質(zhì)對接封裝起來,也就是Die-to-Die的技術(shù)。

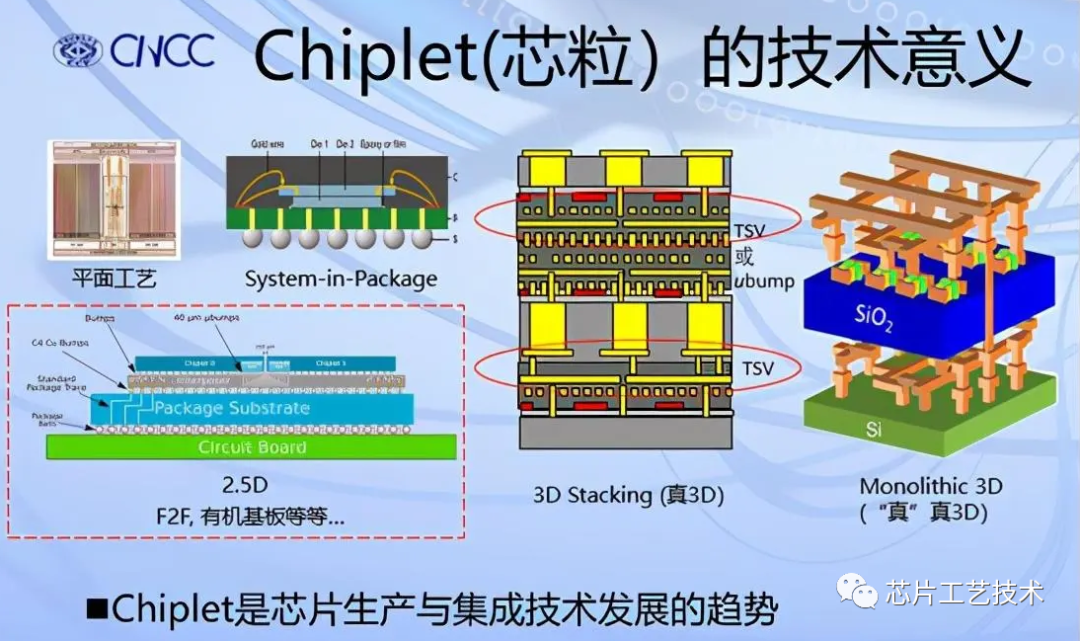

常規(guī)的半導體芯片一般都是2D平面工藝,一層膜,一層圖案,一層介質(zhì)實現(xiàn)特定功能,最終形成具備一些功能的芯片。后來芯片為了實現(xiàn)集成度更高,就會在一個Die上設(shè)計多個模塊功能,有負責計算的部分,通常是數(shù)字電路,也要設(shè)計負責I/O的部分,通常是模擬電路。這些模塊都在同一片die上面設(shè)計好,因此芯片面積都比較大。同時為了追求芯片性能,大家都想采用先進制程,5nm、3nm、1nm,越小越好。但是越小制程難度越大,成本太高,再加上美國作梗,不是所有人都可以用得上5nm。

其實對于芯片,數(shù)字電路采用先進制程可以明顯提高運算性能,但是模擬電路采用先進制程性能提升并不大,有點浪費。

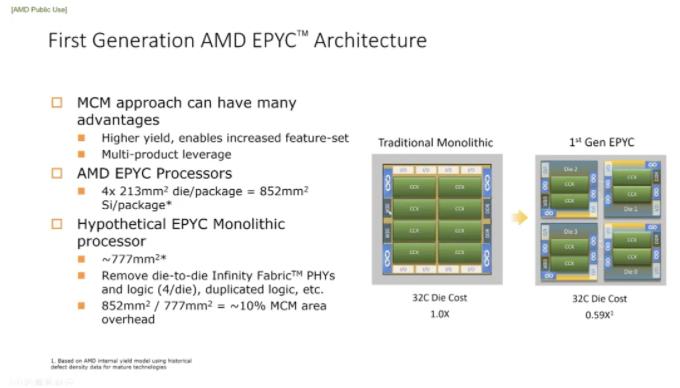

因此就可以想,把本來一個大的die,切割成兩塊或者多塊。數(shù)字電路部分采用新制程,模擬電路采用老制程,這樣既簡化了設(shè)計步驟,又提高了先進制程的利用率,I/O模塊也更經(jīng)濟。

另外采用chiplet降低了單位面積內(nèi)的芯片設(shè)計量,可以適當減少芯片集成度,我的理解是采用14nm的工藝制程說不定可以干5nm的事情。

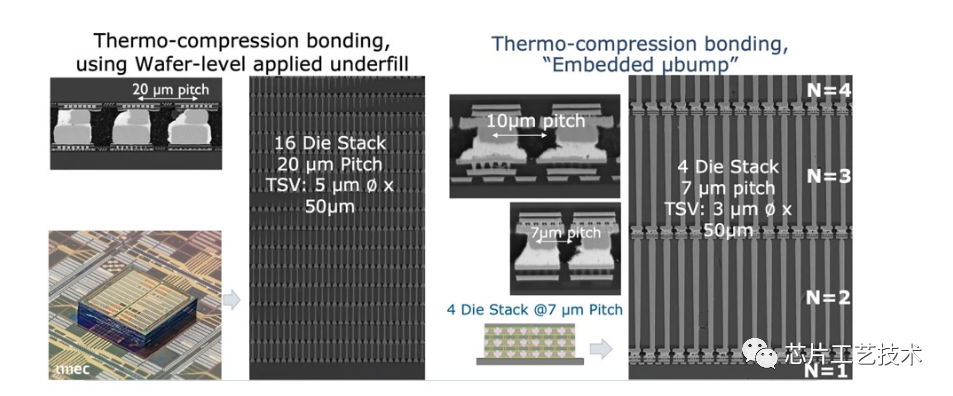

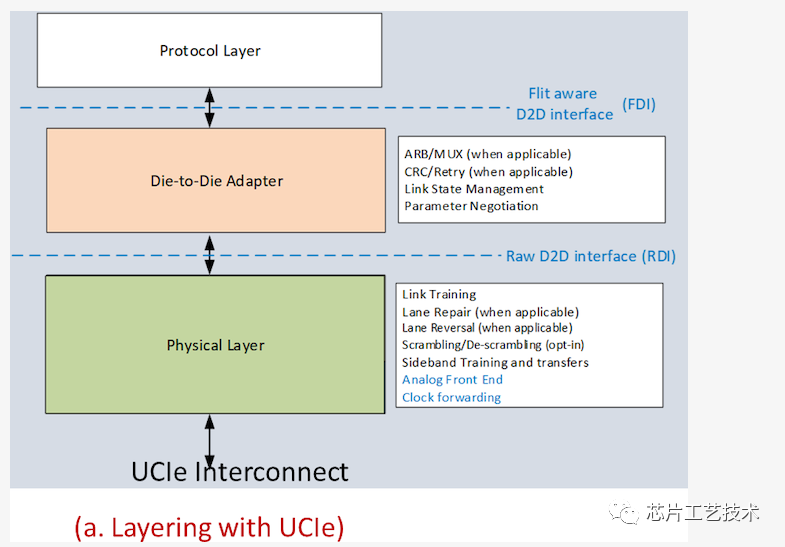

明白了為什么采用chiplet,但是如何用chiplet,就需要die和die之間的互聯(lián)了。和我們做電路一樣的,芯片之間的互聯(lián)也需要協(xié)議,特別是對于這種先進封裝,并沒有行業(yè)規(guī)定,每個芯片廠家設(shè)計的金屬對接口位置可能都不同,因此急需一個標準的出臺。

2022年三月份出現(xiàn)的UCIe, 即Universal Chiplet Interconnect Express,是Intel、AMD、ARM、高通、三星、臺積電、日月光、Google Cloud、Meta和微軟等公司聯(lián)合推出的Die-to-Die互連標準,其主要目的是統(tǒng)一Chiplet(芯粒)之間的互連接口標準,打造一個開放性的Chiplet生態(tài)系統(tǒng)。UCIe在解決Chiplet標準化方面具有劃時代意義。

到目前為止,已經(jīng)成功商用的Die-to-Die互連接口協(xié)議多達十幾種,主要分為串行接口協(xié)議和并行接口協(xié)議。比較而言,串行接口一般延遲比較大,而并行接口可以做到更低延遲,但也會消耗更多的Die-to-Die互連管腳;而且因為要盡量保證多組管腳之間延遲的一致,所以每個管腳不易做到高速率。

UCIe 成員分為三個級別:發(fā)起人、貢獻者和采用者。發(fā)起人由董事會組成并具有領(lǐng)導作用。貢獻者和發(fā)起者公司可以參與工作組,而采用者只能看到最終規(guī)范并獲得知識產(chǎn)權(quán)保護。

貢獻者成員名單如下:

董事會成員有:

但是chiplet也有一些難度,切成小die之后的封裝工作會加倍,精度和具體工藝都需要更精密的儀器設(shè)備來保證,估計又會被歐美日國家把控著。

做成芯片后的測試和原有芯片均不同,疊加后的芯片就像一個黑匣子一樣,不容易查找測試異常。

另外EDA設(shè)計軟件也要跟上,國內(nèi)的設(shè)計軟件目前很難做好這一塊的。

不過對于國內(nèi)半導體行業(yè)也是機遇,畢竟卡脖子問題不解決,也不能做先進制程,不能閑著不是。

審核編輯 :李倩

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81561 -

半導體芯片

+關(guān)注

關(guān)注

60文章

927瀏覽量

71221 -

chiplet

+關(guān)注

關(guān)注

6文章

452瀏覽量

12859

原文標題:什么是Chiplet技術(shù),為啥突然熱起來了

文章出處:【微信號:dingg6602,微信公眾號:芯片工藝技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

從技術(shù)封鎖到自主創(chuàng)新:Chiplet封裝的破局之路

Chiplet與先進封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進封裝

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設(shè)計

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Chiplet技術(shù)革命:解鎖半導體行業(yè)的未來之門

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢

2035年Chiplet市場規(guī)模將超4110億美元

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺

國產(chǎn)半導體新希望:Chiplet技術(shù)助力“彎道超車”!

突破與解耦:Chiplet技術(shù)讓AMD實現(xiàn)高性能計算與服務(wù)器領(lǐng)域復興

Chiplet是什么新技術(shù)呢?

Chiplet是什么新技術(shù)呢?

評論