要了解定制為何如此重要,請考慮以下三個示例,其中可以使用參考設(shè)計作為起點,但設(shè)計人員可能希望對設(shè)計進(jìn)行更改,即使是在后期階段:

設(shè)計實現(xiàn)了通信堆棧的一部分(例如,USB 音頻),但音頻端的硬件接口可以定制為與特定類型的編解碼器(如 I2S 主或從 S/PDIF)進(jìn)行通信,也可以定制帶有一個額外的控制端點。

工業(yè)控制器實現(xiàn)許多標(biāo)準(zhǔn)協(xié)議之一;例如,工業(yè)電機(jī)供應(yīng)商可能希望包含以太網(wǎng) PHY,但推遲決定是否運行 EtherCAT 或任何其他實時以太網(wǎng)堆棧。

嵌入式 Web 服務(wù)器可用于配置上述任一示例,前提是設(shè)計人員可以在 Web 服務(wù)器內(nèi)部實現(xiàn)控制邏輯。

定制設(shè)計的難易程度取決于用于實現(xiàn)設(shè)計核心的技術(shù)。它使用了 ASIC、FPGA 還是實時處理器?

如果設(shè)計實現(xiàn)為 ASIC,那么定制它的唯一可行方法是修改 ASIC 中內(nèi)置的參數(shù)。考慮第一個示例,USB 音頻 ASIC 將具有設(shè)置 USB 設(shè)備產(chǎn)品名稱的方法,并可能提供左對齊和右對齊 I2S 之間的選擇。但是,它可能不提供添加額外控制端點或使用 S/PDIF 作為輸出接口的選項。事實上,開發(fā)支持所有合理接口的 ASIC 是不可能的,開發(fā)支持精心挑選的小型接口集的 ASIC 家族也不經(jīng)濟(jì)。

如果設(shè)計是在 FPGA 中實現(xiàn)的,那么理論上,定制可以像用戶想要的那樣極端。但是,硬件設(shè)計流程可能會使定制成為一個不那么簡單的過程。對于硬件設(shè)計人員來說,實現(xiàn)一個額外的接口(如 S/PDIF)并不困難,但實現(xiàn)一個額外的控制端點需要將軟件重新實現(xiàn)為一個硬件。此外,必須綜合結(jié)果,在定制設(shè)計完全綜合、布局和布線之前,尚不清楚是否仍能滿足原始時序約束。

第三種選擇是將設(shè)計完全實現(xiàn)為軟件。由于涉及許多相互沖突的實時要求,這通常被認(rèn)為難以完成。但是,只要程序員可以將問題分解為一組獨立的實時任務(wù),這些任務(wù)在一組獨立的實時處理器上運行,軟件實現(xiàn)就可以完美地管理。

這使設(shè)計人員能夠靈活地將硬件協(xié)議簡單地作為軟件任務(wù)來實現(xiàn),方法是專門使用一個實時處理器來實現(xiàn)該硬件協(xié)議。例如,可以通過以適當(dāng)?shù)姆绞綌[動時鐘和數(shù)據(jù)線,在軟件中實現(xiàn) I2S。此外,USB 可以通過向 USB PHY 讀取和寫入數(shù)據(jù)來實現(xiàn)。如果這兩個活動作為兩個獨立的任務(wù)執(zhí)行,那么所有的實時期限都可以單獨滿足。

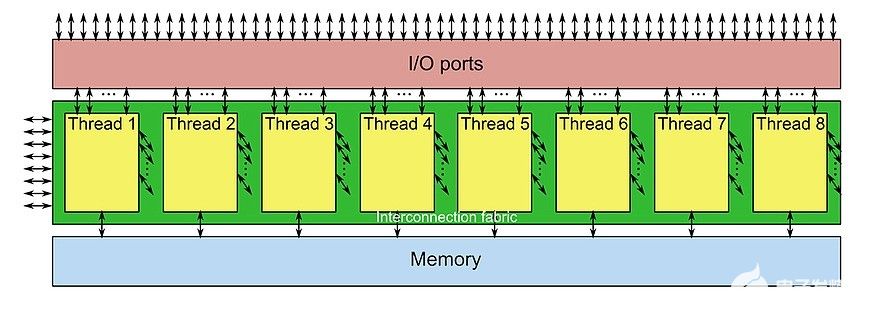

后者是一種稱為并發(fā)實時編程的編程模型。圖 1 顯示了單個 XMOS XCore 處理器如何同時執(zhí)行八個線程。每個線程都可以看作是一個獨立的處理器,具有保證的實時執(zhí)行率。每條指令將在已知的時間內(nèi)執(zhí)行;因此,程序員可以預(yù)測程序是否會滿足時間期限。

圖 1:并發(fā)實時編程同時執(zhí)行多個線程。

這個模型的美妙之處在于時間預(yù)測完全獨立于任務(wù)。例如,考慮前面提到的 I2S 任務(wù)。一旦程序以某種方式編寫,它將在例如 50 MIPS 處理器上執(zhí)行,那么無論對其他線程進(jìn)行修改,該 I2S 線程將始終滿足其時序。打破時間安排的唯一方法是不以適當(dāng)?shù)乃俾侍峁?shù)據(jù)。這是可以預(yù)料的;如果未提供 48 kHz 的數(shù)據(jù),則無法為編解碼器提供 48 kHz 的數(shù)據(jù),并且某些東西必須中斷。

軟件不是靈丹妙藥。兩個明顯的限制是需要太多瞬時帶寬的接口和需要非常短周轉(zhuǎn)時間的硬件接口。例如,在當(dāng)今的處理硬件上用軟件編寫多 GHz SERDES 是不可行的,但許多常見的接口可以用軟件來制定。

軟件實現(xiàn)優(yōu)于硬件接口的原因有以下三個:

1. 經(jīng)濟(jì)性:不可能提供所有可用的接口作為硬件塊。處理器可以根據(jù)需要對任何類型的接口進(jìn)行建模。

2、適應(yīng)性:在硅片上設(shè)置硬件內(nèi)置接口。如果標(biāo)準(zhǔn)不斷發(fā)展,或者如果特定設(shè)備不完全兼容或需要執(zhí)行一些額外的操作,那么硅接口將無法完成這項工作。可以調(diào)整軟件定義的接口以滿足要求。

3. 優(yōu)化:可以優(yōu)化軟件定義的界面來解決手頭的問題。考慮前面提到的 EtherCAT 應(yīng)用程序。如果使用硬件媒體獨立接口(MII),則數(shù)據(jù)包被存儲和轉(zhuǎn)發(fā),這不滿足例如延遲要求。如果接口是在軟件中定義的,那么緩沖需求可以針對問題進(jìn)行定制。

第三個原因很重要,因為許多處理 UART、I2S、MII 和其他標(biāo)準(zhǔn)的標(biāo)準(zhǔn)模塊必須具有內(nèi)置的 FIFO 緩沖區(qū)來解耦接口,而這些緩沖區(qū)在許多情況下是不需要的,因為它們會增加延遲。

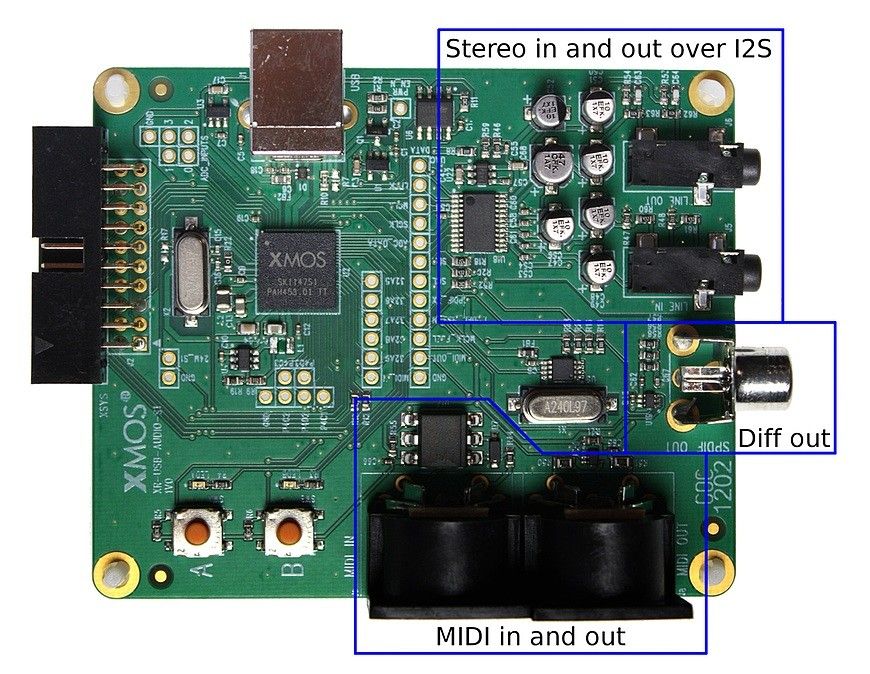

一旦設(shè)計師選擇了基于軟件的設(shè)計流程,可能性就無窮無盡。圖 2 顯示了一個 USB 板,它同時支持使用立體聲 I/O 編解碼器(通過 I2S)、差分?jǐn)?shù)字接口(使用 S/PDIF)和樂器數(shù)字接口 (MIDI) 的模擬接口。

圖 2:在 USB 板上,同一處理器只需更改軟件即可驅(qū)動任何混合接口。

嵌入式處理器實現(xiàn) USB 堆棧和 USB 音頻協(xié)議。在此特定配置中,驅(qū)動三個音頻接口:MIDI、I2S/模擬和 S/PDIF。后者可以僅通過軟件更改更改為不同的協(xié)議,例如 ADAT。更重要的是,產(chǎn)品的變化可以通過不同的接口集進(jìn)行,例如大量的同軸輸出或基于 I2S 的編解碼器。嵌入式處理器上的軟件只需稍作改動即可根據(jù)接口的具體情況進(jìn)行定制。每個接口沒有預(yù)定義的編號。

靈活的硬件可以實現(xiàn)更大的產(chǎn)品差異化,使開發(fā)人員和產(chǎn)品經(jīng)理能夠為他們的客戶提供與眾不同的價值。并發(fā)實時編程可以保證嚴(yán)格的時序要求,XMOS XCore 等嵌入式處理器提供了利用這種編程方法所需的芯片和開發(fā)工具。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19884瀏覽量

235018 -

解碼器

+關(guān)注

關(guān)注

9文章

1173瀏覽量

41949 -

嵌入式

+關(guān)注

關(guān)注

5149文章

19655瀏覽量

317294

發(fā)布評論請先 登錄

移動應(yīng)用高級語言開發(fā)——并發(fā)探索

嵌入式實時數(shù)據(jù)庫系統(tǒng)并發(fā)控制技術(shù)研究

嵌入式實時數(shù)據(jù)庫系統(tǒng)并發(fā)控制技術(shù)研究

負(fù)荷管理系統(tǒng)中的并發(fā)通信設(shè)計與實現(xiàn)

如何通過STM32的串口實現(xiàn)簡易脫機(jī)編程器

java并發(fā)編程實戰(zhàn)之輔助類用法

通過編程實現(xiàn)atoi函數(shù)的程序免費下載

通過并發(fā)實時編程實現(xiàn)定制

通過并發(fā)實時編程實現(xiàn)定制

評論