??在我之前寫的FPGA時序約束教程中,有一篇中講到了虛擬時鐘:

但文中對虛擬時鐘的應用介紹的還不夠詳細,因此這里我們再對虛擬時鐘做一個更加細致的介紹。

??首先,虛擬時鐘用于什么地方?

??虛擬時鐘通常用于設定輸入和輸出的延時,即set_input_delay和set_output_delay。可能有同學忘記這兩個約束的用法了,這里我們再展示一下:

set_input_delay0.5-clockclkA[get_portsA]

set_output_delay1-clockclkB[get_portsB]

其中clkA和clkB就是我們使用create_clock創建的主時鐘或者虛擬時鐘。

??主時鐘在創建的時候需要指定時鐘輸入端口,虛擬時鐘不需要指定端口,所以稱之為虛擬時鐘。那什么場景下要用到虛擬時鐘呢?

- 外部IO的參考時鐘并不是設計中的時鐘

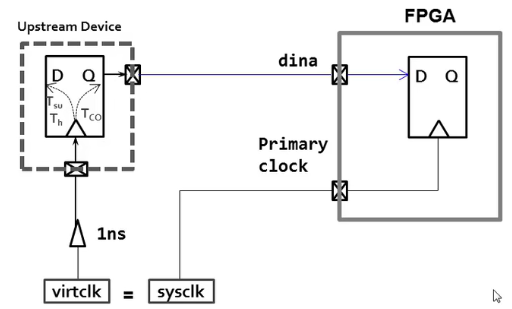

下圖中,外部IO的參考時鐘比設計中主時鐘的路徑上多了一個BUFFER,因此我們需要使用虛擬時鐘來進行約束。

create_clock-namesysclk-period10[get_portsclkin]

create_clock-namevirtclk-period10

set_clock_latency-source1[get_clockvirtclk]

set_input_delay-clockvirtclk-max4[get_portsdina]

set_input_delay-clockvirtclk-min2[get_portsdina]

- FPGA I/O路徑參考時鐘來源于內部衍生時鐘,但與主時鐘的頻率關系并不是整數倍

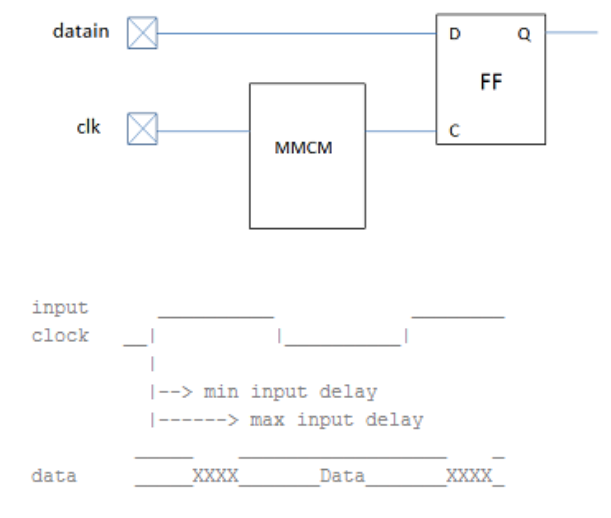

如果I/O路徑參考時鐘源于內部的衍生時鐘,那set_input_delay和set_output_delay約束中-clock參數后的時鐘不能是衍生時鐘,比如下圖的例子中,輸入10MHz時鐘經過了MMCM后去采輸入的數據。

image-20211206203529124

image-20211206203529124a) 如果MMCM沒有負的相移而且輸出的頻率也是10MHz,那么直接使用主時鐘來約束input delay。

create_clock-period100.000-nameclk[get_portsclk]

set_input_delay-clockclk-max2.000[get_portsdatain]

set_input_delay-clockclk-min1.000[get_portsdatain]

b) 如果MMCM輸出頻率是60MHz,那么這個衍生時鐘跟主時鐘并不是整數倍關系,這時就需要用到虛擬時鐘了

create_clock-period100.000-nameclk[get_portsclk]

create_clock-nameclk_port_vclk-period16.67

set_input_delay-clockclk_port_vclk-max2[get_portsdatain]

set_input_delay-clockclk_port_vclk-min1[get_portsdatain]

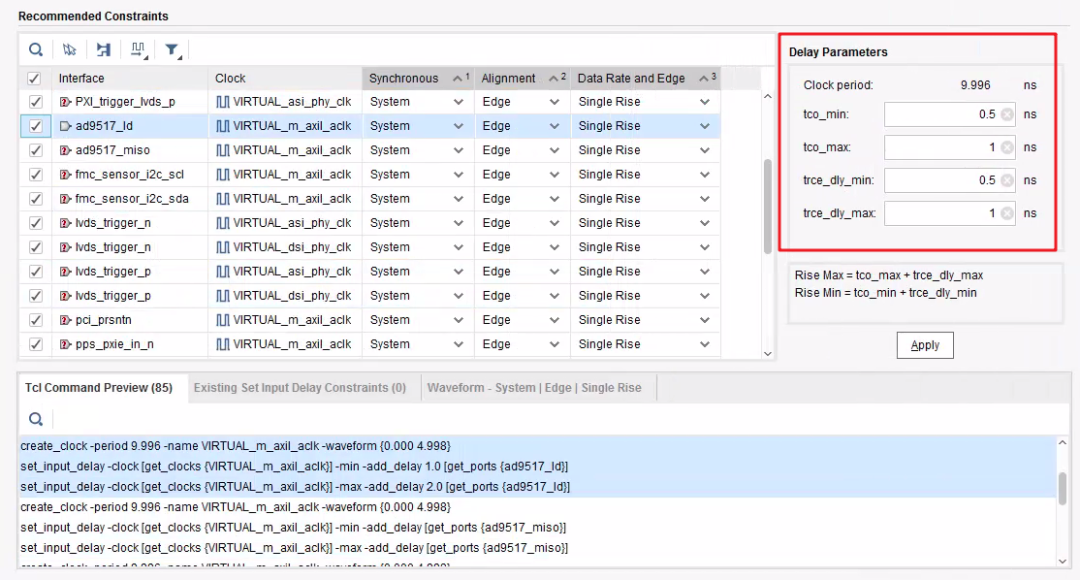

- 在不修改時鐘特性的情況下針對I/O指定不同的jitter和latency

這個需求我們可以在Constraints Wizards中指定,簡單又方便

image-20211206212729797

image-20211206212729797

在設置完成后,可以看到Tcl Command Preview中提示的約束指令。

審核編輯 :李倩

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618222 -

虛擬時鐘

+關注

關注

0文章

5瀏覽量

6654

原文標題:FPGA的虛擬時鐘如何使用?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA的虛擬時鐘用于什么地方?

FPGA的虛擬時鐘用于什么地方?

評論