在ASIC中用到鎖存器的地方很多,Time Borrowing是使用鎖存器的典型應(yīng)用之一,在深度流水線的設(shè)計中可以極大地提高處理性能。另外鎖存器和寄存器相比能夠顯著的減小面積:寄存器占用的硅片面積是鎖存器的兩倍,在ASIC設(shè)計中一個典型的主從寄存器是由兩個鎖存器級聯(lián)來實現(xiàn)的。

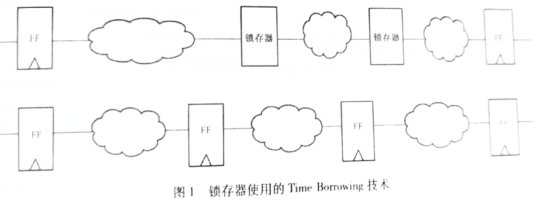

圖1說明了如何使用鎖存器的Time Borrowing技術(shù)來替代關(guān)鍵路徑中的寄存器。通過重新分配相鄰鎖存器之間的組合邏輯延遲,從而延長最長路徑的時鐘周期。

對于Xilinx的 FPGA芯片來說,不管是鎖存器還是寄存器,都是用相同的硬件資源實現(xiàn)的。這些硬件資源共享相同的數(shù)據(jù)輸入/輸出、復(fù)位和使能信號,可以配置成邊沿觸發(fā)的寄存器或者電平使能的鎖存器。因此在 FPGA芯片中,無論是鎖存器還是寄存器都使用相同的硬件資源,使用鎖存器并不會帶來任何的優(yōu)勢。

寄存器和鎖存器關(guān)于數(shù)據(jù)的存儲方面存在著根本的差異。鎖存器屬于電平敏感電路,當(dāng)門使能信號有效時,輸入數(shù)據(jù)將直接輸出;而門使能信號無效時,數(shù)據(jù)保持到鎖存器中。寄存器屬于邊沿敏感電路,數(shù)據(jù)只有在時鐘的上升沿或者下降沿才會被保存到寄存器中。

雖然鎖存器和寄存器使用相同的FPGA硬件資源,但還是要盡量避免使用前者。首先,當(dāng)鎖存器處于導(dǎo)通狀態(tài)時,輸入信號的毛刺會直接傳遞到后面的邏輯中;另外,對于靜態(tài)時序分析工具來說、分析寄存器遠(yuǎn)遠(yuǎn)比鎖存器簡單得多。因為對于寄存器而言,只考慮到時鐘的上升或者下降沿:對于鎖存器而言,不僅需要考慮其上升沿和下降沿,而且還要考慮上、下沿之間的持續(xù)時間。對于具有周期性抖動的信號而言,鎖存器常常會造成問題。而對于邊沿敏感的寄存器,由于只需要關(guān)心時鐘邊沿的達(dá)到時間,因此即便是門使能的信號具有周期抖動,也不會造成任何的問題。ASIC設(shè)計中鎖存器的Time Borrowing電路,對于FPGA結(jié)構(gòu)來講更是難以回避的挑戰(zhàn)。由于某級流水線的延遲和前面所有流水線的延遲相關(guān),這種流水線的高度相關(guān)性將使得靜態(tài)時序分析更加難以處理,并且其困難程度和流水線的級數(shù)也不存在任何的線性關(guān)系。

正是因為上述原因,基于鎖存器的設(shè)計需要更加仔細(xì)和周密的時序約束。對于基于鎖存器流水線的邏輯綜合和物理實現(xiàn),更是要從整個芯片的角度去做分析,才能夠正確地約束不同的時序關(guān)系。

因此在將ASIC 設(shè)計移植到FPGA時,最好就是將電平使能的鎖存器轉(zhuǎn)換為邊沿觸發(fā)的寄存器。這需要工程師投人許多的時間去分析和修改,因為不是所有描述鎖存器的代碼風(fēng)格都能夠通過同樣的方式進(jìn)行轉(zhuǎn)換。

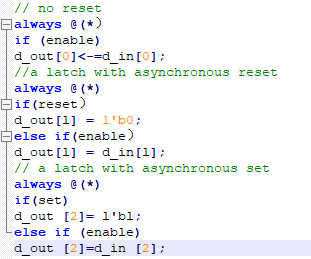

大多數(shù)商用綜合工具都支持鎖存器的設(shè)計,代碼中的if語句如果缺少相應(yīng)的case語句,將自動生成鎖存器。

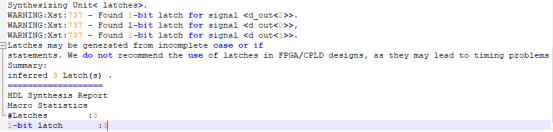

當(dāng)Xilinx的綜合工具XST 遇到鎖存器之后,會產(chǎn)生以下類似的報告。

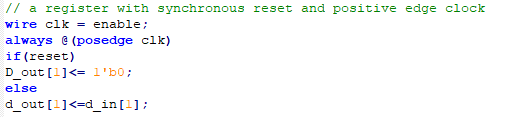

通過修改成綜合工具所支持的代碼風(fēng)格,可以將鎖存器轉(zhuǎn)換成寄存器。下面通過一個簡單的例子展示了其中的一種代碼風(fēng)格,可以將門使能信號轉(zhuǎn)換成時鐘信號。

當(dāng)然也有其他一些代碼風(fēng)格,比如時鐘可以使用上升沿或者下降沿(Xilinx的FPGA不支持雙時鐘沿)、同步或者異步的復(fù)位置位等。

原文標(biāo)題:FPGA知識匯集-鎖存器的移植

文章出處:【微信公眾號:FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1645文章

22040瀏覽量

618203 -

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124418 -

鎖存器

+關(guān)注

關(guān)注

8文章

925瀏覽量

42362

原文標(biāo)題:FPGA知識匯集-鎖存器的移植

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

鎖存器、觸發(fā)器、寄存器和緩沖器的區(qū)別

觸發(fā)器、鎖存器、寄存器三者的區(qū)別

【轉(zhuǎn)】數(shù)字電路三劍客:鎖存器、觸發(fā)器和寄存器

關(guān)于鎖存器的time borrowing概念

鎖存器、觸發(fā)器、寄存器的關(guān)聯(lián)與區(qū)別及其相應(yīng)的verilog描述

一文詳細(xì)區(qū)分寄存器、鎖存器和觸發(fā)器

什么是鎖存器 與寄存器有何區(qū)別

具有3態(tài)輸出的8位鎖存寄存器收發(fā)數(shù)據(jù)表

帶輸入鎖存器的8位移位寄存器數(shù)據(jù)表

如何使用鎖存器的Time Borrowing技術(shù)來替代關(guān)鍵路徑中的寄存器

如何使用鎖存器的Time Borrowing技術(shù)來替代關(guān)鍵路徑中的寄存器

評論